## Circuit Modeling with Hardware Description Languages

### Prof. Hubert Kaeslin Microelectronics Design Center ETH Zürich

Morgan Kaufmann "Top-Down Digital VLSI Design" Chapter 4

last update: July 18, 2014

## Content

### You will learn

to write high-quality HDL models for circuit synthesis and simulation.

- Why hardware synthesis?

- Key concepts behind hardware description languages

- What sets HDLs apart from a programming language

- Essential VHDL and/or SystemVerilog language constructs

- Putting HDLs to service for hardware synthesis

- Synthesis subset

- Patterns for registers and finite state machines

- Timing constraints

- How to establish a register transfer level model

- VHDL versus SystemVerilog

Simulation and testbench coding are postponed to chapter 5 "Functional Verification".

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions

Subject

Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

# Motivation and background

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

### Why hardware synthesis?

Current situation for VLSI designers:

- Buyers ask for more and more functions on a single chip.

- Technology supports ever higher integration densities (Moore's law).

- Market pressure vetoes dilation of development times.

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

## Why hardware synthesis?

Current situation for VLSI designers:

- Buyers ask for more and more functions on a single chip.

- Technology supports ever higher integration densities (Moore's law).

- Market pressure vetoes dilation of development times.

Hardware description languages (HDL) and design automation come to the rescue in four ways:

- Move design entry to higher levels of abstraction.

- Allow designers to focus on functionality as synthesis tools automate the construction of structural and physical views.

- ► Facilitate reuse by capturing a circuit description in a parametrized, technology- and platform-independent form.

- Make functional verification more efficient by supporting stimuli generation, automatic response checking, assertion-based verification, etc.

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

### Languages for modeling digital hardware I

| VHDL    | An HDL that not only supports structural and behavioral circuit   |  |  |  |

|---------|-------------------------------------------------------------------|--|--|--|

|         | models but testbench models too. A subset is synthesizable.       |  |  |  |

|         | Syntactically similar to Ada.                                     |  |  |  |

| Verilog | Conceptually similar to VHDL, no type checking and more limited   |  |  |  |

|         | capabilities for design abstraction. A subset is synthesizable.   |  |  |  |

|         | Syntactically similar to C. Superseded by                         |  |  |  |

| System- | A superset of Verilog that includes many advanced features from   |  |  |  |

| Verilog | VHDL and from specialized verification languages (OpenVera, PLS). |  |  |  |

|         | A subset is synthesizable. Supports object-oriented programming.  |  |  |  |

| SystemC | Extends C++ with class libraries and a simulation kernel.         |  |  |  |

|         | Adds clocking information to C++ functions.                       |  |  |  |

|         | Intended for software/hardware co-design and co-simulation.       |  |  |  |

|         | Does not support any timing finer than one clock cycle.           |  |  |  |

|         | Synthesis path is via translation to RTL VHDL or Verilog.         |  |  |  |

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

### Languages for modeling digital hardware II

| Criterion                                                                                                                                     | VHDL                              | Verilog                                | SystemVerilog                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------|-----------------------------------------|

| Synthesis support                                                                                                                             | yes                               | yes                                    | growing                                 |

| Parametrization & abstract modeling                                                                                                           | good                              | poor                                   | good                                    |

| Type checking & scoping rules                                                                                                                 | strong                            | none                                   | loose                                   |

| Deterministic event queue mechanism                                                                                                           | yes                               | not really                             | not really                              |

| Modeling of electric phenomena                                                                                                                | 9-valued                          | 4-valued                               | 4-valued                                |

| High-level verification support                                                                                                               | limited                           | poor                                   | excellent                               |

| Parametrization & abstract modeling<br>Type checking & scoping rules<br>Deterministic event queue mechanism<br>Modeling of electric phenomena | good<br>strong<br>yes<br>9-valued | poor<br>none<br>not really<br>4-valued | good<br>loose<br>not really<br>4-valued |

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

### Languages for modeling digital hardware II

| Criterion                           | VHDL     | Verilog    | SystemVerilog |

|-------------------------------------|----------|------------|---------------|

| Synthesis support                   | yes      | yes        | growing       |

| Parametrization & abstract modeling | good     | poor       | good          |

| Type checking & scoping rules       | strong   | none       | loose         |

| Deterministic event queue mechanism | yes      | not really | not really    |

| Modeling of electric phenomena      | 9-valued | 4-valued   | 4-valued      |

| High-level verification support     | limited  | poor       | excellent     |

For me, I find VHDL is like swimming with a lifeguard on duty, whereas Verilog is like swimming with a lifebuoy hanging by the poolside. (Blogger on EETimes 2011)

- Many companies currently use VHDL for synthesis and SystemVerilog for system-level verification.

- Will SystemVerilog one day supersede Verilog and VHDL, and reconcile their user communities?

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

## The genesis of VHDL

- 1983 US DoD commissions IBM, Intermetrics and Texas Instruments to define a HDL for documentation purposes. Ada is taken as a starting point. There are no plans for automatic synthesis.

- 1986 Military restrictions lifted, rights transferred to IEEE.

- 1987 Language accepted as IEEE 1076 standard. Event-based simulation tools begin to appear.

- 1993 Language standard significantly revised to become IEEE 1076-93. Nine-valued logic system accepted as IEEE 1164 standard. Though confined to a language subset, synthesis begins to catch on.

- 1999 A major extension towards modeling of analog and mixed-signal circuits is accepted as separate a standard IEEE 1076.1.

- 2002 Standard slightly revised to become IEEE 1076-2002.

- 2008 IEEE 1076-2008 brings enhanced generics, source code encryption, embedding of IEEE 1850 Property Specification Language, and more.

Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

## The genesis of SystemVerilog

1984 Gateway Design Autom. develops Verilog for a proprietary logic simulator.

- 1989 Gateway acquired by Cadence.

- 1990 Verilog made an open standard.

- 1995 Verilog accepted as IEEE 1364 standard. (questionable politics involved)

- 2001 IEEE 1364-2001 brings major extensions for circuit modeling.

2005 IEEE 1364-2005 is a minor revision.

SystemVerilog, created by the Accellera consortium, is accepted as a separate standard named IEEE 1800. (more politics involved)

Quiz: "What do Sausage and EDA Standards have in common?"

Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

## The genesis of SystemVerilog

1984 Gateway Design Autom. develops Verilog for a proprietary logic simulator.

- 1989 Gateway acquired by Cadence.

- 1990 Verilog made an open standard.

- 1995 Verilog accepted as IEEE 1364 standard. (questionable politics involved)

- 2001 IEEE 1364-2001 brings major extensions for circuit modeling.

2005 IEEE 1364-2005 is a minor revision.

SystemVerilog, created by the Accellera consortium, is accepted as a separate standard named IEEE 1800. (more politics involved)

Quiz: "What do Sausage and EDA Standards have in common?" Answer: "Those who like sausage or EDA standards should never watch either one be made!" (Stuart Sutherland).

# 2009 IEEE 1800-2009 standard brings improvements mostly for verification, Verilog gets absorbed into the SystemVerilog standard.

2013 IEEE 1800-2012 version released.

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

## Why bother learning hardware description languages? I

Idea: View HDLs as nothing more than intermediate formats for exchanging data between system design tools and VLSI CAE/CAD suites. Have electronic system-level tools generate code from specs automatically.

Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

## Why bother learning hardware description languages? I

Idea: View HDLs as nothing more than intermediate formats for exchanging data between system design tools and VLSI CAE/CAD suites. Have electronic system-level tools generate code from specs automatically.

riangle Software for system design has a focus, there is no universal tool.

- Transformatorial systems as found in signal processing and telecommunications.

- Reactive system as found in controllers and interface protocols.

- Specific applications such as data networks, image processing, instruction set computers, etc.

- HDL generators typically restricted to few predefined architectural patterns.

- $\triangle$  HDL code generated by most ESL tools is nothing else than a translation of software code and inadequate for circuit synthesis.

- $\bigtriangleup$  HDLs are indispensable for modeling library cells and virtual components.

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

### Why bother learning hardware description languages? II

$\bigtriangleup\,$  HDLs are being used all along digital VLSI design flows.

| Des     | ign stage      | Main             | Level of    |                      | Predominant  |

|---------|----------------|------------------|-------------|----------------------|--------------|

| & model |                | purpose          | abstraction | Timing               | languages    |

| 1.      | Algorithmic    | system-level     | behavioral  | none                 | C, Matlab    |

|         | model          | simulation       |             | tentative            | VHDL, SysVer |

| 2.      | RTL            | simulation       | register    | optional fake delays | VHDL, SysVer |

|         | model          | synthesis        | transfer    | constraints in Tcl   |              |

| 3.      | Post-synthesis | simulation,      | gate level  | estimated with       | Verilog,     |

|         | netlist        | timing analysis, |             | wire load models     | (VHDL&VITAL) |

|         |                | place & route    |             |                      |              |

| 4.      | Post-layout    | simulation,      | gate level  | extracted from       | Verilog,     |

|         | netlist        | timing analysis, |             | layout and           | (VHDL&VITAL) |

|         |                | sign-off         |             | back-annotated       |              |

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware **Why bother learning hardware description languages?** A first look at VHDL and SystemVerilog

### Why bother learning hardware description languages? II

$\bigtriangleup\,$  HDLs are being used all along digital VLSI design flows.

| Design stage |                | Main             | Level of    |                      | Predominant  |

|--------------|----------------|------------------|-------------|----------------------|--------------|

| & model      |                | purpose          | abstraction | Timing               | languages    |

| 1.           | Algorithmic    | system-level     | behavioral  | none                 | C, Matlab    |

|              | model          | simulation       |             | tentative            | VHDL, SysVer |

| 2.           | RTL            | simulation       | register    | optional fake delays | VHDL, SysVer |

|              | model          | synthesis        | transfer    | constraints in Tcl   |              |

| 3.           | Post-synthesis | simulation,      | gate level  | estimated with       | Verilog,     |

|              | netlist        | timing analysis, |             | wire load models     | (VHDL&VITAL) |

|              |                | place & route    |             |                      |              |

| 4.           | Post-layout    | simulation,      | gate level  | extracted from       | Verilog,     |

|              | netlist        | timing analysis, |             | layout and           | (VHDL&VITAL) |

|              |                | sign-off         |             | back-annotated       |              |

### Conclusion

For the foreseeable future, VHDL and SystemVerilog are bound to remain prominent hubs for all VLSI design activities.

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

## Requirements for HDLs

Show around a motherboard or some other mounted PCB.

What features must a formal language have to capture the essence of electronic circuitry?

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

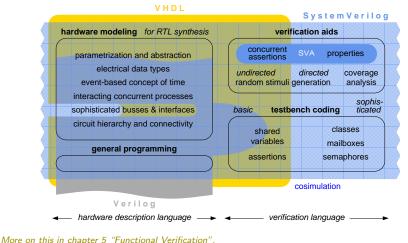

## A first look at VHDL and SystemVerilog

In a nutshell, HDLs can be characterized as follows:

- HDL = Structured programming language

- + circuit hierarchy and connectivity

- + interacting concurrent processes

- + a discrete replacement for electrical signals

- + an event-driven scheme of execution

- + model parametrization facilities

- + verification aids

Chapter 5

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

## A first look at VHDL and SystemVerilog

In a nutshell, HDLs can be characterized as follows:

- $\mathsf{HDL} \quad = \quad \mathsf{Structured} \ \mathsf{programming} \ \mathsf{language}$

- + circuit hierarchy and connectivity

- + interacting concurrent processes

- + a discrete replacement for electrical signals

- + an event-driven scheme of execution

- + model parametrization facilities

- + verification aids

Limitation:

• No way to express timing constraints

Chapter 5

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

### Two words of caution ...

### Linguistic ambiguity in the context of hardware modeling:

| Meaning of "sequential"<br>with reference to                | Synonym      | Antonyms                     |

|-------------------------------------------------------------|--------------|------------------------------|

| <ul> <li>program execution<br/>during simulation</li> </ul> | step-by-step | concurrent,<br>parallel      |

| <ul> <li>nature of circuit<br/>being modeled</li> </ul>     | memorizing   | combinational,<br>memoryless |

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

### ... before we go into the details

Teaching follows two threads:

Lab hours Become acquainted with software tools and acquire coding skills.

Lectures Understand the underlying concepts and mechanisms.

- modeling of electrical phenomena

- simulation cycle

- testbench design

- synthesis procedure

- handling of macrocells (RAM)

- delay modeling, timing checks, timing constraints

- ► code portability

...

Key concepts and constructs of VHDL Key concepts and constructs of SystemVerilog Automatic circuit synthesis from HDL models Conclusions Why hardware synthesis? Alternatives for modeling digital hardware Why bother learning hardware description languages? A first look at VHDL and SystemVerilog

15/227

### ... before we go into the details

Teaching follows two threads:

Lab hours Become acquainted with software tools and acquire coding skills.

Lectures Understand the underlying concepts and mechanisms.

- modeling of electrical phenomena

- simulation cycle

- testbench design

- synthesis procedure

- handling of macrocells (RAM)

- delay modeling, timing checks, timing constraints

- ► code portability

► ...

Both are needed! Circuit design is neither pure theory nor ignorant hacking.

### A fool with a tool is still a fool.

Lircuit hierarchy and connectivity interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

# Key concepts and constructs of VHDL

For a SystemVerilog course, skip the next 95 or so slides.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization

### Hardware description language requirements

HDL requirement no.1

Means for expressing how circuits are being composed from subcircuits and how those subcircuits connect to each other.

Circuit hierarchy and connectivity

Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming language:

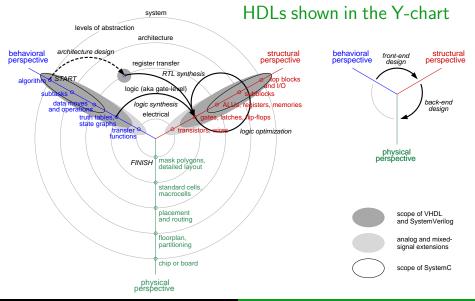

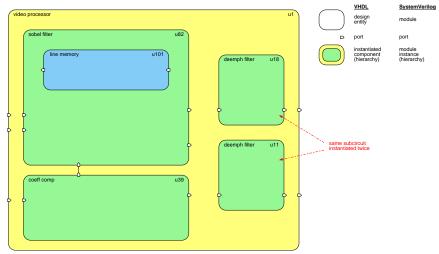

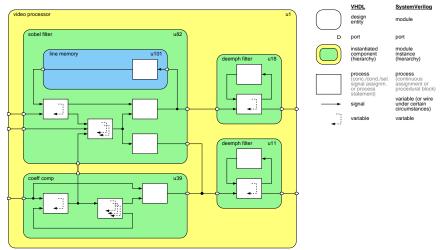

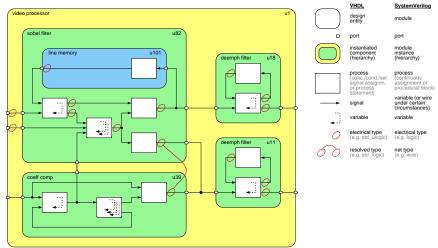

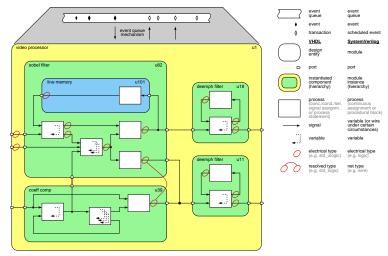

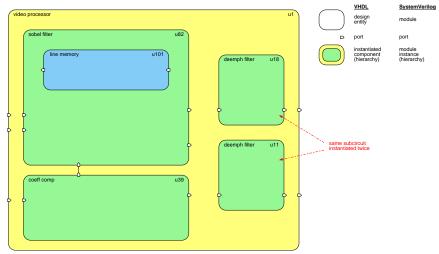

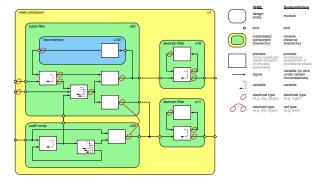

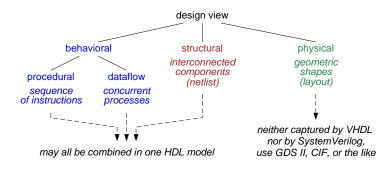

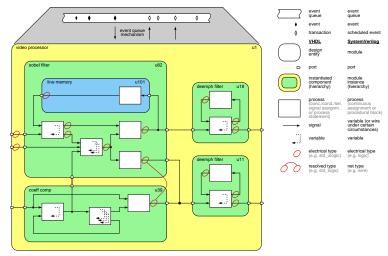

### 1st HDL capability: Circuit hierarchy and connectivity

Figure: Hierarchical composition ...

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

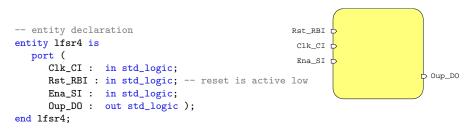

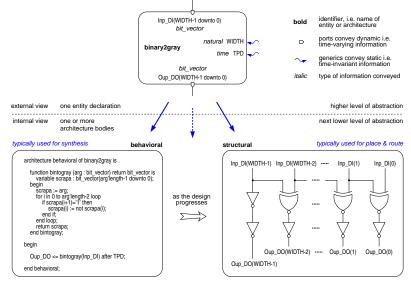

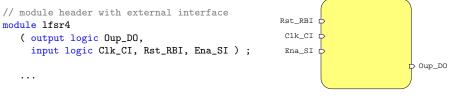

### Entity declaration

Specifies the external interface of a design entity (small or large).

A port list declares all signals of an entity that are accessible from outside (i.e. the terminals of a circuit as opposed to its inner nodes).

Circuit hierarchy and connectivity

Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

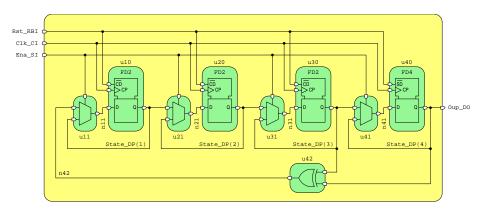

### Architecture body I: a structural circuit model

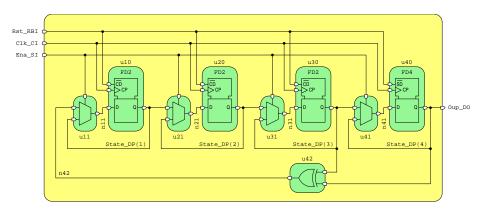

Figure: Linear-feedback shift register circuit to be described.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Architecture body I: a structural circuit model

Refer to transparency lfsr4struc.vhd for code!

Describes a circuit or netlist assembled from components and wires.

- 1. Declare all components to be used.

- 2. Declare all signals that run back and forth unless they are already known from the port clause.

- 3. Instantiate components specifying all terminal-to-signal connections.

Circuit hierarchy ad connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

22 / 227

### How to compose a circuit from components

How do you proceed when asked to fit a circuit board with components?

- 1. Think of a part's exact name, e.g. GTECH\_FD2

- 2. Fetch a copy and assign it some unique identifier it, e.g. u10

- 3. Solder its terminals to existing metal pads on the board

The component instantiation statement does exactly that. Example:

```

u10 : GTECH_FD2

port map( D => n11,

CP => Clk_CI,

CD => Rst_RBI,

Q => State_DP(1) );

```

### Note

The association operator => does not indicate an assignment but an association of two signals that stands for an electrical connection.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### The essence of structural circuit modeling

- VHDL can describe the hierarchical composition of a circuit by

- instantiating components or entities and by

- interconnecting them with the aid of signals.

- Structural HDL models hold the same information as circuit netlists do.

- Manually writing structural HDL models is not particularly attractive.

- Most structural models are in fact obtained from RTL models by automatic synthesis.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### The essence of <u>structural</u> circuit modeling

- VHDL can describe the hierarchical composition of a circuit by

- instantiating components or entities and by

- interconnecting them with the aid of signals.

- Structural HDL models hold the same information as circuit netlists do.

- Manually writing structural HDL models is not particularly attractive.

- Most structural models are in fact obtained from RTL models by automatic synthesis.

### HDL requirement no.2

Means for expressing circuit behavior including the combined effects of multiple subcircuits that operate jointly and concurrently.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

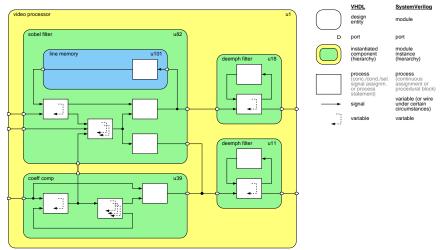

### 2nd HDL capability: Interacting concurrent processes

Figure: ... plus behavior modeled with the aid of concurrent processes ...

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Constants, variables, and signals

What everyone knows from software languages:

- Constant declaration

Example constant FERMAT\_PRIME\_4 : integer := 65537;

- Variable declaration Examples

variable Brd : real := 2.48678E5; variable Ddr : real := 1.08179E5;

Variable assignment Example

Brd := Brd + Ddr;

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Constants, variables, and signals

What everyone knows from software languages:

- Constant declaration

Example constant FERMAT\_PRIME\_4 : integer := 65537;

- > Variable declaration

Examples variable Brd : real := 2.48678E5;

- variable Ddr : real := 1.08179E5;

Variable assignment Example Brd := Brd + Ddr;

- ... plus a special vehicle for exchanging information between processes:

- Signal declaration

Example signal Error\_D, Actual\_D, Wanted\_D : integer := 0;

- > Signal assignment. Example Error\_D <= Actual\_D - Wanted\_D;</pre>

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Practical advice

### Hints

- ► VHDL is case-insensitive, e.g. clk\_ci = CLK\_CI (except for extended identifiers written between backslashes, e.g. \clk\_ci \ ≠ \CLK\_CI \).

- ▶ Naming a signal or a port In or Out is all too tempting, yet these are reserved words in VHDL. We recommend Inp and Oup instead.

- Two distinct symbols are being used for variable assignment := and for signal assignment <= .</p>

- Code is easier to read when signals can be told from variables by their visual appearance. We append an underscore followed by a suffix of upper-case letters to signals, e.g. Carry\_DB, AddrCnt\_SN, Irq\_AMI.

Details of our naming convention are to follow in chapter 6 "The Case for Synchronous Design".

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## How to describe combinational logic behaviorally I

- 1. Concurrent signal assignment:

- Syntactically simplest form of a process.

- Drives one signal.

### Example:

signal Aa\_D, Bb\_D, Cc\_D, Oup\_D : std\_logic; .....

```

Oup_D <= Aa_D xor (Bb_D and not Cc_D)</pre>

```

Typically used to model some combinational behavior (such as an arithmetic or logic operation) when there is no need for branching.

Glimpse ahead: A concurrent/selected/conditional signal assignment gets activated by any change of any signal on the right-hand side.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## How to describe combinational logic behaviorally II

#### 2. Selected signal assignment. Example:

. . . . .

with ThisMonth\_D select

ThisQuarter\_D <= Q1ST when JANUARY | FEBRUARY | MARCH,

Q2ND when APRIL | MAY | JUNE,

Q3RD when JULY | AUGUST | SEPTEMBER,

Q4TH when others;</pre>

> This is a form of conditional execution reminiscent of a multiplexer.

Note: The | symbol separates choices, it does not express a logic or operation.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## How to describe combinational logic behaviorally III

#### 3. Conditional signal assignment. Example:

```

subtype day is integer range 1 to 31;

signal ThisDay_D is day;

signal Spring_D is boolean;

.....

```

```

Spring_D <= true when (ThisMonth_D=MARCH and ThisDay_D>=21) or

ThisMonth_D=APRIL or ThisMonth_D=MAY or

(ThisMonth_D=JUNE and ThisDay_D<=20)

else false;

```

#### This is a syntactically different form of conditional execution.

Note: There are two <= symbols here. One stands for a signal assignment, the other for a comparison operator.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## How to describe combinational logic behaviorally IV

4. Process statement.

Example:

```

memless1: process (all)

begin

Spring_D <= false; -- execution begins here

if ThisMonth_D=MARCH and ThisDay_D>=21 then Spring_D <= true; end if;

if ThisMonth_D=APRIL then Spring_D <= true; end if;

if ThisMonth_D=MAY then Spring_D <= true; end if;

if ThisMonth_D=JUNE and ThisDay_D<=20 then Spring_D <= true; end if;

end process memless1; -- process suspends here</pre>

```

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Process statement versus signal assignments

When compared to a concurrent/selected/conditional signal assignment, a process statement

- is capable of updating two or more signals at a time,

- captures the instructions for doing so in a sequence of statements that may not only include branching but also loops,

- gives the liberty to make use of variables for temporary storage,

- provides more detailed control over the conditions for activation.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Process statement versus signal assignments

When compared to a concurrent/selected/conditional signal assignment, a process statement

- is capable of updating two or more signals at a time,

- captures the instructions for doing so in a sequence of statements that may not only include branching but also loops,

- gives the liberty to make use of variables for temporary storage,

- provides more detailed control over the conditions for activation.

#### Observation

The process statement is best summed up as being concurrent outside and sequential inside.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

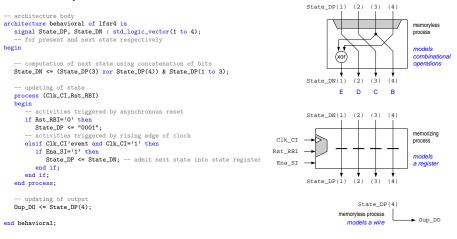

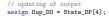

## How to describe a register behaviorally

- Code example of an edge-triggered register that features

- 1. an asynchronous reset,

- 2. a synchronous load, and

- 3. an enable.

```

p_memzing : process (Clk_C,Rst_RB)

begin

-- activities triggered by asynchronous reset

if Rst_RB='0' then

State DP <= (others => '0'): -- shorthand for all bits zero

-- activities triggered by rising edge of clock

elsif Clk_C'event and Clk_C='1' then

-- when synchronous load is asserted

if Lod_S='1' then

State_DP <= (others => '1'); -- shorthand for all bits one

-- else assume new value iff enable is asserted

elsif Ena_S='1' then

State_DP <= State_DN; -- admit next state into state register</pre>

end if:

end if:

end process p_memzing;

```

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Architecture body II: a behavioral circuit model

## Describes how concurrent processes interact via signals and how they alter them.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## The essence of <u>behavioral</u> circuit modeling

In VHDL, the behavior of a digital circuit typically gets described by a collection of concurrent processes that

- execute simultaneously, that

- communicate via signals, and where

- each such process represents some subfunction.

#### Hint for RTL synthesis

- Model each register with a process statement.

- Prefer concurrent, selected, and conditional signal assignments for describing the combinational logic in between.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

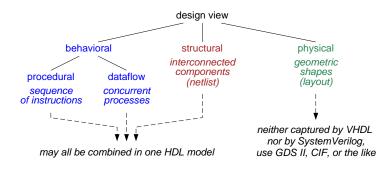

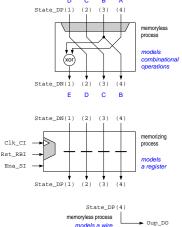

## Hardware modeling styles

#### Observation

VHDL allows for procedural, dataflow, and structural modeling styles to be freely combined in a single model.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

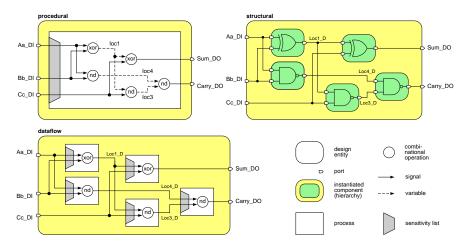

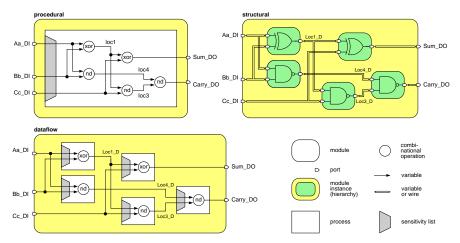

## Procedural, dataflow, and structural models compared I

Refer to transparency fulladd.vhd for code!

Compare in terms of

- 1. number of processes

- 2. number of internal signals

- 3. number of variables

- 4. impact of ordering of statements

- 5. interaction with event queue

- 6. portability of source code

Note: Adders are normally synthesized from algebraic expressions, a full-adder has been chosen here for its simplicity and obviousness.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Procedural, dataflow, and structural models compared II

Figure: Modeling styles illustrated with a full adder as example.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Example: The ones counter

Refer to transparency onescnt.vhd for code!

#### Observe

- 1. In spite of its name, this is a memoryless subfunction that finds applications in large adder circuits.

- 2. The output is a 3 bit number that indicates how many of the four input bits are 1 (logic high).

- 3. The great diversity of modeling styles to express exactly the same functionality.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Example: The ones counter

Refer to transparency onescnt.vhd for code!

#### Observe

- 1. In spite of its name, this is a memoryless subfunction that finds applications in large adder circuits.

- 2. The output is a 3 bit number that indicates how many of the four input bits are 1 (logic high).

- 3. The great diversity of modeling styles to express exactly the same functionality.

#### Observation

Some code examples are compact and easy to understand, others are more cryptic or tend to grow exponentially.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

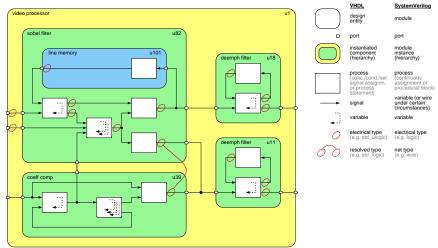

## 3rd capabilitity: A discrete replacement for electrical signals

Figure: ... plus data types for modeling electrical phenomena ...

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

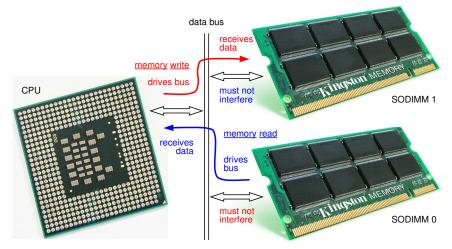

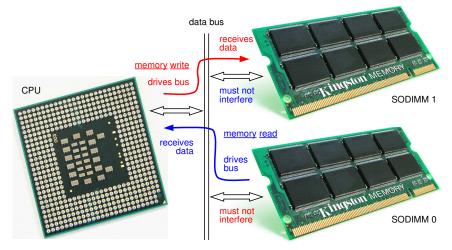

## What you ought to know about bidirectional busses I

Figure: Memory read and write transfers in a computer.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## What you ought to know about bidirectional busses II

Requirements:

- Each bidirectional line is to be driven from multiple places, so one needs a multi-driver signal (as opposed to a single-driver signal).

- Driving alternates.

- Buffers must be able to electrically release the line hence the name "three-state" output (0, 1, disabled output = high-impedance state).

- Requires some kind of access control mechanism (centralized or distributed).

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## What you ought to know about bidirectional busses II

Requirements:

- Each bidirectional line is to be driven from multiple places, so one needs a multi-driver signal (as opposed to a single-driver signal).

- Driving alternates.

- Buffers must be able to electrically release the line hence the name "three-state" output (0, 1, disabled output = high-impedance state).

- Requires some kind of access control mechanism (centralized or distributed).

Failure modes:

- ► Stationary drive conflict → functional failure or damage.

- Floating voltage  $\mapsto$  electrically undesirable condition.

Presentation focusses on HDL modeling, remedies to be discussed in chapter 10 "Gate- and Transistor-Level Design".

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

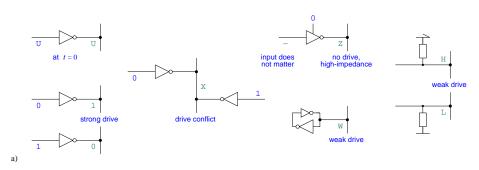

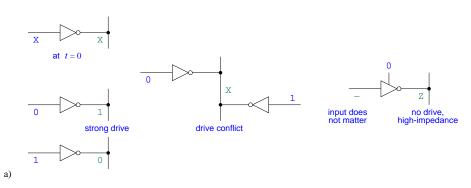

## Why do binary types not suffice to model digital circuits?

Digital circuits exhibit characteristics and phenomena such as

- transients,

- three-state outputs,

- drive conflicts, and

- power-up

that can not be modeled with 0 and 1 alone.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Why do binary types not suffice to model digital circuits?

Digital circuits exhibit characteristics and phenomena such as

- transients,

- three-state outputs,

- drive conflicts, and

- power-up

that can not be modeled with 0 and 1 alone.

#### HDL requirement no.3

A multi-valued logic system capable of capturing the effects of both node voltage and source impedance.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## The IEEE 1164 logic system I

#### Voltage is quantized into three logic states

- $\circ$  low logic low, that is below  $U_l$ .

- $\circ$  high logic high, that is above  $U_h$ .

- unknown either "low", "high" or anything in between

- e.g. as a result from a short between two drivers.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## The IEEE 1164 logic system I

# Voltage is quantized into three logic states $\circ$ low $\circ$ high $\circ$ high $\circ$ unknowneither "low", "high" or anything in between

e.g. as a result from a short between two drivers.

Source impedance gets mapped onto three drive strengths

- $\circ$  strong  $% \left( {\left| {{{\rm{sc}}} \right|_{\rm{sc}}} \right)$  as exhibited by a driving output

- $\circ$  high-impedance as exhibited by a disabled three-state output

- weak somewhere between "strong" and "high-impedance"

e.g. as exhibited by a passive pull-up/down resistor.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## The IEEE 1164 logic system II

No charge retention in high-impedance state  $\rightsquigarrow$

- charged low

- charged high

- charged unknown

are all merged into a single value of undetermined state (voltage).

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## The IEEE 1164 logic system II

No charge retention in high-impedance state  $\rightsquigarrow$

- charged low

- charged high

- charged unknown

are all merged into a single value of undetermined state (voltage).

Two extra logic values are added, namely: • uninitialized signal has never been assigned any value since power-up (applicable to simulation only). • don't care don't care condition for logic minimization, distinction between "low" or "high" immaterial (applicable to synthesis only).

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## The IEEE 1164 logic system III

Uses a total of nine logic values to model electrical signals.

| logic valu  | $e \rightarrow$ | logic state |         |      |  |

|-------------|-----------------|-------------|---------|------|--|

| ↓           |                 | low         | unknown | high |  |

| uninitializ | ized U          |             |         |      |  |

|             | strong          | 0           | Х       | 1    |  |

| strength    | weak            | L           | W       | Н    |  |

|             | high-impedance  | Z           | Z       | Z    |  |

| don't care  |                 |             | -       |      |  |

Defines two data types that share the above set of values:

| $\circ \texttt{std}\_\texttt{ulogic}$ | type    | Difference to be |

|---------------------------------------|---------|------------------|

| $\circ$ std_logic                     | subtype | explained soon   |

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Illustrations

Figure: The IEEE 1164 standard MVL-9 illustrated.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Collapsing of logic values during synthesis

L and H are not normally honored by synthesis software. Most synthesis tools collapse "meaningless" (to them) values to more sensible ones, e.g.

- ▶ L → 0

- ▶ H → 1

- X or  $W \mapsto$  -

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Collapsing of logic values during synthesis

L and H are not normally honored by synthesis software. Most synthesis tools collapse "meaningless" (to them) values to more sensible ones, e.g.

- ▶ L → 0

- ▶ H → 1

- $\blacktriangleright$  X or W  $\mapsto$  –

#### Hint for RTL synthesis

For the sake of clarity and portability, do not use logic values other than 0, 1, Z and – in VHDL source code that is intended for synthesis.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

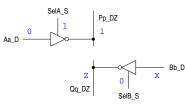

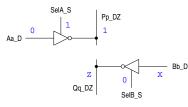

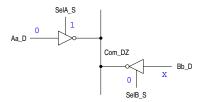

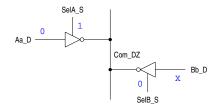

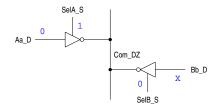

## How to model a bidirectional line in VHDL I

Want to model a circuit node that can be driven from multiple subcircuits?  $\rightsquigarrow$  Use two or more conditional signal assignments.

#### Example:

signal Com\_DZ, Aa\_D, Bb\_D, SelA\_S, SelB\_S : std\_logic;

```

Com_DZ <= not Aa_D when SelA_S='1' else 'Z';

.....

Com_DZ <= not Bb_D when SelB_S='1' else 'Z';

.....

```

#### Note

Node Com\_DZ is left floating when neither of the two drivers is enabled.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

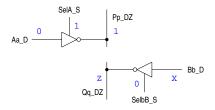

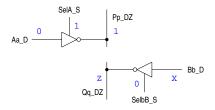

SelA S

Aa D

## How to model a bidirectional line in VHDL II

single-driver signals Pp\_DZ and Qq\_DZ may assume distinct logic values, no difference between std ulogic and std logic if multi-driver signal Com\_DZ is of type std\_ulogic then an error message gets issued std\_logic then the conflict is resolved to Com DZ = 1

Com DZ

SelB S

Bb D

х

b)

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## How to model a bidirectional line in VHDL II

single-driver signals Pp\_DZ and Qq\_DZ may assume distinct logic values, no difference between std ulogic and std logic

if multi-driver signal Com\_DZ is of type

std\_ulogic then an error message gets issued

std\_logic then the conflict is resolved to Com\_DZ = 1

#### Observation

b)

The distinction between types std\_ulogic and std\_logic matters only when simulating a multi-driver node:

std\_logictacitely resolves all conflicts that might occurstd\_ulogicgenerates a message in case of conflict

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## The IEEE 1164 standard resolution function

| resolution function "resolved" |                                                                           |                                                                                                                           |                                                                                         |                                                      |                                                      |                                                      |                                                      |                                                                                                        |

|--------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| consta<br>                     | nt resolut                                                                |                                                                                                                           |                                                                                         |                                                      |                                                      |                                                      |                                                      |                                                                                                        |

|                                | U                                                                         | X 0                                                                                                                       | 1 Z                                                                                     |                                                      | _                                                    |                                                      |                                                      |                                                                                                        |

|                                | ('U', '<br>('U', '<br>('U', '<br>('U', '<br>('U', '<br>('U', '<br>('U', ' | 'X', 'X',       'X', '0',       'X', '0',       'X', '0',       'X', '0',       'X', '0',       'X', '0',       'X', '0', | 'X', 'X',<br>'X', 'O',<br>'1', '1',<br>'1', 'Z',<br>'1', 'W',<br>'1', 'L',<br>'1', 'H', | 'X',<br>'0',<br>'1',<br>'W',<br>'W',<br>'W',<br>'W', | 'X',<br>'O',<br>'1',<br>'L',<br>'W',<br>'L',<br>'W', | 'X',<br>'O',<br>'1',<br>'H',<br>'W',<br>'W',<br>'H', | , X,<br>, X,<br>, X,<br>, X,<br>, X,<br>, X,<br>, X, | ),   U  <br>),   X  <br>),   0  <br>),   1  <br>),   Z  <br>),   W  <br>),   L  <br>),   H  <br>),   - |

| );                             |                                                                           |                                                                                                                           |                                                                                         |                                                      |                                                      |                                                      |                                                      |                                                                                                        |

► This is the default resolution function, others can be added.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Data type std\_logic versus std\_ulogic

- Signals of type std\_logic can accommodate multiple drivers whereas those of type std\_ulogic can not.

- An error message will tell should a std\_ulogic-type signal accidentally get involved in a naming conflict, so this is the more conservative choice.

- A signal is allowed to be driven from multiple processes iff a resolution function is defined that determines the outcome.

- There can be no such thing as a resolution function for variables, neither for bit, bit\_vector, integer, real, and similar data types.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Data types for modeling single-bit signals

| data type                       | bit  | std_ulogic          | std_logic |  |  |  |

|---------------------------------|------|---------------------|-----------|--|--|--|

| defined in                      | VHDL | ieee.std_logic_1164 |           |  |  |  |

| value set per binary digit      | 2    | 9                   |           |  |  |  |

| for simulation purposes         |      |                     |           |  |  |  |

| modeling of power-up phase      | no   | yes                 | yes       |  |  |  |

| modeling of weakly driven nodes | no   | yes                 | yes       |  |  |  |

| modeling of multi-driver nodes  | no   | yes                 | yes       |  |  |  |

| handling of drive conflicts     | n.a. | reported            | resolved  |  |  |  |

| for synthesis purposes          |      |                     |           |  |  |  |

| three-state drivers             | no   | yes                 | yes       |  |  |  |

| don't care conditions           | no   | yes                 | yes       |  |  |  |

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Data types for modeling multi-bit signals

| data type(s)                   | integer, | bit_                           | std_logic | signed,  | signed,  |

|--------------------------------|----------|--------------------------------|-----------|----------|----------|

|                                | natural, | vector                         | _vector   | unsigned | unsigned |

|                                | positive |                                |           |          |          |

| defined in                     | VHDL     | VHDL                           | ieee.     | ieee.    | ieee.    |

|                                |          |                                | std_logic | numeric  | numeric  |

|                                |          |                                | _1164     | _bit     | _std     |

| value set per binary digit     | 2        | 2                              | 9         | 2        | 9        |

| word width                     | 32 bit   | at the programmer's discretion |           |          | ion      |

| arithmetic operations          | yes      | no                             | no        | yes      | yes      |

| logic operations               | no       | yes                            | yes       | yes      | yes      |

| access to subwords or bits     | no       | yes                            | yes       | yes      | yes      |

| modeling of electrical effects | no       | no                             | yes       | no       | yes      |

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Data types for modeling multi-bit signals

| data type(s)                   | integer, | bit_                           | std_logic | signed,  | signed,  |

|--------------------------------|----------|--------------------------------|-----------|----------|----------|

|                                | natural, | vector                         | _vector   | unsigned | unsigned |

|                                | positive |                                |           |          |          |

| defined in                     | VHDL     | VHDL                           | ieee.     | ieee.    | ieee.    |

|                                |          |                                | std_logic | numeric  | numeric  |

|                                |          |                                | _1164     | _bit     | _std     |

| value set per binary digit     | 2        | 2                              | 9         | 2        | 9        |

| word width                     | 32 bit   | at the programmer's discretion |           |          | ion      |

| arithmetic operations          | yes      | no                             | no        | yes      | yes      |

| logic operations               | no       | yes                            | yes       | yes      | yes      |

| access to subwords or bits     | no       | yes                            | yes       | yes      | yes      |

| modeling of electrical effects | no       | no                             | yes       | no       | yes      |

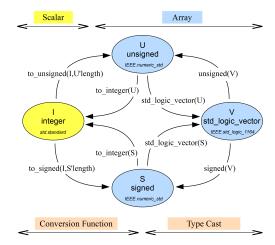

► VHDL is strongly typed = extensive type checking is performed → must convert before assignment or comparison across types.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

## Converting between data types

Figure: VHDL type conversion paths (chart courtesy of Dr. Jürgen Wassner).

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Orientation of binary vectors

#### Hint

Any vector that contains a data item coded in some positional number system should consistently be declared as  $(i_{MSB} \text{ downto } i_{LSB})$  where  $2^i$  is the weight of the binary digit with index *i*.

The MSB so has the highest index assigned to it and appears in the customary leftmost position because  $i_{MSB} \ge i_{LSB}$ . Example signal Hour\_D : unsigned(4 downto 0) := "10111";

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Orientation of binary vectors

#### Hint

Any vector that contains a data item coded in some positional number system should consistently be declared as  $(i_{MSB} \text{ downto } i_{LSB})$  where  $2^i$  is the weight of the binary digit with index *i*.

The MSB so has the highest index assigned to it and appears in the customary leftmost position because  $i_{MSB} \ge i_{LSB}$ . Example signal Hour\_D : unsigned(4 downto 0) := "10111";

Types unsigned and signed are for integer numbers:

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Orientation of binary vectors

#### Hint

Any vector that contains a data item coded in some positional number system should consistently be declared as  $(i_{MSB} \text{ downto } i_{LSB})$  where  $2^i$  is the weight of the binary digit with index *i*.

The MSB so has the highest index assigned to it and appears in the customary leftmost position because  $i_{MSB} \ge i_{LSB}$ . Example signal Hour\_D : unsigned(4 downto 0) := "10111";

Types unsigned and signed are for integer numbers:

What about fractional parts .ff...f ?

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Data types for fractional and floating point numbers

#### Introduced with the IEEE 1076-2008 revision.

| type prefix                    | unresolved_                    |        |                | unresolved |

|--------------------------------|--------------------------------|--------|----------------|------------|

| data type                      | ufixed                         | sfixed | float          | resolved   |

| defined in                     | fixed_                         |        | $float_{-}$    |            |

|                                | $generic_{-}$                  |        | $generic_{-}$  |            |

|                                | pkg                            |        | pkg            |            |

| arithmetics                    | fixed point                    |        | floating point |            |

|                                | unsigned                       | signed |                |            |

| word width                     | at the programmer's discretion |        |                |            |

| arithmetic operations          | yes                            |        |                |            |

| logic operations               | yes                            |        |                |            |

| access to subwords or bits     | yes                            |        |                |            |

| modeling of electrical effects | <b>yes</b> (resolved)          |        |                |            |

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

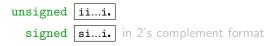

### Data types for fractional numbers

Both signed and unsigned formats exist; 2'C format used for signed numbers.

Unsigned example

signal HourWithQuarter\_D : ufixed(4 downto -2) := "1011111";

```

iiiii.ff (\mapsto range 0 to 11111.11<sub>2</sub> = 31.75<sub>10</sub>

```

```

in steps of \frac{1}{4}, initial value = 10111.11<sub>2</sub> = 23.75<sub>10</sub>)

```

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Data types for fractional numbers

Both signed and unsigned formats exist; 2'C format used for signed numbers.

```

Unsigned example

signal HourWithQuarter_D : ufixed(4 downto -2) := "1011111";

iiiii.ff (\mapsto range 0 to 11111.11<sub>2</sub> = 31.75<sub>10</sub>

in steps of \frac{1}{4}, initial value = 10111.11<sub>2</sub> = 23.75<sub>10</sub>)

Signed example

signal HourWithQuarter_D : sfixed(4 downto -2) := "1011111";

```

**siiii.ff** ( $\mapsto$  range 10000.00<sub>2</sub> = -16.00<sub>10</sub> to 01111.11<sub>2</sub> = 15.75<sub>10</sub> in steps of  $\frac{1}{4}$ , initial value = 10111.11<sub>2</sub> = -9.75<sub>10</sub>)

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Data types for fractional numbers

Both signed and unsigned formats exist; 2'C format used for signed numbers.

```

Unsigned example

signal HourWithQuarter_D : ufixed(4 downto -2) := "1011111";

iiiii.ff] (\mapsto range 0 to 11111.11<sub>2</sub> = 31.75<sub>10</sub>

in steps of \frac{1}{4}, initial value = 10111.11<sub>2</sub> = 23.75<sub>10</sub>)

Signed example

signal HourWithQuarter_D : sfixed(4 downto -2) := "1011111";

siiii.ff] (\mapsto range 10000.00<sub>2</sub> = -16.00<sub>10</sub> to 01111.11<sub>2</sub> = 15.75<sub>10</sub>)

```

in steps of  $\frac{1}{4}$ , initial value = 10111.11<sub>2</sub> = -9.75<sub>10</sub>)

- For maximum versatility, some arithmetic aspects are kept user-adjustable via generics:

- Rounding behavior. (round  $\approx$  vs. truncate  $\downarrow$ ).

- ► Overflow behavior (saturate \_\_\_\_\_ vs. wrap around ////).

- Number of guard bits for division operation (extra digit positions used to reduce the roundoff error)

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Data types for floating point numbers

Floating point numbers include a sign bit and an exponent by definition.

- Formats adhere to the principles of the IEEE 754 standard, except # of bits for exponent and mantissa are defined in type declaration.

- Mantissa is coded as a fractional number in 2'C format.

- Exponent is coded in O-B (offset-binary) format.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Data types for floating point numbers

Floating point numbers include a sign bit and an exponent by definition.

- Formats adhere to the principles of the IEEE 754 standard, except # of bits for exponent and mantissa are defined in type declaration.

- Mantissa is coded as a fractional number in 2'C format.

- Exponent is coded in O-B (offset-binary) format.

#### Example

signal ToyFloat\_D : float(5 downto -8);

The number format so specified is seeeee.ffffffff where

- #e = 5 and #f = 8

- s stands for the sign bit (of the mantissa)

- each e stands for one bit of the exponent (with an offset  $2^{\#e-1}-1=15$ )

- ▶ each f stands for one bit of the mantissa (normalized to the interval [1...2) and with binary weights from <sup>1</sup>/<sub>2</sub> all the way down to <sup>1</sup>/<sub>256</sub>)

#### Online translators available on the Internet!

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

#### 4th HDL capability: An event-based model of time

Figure: ... plus an event queue mechanism that governs process activation ...

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### How does VHDL simulation work? I

Please recall:

A signal's value can be altered by any of ...

- Concurrent signal assignment (simplest)

- Selected signal assignment

- Conditional signal assignment

- process statement (most powerful).

#### Make sure to understand

All the above constructs are concurrent processes aka threads of execution (in the sense of the German "nebenläufiger Prozess").

"process statement", in contrast, refers to a specific VHDL language construct (identified by the presence of the reserved word process).

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

#### How does VHDL simulation work? II

- A typical circuit model comprises many many processes.

- No more than a few processor cores are normally available for running the simulation code.

- Yet, simulation is to yield the same result as if all processes were operating simultaneously.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

#### How does VHDL simulation work? II

- A typical circuit model comprises many many processes.

- No more than a few processor cores are normally available for running the simulation code.

- Yet, simulation is to yield the same result as if all processes were operating simultaneously.

#### HDL requirement no.4

A mechanism that schedules processes for sequential execution and that combines their effects such as to perfectly mimic concurrency.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

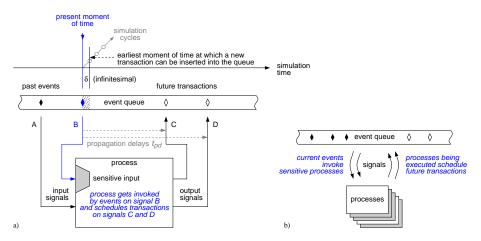

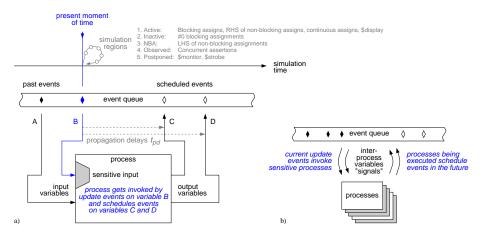

### Notions of time

Simulation time is to an HDL what physical time is to the hardware being modeled. The simulator can be thought to maintain some kind of stop watch that registers the progress of simulation time.

Execution time (aka wall clock) refers to the time a computer takes to execute statements from the program code during simulation.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Notions of time

Simulation time is to an HDL what physical time is to the hardware being modeled. The simulator can be thought to maintain some kind of stop watch that registers the progress of simulation time.

## Execution time (aka wall clock) refers to the time a computer takes to execute statements from the program code during simulation.

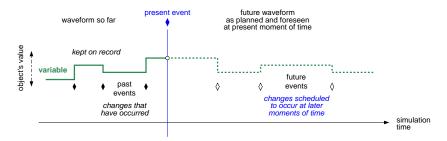

- In VHDL simulation, the continuum of time gets subdivided by events each of which occurs at a precise moment of simulation time.

- ► An event is said to happen whenever the value of a signal changes.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

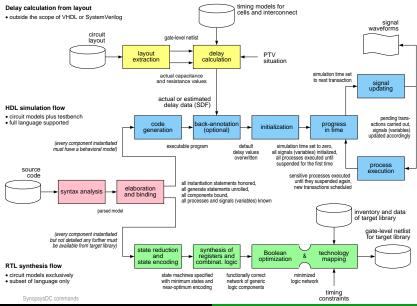

### Event-driven simulation I

Event-driven simulation works in cycles where three stages alternate:

- 1. Advance simulation time to the next transaction thereby making it the current one.

- 2. Set all signals that are to be updated at the present moment of time to the target value associated with the current transaction.

- 3. Invoke all processes that need to respond to the new situation. Every signal assignment there supposed to modify a signal's value causes a transaction to be entered into the event queue at that point in the future when the signal is anticipated to take on its new value.

Go to 1. and start a new simulation cycle.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

#### The event-queue mechanism

Figure: Interactions between the event queue and processes in VHDL.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Event-driven simulation II

- Simulation stops when the event queue becomes empty or when simulation time reaches some predefined final value.

- As nothing happens between transactions, an event-driven simulator essentially skips from one transaction to the next.

No computational resources are wasted while models sit idle.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Event-driven simulation II

- Simulation stops when the event queue becomes empty or when simulation time reaches some predefined final value.

- As nothing happens between transactions, an event-driven simulator essentially skips from one transaction to the next.

No computational resources are wasted while models sit idle.

#### Note the analogy between event queue and agenda

- Events are observable from the past evolution of a signal's value.

- Transactions reflect future plans that may or may not materialize.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

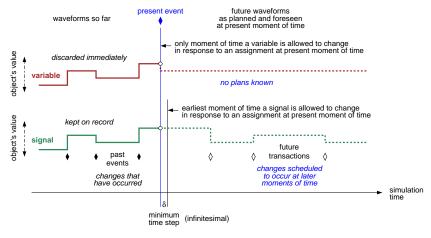

### Delay modeling for simulation I

Ramps can not be modeled.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Delay modeling for simulation II

#### Observation

The  $\delta$  delay serves to maintain a consistent order of transactions in models that include zero delays.

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

### Delay modeling for simulation II

#### Observation

The  $\delta$  delay serves to maintain a consistent order of transactions in models that include zero delays.

When simulating models with no delays (other than  $\delta$ ), it becomes difficult to distinguish between cause and effect from waveform output

as the respective events appear to coincide.

#### Hint

Fake delays help to visually tell apart cause and effect.

Example

Oup\_D <= InpA\_D + InpB\_D after FAKEDELAY;</pre>

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages

#### Signal versus variable I

Figure: The past, present and future of VHDL variables and signals.

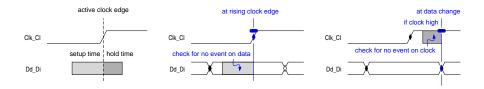

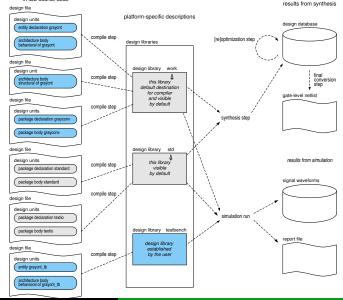

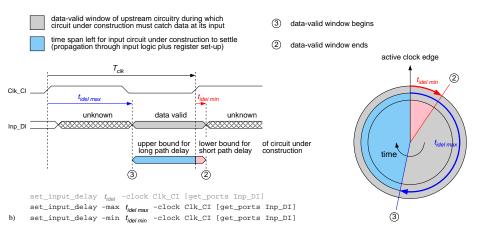

Circuit hierarchy and connectivity Interacting concurrent processes A discrete replacement for electrical signals An event-driven scheme of execution Facilities for model parametrization Concepts borrowed from programming languages