## From Algorithms to Architectures

Prof. Hubert Kaeslin Microelectronics Design Center ETH Zürich

Morgan Kaufmann "Top-Down Digital VLSI Design" Chapter 3

last update: July 18, 2014

## Content

#### You will learn

about the options for tailoring hardware to data/signal processing algorithms.

- General-purpose vs. special-purpose architectures and all sorts of compromises between the two

- ► A toolbox for optimizing VLSI architectures

- ▶ Iterative decomposition, pipelining, replication, time sharing

- Algebraic transforms

- Retiming

- Loop unfolding, pipeline interleaving

- ► Options for temporary storage of data

- ▶ Not so common architectural concepts

- ▶ Bit-serial architectures, distributed arithmetic

- Computing in semirings

## The goals of architecture design

- ► Decide on the necessary hardware resources for carrying out computations from data and/or signal processing.

- Organize their interplay such as to meet target specifications.

## The goals of architecture design

- ▶ Decide on the necessary hardware resources for carrying out computations from data and/or signal processing.

- Organize their interplay such as to meet target specifications.

- Concerns:

- 1. Functional correctness

- 2. Performance targets (throughput, operation rate, etc.)

- 3. Circuit size

- 4. Energy efficiency

- 5. Agility (wrt to evolving needs, changing specs, future standards)

- 6. Engineering effort and time to market

The architectural solution space Dedicated VLSI architectures and how to design them Equivalence transforms for combinational computations

## Subject

## The architectural solution space

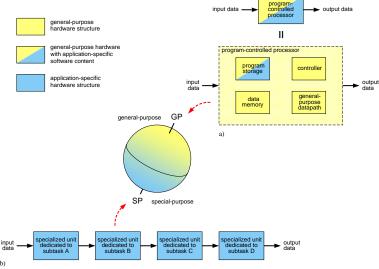

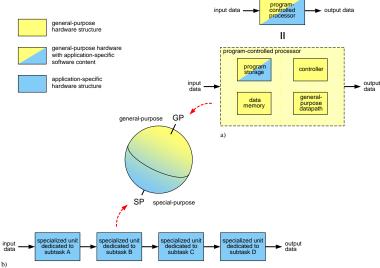

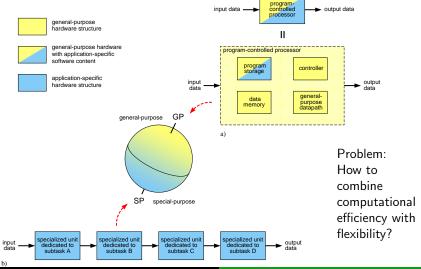

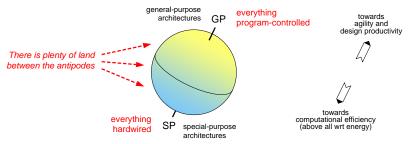

The antipodes

## What you ought to know about microprocessors

Instruction set processors execute one program instruction after the other in consecutive fetch-load-execute-store cycles.

ALU (arithmetic-logic unit) carries out data manipulations.

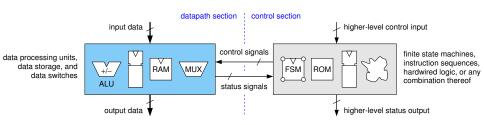

Datapath vs. Control section

von Neumann architecture common memory space, vs.

Harvard architecture separate memory spaces for data and program code.

#### The antipodes

What makes an algorithm suitable for a dedicated VLSI architecture: There is plenty of land between the antipodes Digest

## The architectural antipodes I

## The architectural antipodes II

|                 | Hardware architecture                        |                                 |  |  |

|-----------------|----------------------------------------------|---------------------------------|--|--|

|                 | General purpose                              | Special purpose                 |  |  |

| Algorithm       | any, not known a priori fixed, must be known |                                 |  |  |

| Architecture    | instruction set processor                    | dedicated, no single pattern    |  |  |

| Execution model | fetch-load-execute-store                     | process data item and pass on   |  |  |

|                 | "instruction-oriented"                       | "dataflow-oriented"             |  |  |

| Datapath        | ALU(s) plus memory                           | customized design               |  |  |

| Controller      | with program microcode                       | typically hardwired             |  |  |

| Performance     | instructions per second,                     | data throughput,                |  |  |

| indicator       | run time of benchmarks                       | can be anticipated analytically |  |  |

| Strengths       | highly flexible,                             | room for max. performance,      |  |  |

|                 | immediately available,                       | highly energy-efficient,        |  |  |

|                 | routine design flow,                         | lean circuitry                  |  |  |

|                 | low up-front costs                           |                                 |  |  |

The antipodes

## The architectural antipodes III

#### Guideline

Before embarking in ASIC design, find out

- ▶ Does an architecture dedicated to the application at hand make sense

- or is a program-controlled general-purpose processor more adequate?

The antipodes

## The architectural antipodes III

#### Guideline

Before embarking in ASIC design, find out

- ▶ Does an architecture dedicated to the application at hand make sense

- or is a program-controlled general-purpose processor more adequate?

- Opting for commercial microprocessors and/or FPL sidesteps many technical problems that absorb much attention when a custom IC is to be designed instead.

- Conversely, it is precisely

- the focus on the payload computation,

- ▶ the absence of programming and configuration overhead, and

- the full control over architecture, circuit, and layout details

that make it possible to optimize performance and energy efficiency.

## Example: Viterbi decoder

| Architecture      | General purpose          |            | Special    | purpose    |

|-------------------|--------------------------|------------|------------|------------|

| Key component     | DSP                      |            | ASIC       |            |

|                   | TI TMS320C6455           |            | sem03w6    | sem05w1    |

|                   | without with             |            | ETH        | ETH        |

|                   | Viterbi coprocessor VCP2 |            |            |            |

| Number of chips   | 1                        | 1          | 1          | 1          |

| CMOS process      | 90 nm                    | 90 nm      | 250 nm 5Al | 250 nm 5Al |

| Program code      | 187 Kibyte               | 242 Kibyte | none       | none       |

| Circuit size      | n.a.                     | n.a.       | 73 kGE     | 46 kGE     |

| Max. throughput   | 45 kbit/s                | 9 Mbit/s   | 310 Mbit/s | 54 Mbit/s  |

| @ clock           | 1 GHz                    | 1 GHz      | 310 MHz    | 54 MHz     |

| Power dissipation | 2.1 W                    | 2.1 W      | 1.9 W      | 50 mW      |

| Year              | 2005                     | 2005       | 2004       | 2006       |

#### Reasons:

- ▶ DSP optimized for sustained multiply-accumulates, word width 32 bit.

- ▶ Viterbi algorithm arranged to do without multiplication.

- ▶ Viterbi algorithm arranged to do with words of 6 bit or less.

- ▶ Dedicated architectures can exploit full potential for parallelism.

## Example: AES block cipher encrypter/decrypter

(Rijndael algorithm)

| Architecture      | General purpose | Special purpose |               |               |

|-------------------|-----------------|-----------------|---------------|---------------|

| Key component     | CISC Processor  | FPGA Xilinx     | ASIC (ETH)    | ASIC (UCLA)   |

|                   | Pentium III     | Virtex-II       | CryptoFun     | Rijndael core |

| Number of chips   | motherboard     | 1 + config.     | 1             | 1             |

| CMOS process      | n.a.            | 150 nm 8AI      | 180 nm 4Al2Cu | 180 nm 4Al2Cu |

| Max. throughput   | 648 Mbit/s      | 1.32 Gbit/s     | 2.0 Gbit/s    | 1.6 Gbit/s    |

| @ clock           | 1.13 GHz        | n.a.            | 172 MHz       | 125 MHz       |

| Power dissipation | 41.4 W          | 490 mW          | n.a.          | 56 mW         |

| @ supply          | n.a.            | 1.5 V           | 1.8 V         | 1.8 V         |

| Year              | 2000            | ≈ 2002          | 2007          | 2002          |

#### Reasons:

- ▶ Multiple LUTs included in hardware for S-Box function and inverse.

- Ciphering and subkey preparation carried out by concurrent units.

- Rijndael algorithm designed with Pentium III architecture in mind (MMX instructions, LUTs that fit into cache memory, etc.).

- ▶ Power dissipation of general-purpose processor remains daunting.

## When do dedicated architectures make sense?

### Dedicated architectures are favored by real-time applications such as

- ▶ Data, audio and video (de)compression

- ► Ciphering & deciphering (primarily for secret key ciphers)

- Error correction coding

- ► Digital modulation & demodulation (for modems, wireless communication, and disk drives)

- Adaptive channel equalization for copper lines and optical fibers

- ▶ Multipath combiners in broadband wireless access networks

- ► Computer graphics and video rendering

- ► Multimedia (e.g. MPEG, HDTV)

- ▶ Pattern recognition

The antipodes

What makes an algorithm suitable for a dedicated VLSI architecture<sup>:</sup> There is plenty of land between the antipodes Digest

## Answer

"Does it make sense to consider dedicated hardware architectures?"

YES Dedicated architectures outperform program-controlled processors by orders of magnitude (wrt throughput and energy efficiency) in many transformatorial systems where data streams get processed in fairly regular ways.

## Answer

"Does it make sense to consider dedicated hardware architectures?"

YES Dedicated architectures outperform program-controlled processors by orders of magnitude (wrt throughput and energy efficiency) in many transformatorial systems where data streams get processed in fairly regular ways.

#### but also

NO Dedicated architectures can not rival the agility and economy of processor-type designs in applications where the computation is primarily reactive, very irregular, highly data-dependent, or memory-hungry.

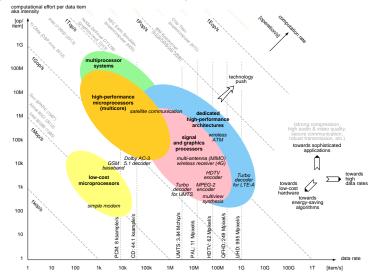

## Computational needs and capabilities

## Algorithms suitable for dedicated architectures

What makes an algorithm suitable for dedicated VLSI architectures?

### Ideally:

- 1. Loose coupling between major processing tasks

- Well-defined functional specification for each task.

- Manageable interactions between them.

## Algorithms suitable for dedicated architectures

What makes an algorithm suitable for dedicated VLSI architectures?

### Ideally:

- 1. Loose coupling between major processing tasks

- Well-defined functional specification for each task.

- Manageable interactions between them.

- 2. Simple control flow

- Course of operation does not depend on the data being processed.

- No need for overly many modes of operations, data formats, etc.

- Makes it possible to anticipate the datapath resources required to meet throughput goal and to design the architecture accordingly.

- ▶ Permits control by counters and simple finite state machines.

## Algorithms suitable for dedicated architectures

- 3. Regular data flow, recurrence of a few identical operations

- Opens a door for sharing hardware resources in an efficient way.

## Algorithms suitable for dedicated architectures

- 3. Regular data flow, recurrence of a few identical operations

- ▶ Opens a door for sharing hardware resources in an efficient way.

- 4. Reasonable storage requirements

- ▶ Renders on-chip memories economically possible.

- ► Massive storage requirements in conjunction with moderate computational burdens place dedicated architectures at a disadvantage.

## Algorithms suitable for dedicated architectures

- 3. Regular data flow, recurrence of a few identical operations

- ▶ Opens a door for sharing hardware resources in an efficient way.

- 4. Reasonable storage requirements

- ▶ Renders on-chip memories economically possible.

- Massive storage requirements in conjunction with moderate computational burdens place dedicated architectures at a disadvantage.

- 5. Compatible with finite precision arithmetics

- Insensitive to effects from finite precision, no need for floating-point arithmetics

- Area, logic delay, interconnect length, parasitic capacitances, and energy dissipation all grow with word width, they combine into a burden that multiplies at an overproportional rate.

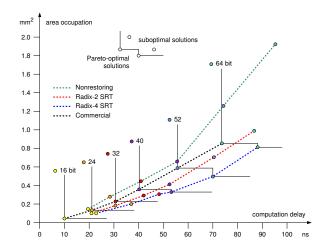

# Example: Fixed-point division

Figure: Comparison of hardware divider architectures for a 180 nm CMOS process under worst-case PTV conditions. Note the impact of quotient width.

## Algorithms suitable for dedicated architectures

- ... continued

- 6. Non-recursive linear time-invariant computation over some algebraic field

- Opens a door for reorganizing the data processing in many ways.

- ▶ High-speed operation, in particular, is much easier to obtain.

## Algorithms suitable for dedicated architectures

- ... continued

- 6. Non-recursive linear time-invariant computation over some algebraic field

- ▶ Opens a door for reorganizing the data processing in many ways.

- ▶ High-speed operation, in particular, is much easier to obtain.

- 7. No transcendental functions

- Roots, logarithmic, exponential, or trigonom. functions, translations between incompatible number systems are expensive in hardware.

- o Results must either be stored in large lookup tables (LUTs) or

- o get calculated on-line in lengthy computation sequences.

## Algorithms suitable for dedicated architectures

- 6. Non-recursive linear time-invariant computation over some algebraic field

- Opens a door for reorganizing the data processing in many ways.

- ► High-speed operation, in particular, is much easier to obtain.

- 7. No transcendental functions

- ▶ Roots, logarithmic, exponential, or trigonom. functions, translations between incompatible number systems are expensive in hardware.

- Results must either be stored in large lookup tables (LUTs) or

- o get calculated on-line in lengthy computation sequences.

- 8. Extensive usage of operations unavailable from instruction sets

- ► Replace lengthy instruction sequences by dedicated computational units, e.g. finite field arithmetics, many ciphering operations, CORDIC.

- Fixed arguments often allow for some form of preprocessing, e.g.

- drop unit factors and/or zero sum terms.

- adopt special number representation schemes,

- take advantage of symmetries and precomputed lookup tables.

## Algorithms suitable for dedicated architectures

- 9. No divisions and multiplications on very wide data words

- ▶ Much more expensive than addition and subtraction.

- ▶ Vast numerical range of results gives rise to scaling issues.

- Matrix inversion is a particularly nasty case in point as it involves divisions and often brings about numerical instability.

## Algorithms suitable for dedicated architectures

- 9. No divisions and multiplications on very wide data words

- ▶ Much more expensive than addition and subtraction.

- ▶ Vast numerical range of results gives rise to scaling issues.

- Matrix inversion is a particularly nasty case in point as it involves divisions and often brings about numerical instability.

- 10. Throughput rather than latency is what matters

- ► Tight latency requirements rule out pipelining

- but are not in favor of microprocessors either as program-controlled operation can not normally guarantee fixed response times, even less so when a complex operating system is involved.

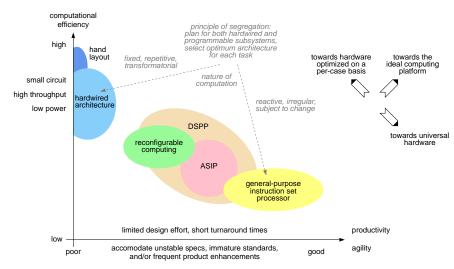

## The architectural solution space

## The architectural solution space

## Have a look at typical electronic devices

| 31          |                                         |                                   |  |  |

|-------------|-----------------------------------------|-----------------------------------|--|--|

|             | Subfunctions primarily characterized by |                                   |  |  |

|             | irregular control flow and/or           | repetitive control flow and       |  |  |

| Application | need for flexibility                    | need for computing efficiency     |  |  |

| Blu-ray     | user interface, track seeking,          | 16-to-8 bit demodulation,         |  |  |

| player      | tray and spindle control,               | error correction,                 |  |  |

|             | processing of non-video data            | MPEG-2 decompression,             |  |  |

|             | (directory, title, author,              | deciphering (AACS AES-128),       |  |  |

|             | subtitles, region codes)                | video signal processing           |  |  |

| Smartphone  | user interface, SMS/MMS,                | intermediate frequency filtering, |  |  |

|             | directory management,                   | (de)modul., channel (de)coding,   |  |  |

|             | battery monitoring,                     | error correction (de)coding,      |  |  |

|             | communication protocol,                 | (de)ciphering, speech and         |  |  |

|             | channel allocation,                     | video (de)compression,            |  |  |

|             | roaming, accounting                     | display graphics                  |  |  |

## Have a look at typical electronic devices

| 31          |                                         |                                   |  |  |

|-------------|-----------------------------------------|-----------------------------------|--|--|

|             | Subfunctions primarily characterized by |                                   |  |  |

|             | irregular control flow and/or           | repetitive control flow and       |  |  |

| Application | need for flexibility                    | need for computing efficiency     |  |  |

| Blu-ray     | user interface, track seeking,          | 16-to-8 bit demodulation,         |  |  |

| player      | tray and spindle control,               | error correction,                 |  |  |

|             | processing of non-video data            | MPEG-2 decompression,             |  |  |

|             | (directory, title, author,              | deciphering (AACS AES-128),       |  |  |

|             | subtitles, region codes)                | video signal processing           |  |  |

| Smartphone  | user interface, SMS/MMS,                | intermediate frequency filtering, |  |  |

|             | directory management,                   | (de)modul., channel (de)coding,   |  |  |

|             | battery monitoring,                     | error correction (de)coding,      |  |  |

|             | communication protocol,                 | (de)ciphering, speech and         |  |  |

|             | channel allocation,                     | video (de)compression,            |  |  |

|             | roaming, accounting                     | display graphics                  |  |  |

### Guideline

Segregate the needs for computational efficiency from those of agility!

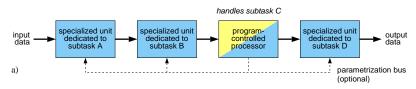

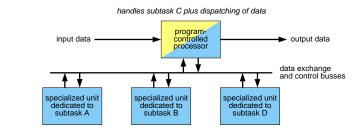

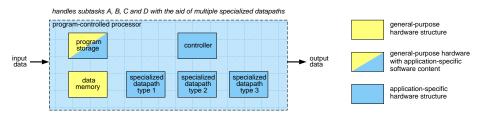

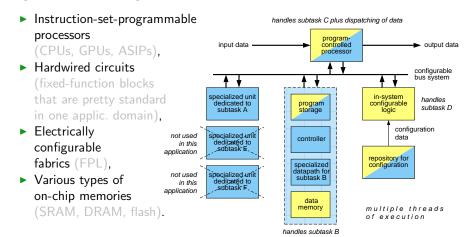

## 1. Dedicated satellites and 2. Host with helper engines

Figure: Chain of general-purpose processor and dedicated satellites (a), host computer with specialized fixed-function blocks or coprocessors (b).

b)

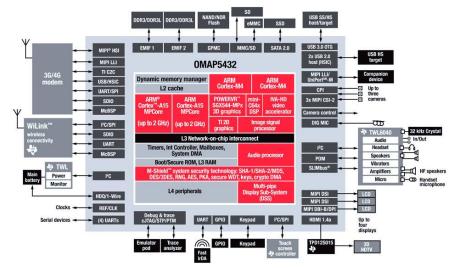

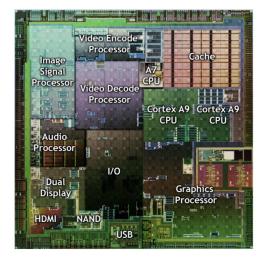

## Example: System on a chip for smartphones (by Texas Instr.)

## 3. Application-specific instruction set processor (ASIP)

- ▶ Program-controlled operation → highly flexible

- ► Application-specific features confined to datapath circuitry

- ► Single thread of execution (concurrency limited to SIMD), easily extended to multiple threads (by including multiple ASIP cores)

## Example: AES cipher encrypter/decrypter revisited

| General purpose | Special purpose |               |               | ASIP            |

|-----------------|-----------------|---------------|---------------|-----------------|

| CISC Processor  | FPGA Xilinx     | ASIC (ETH)    | ASIC (UCLA)   | Cryptoprocessor |

| Pentium III     | Virtex-II       | CryptoFun     | Rijndael core | core UCLA       |

| motherboard     | 1 + config.     | 1             | 1             | 1               |

| Assembler       | none            | none          | none          | Assembler       |

| n.a.            | n.a.            | 76 kGE        | 173 kGE       | 73.2 kGE        |

| n.a.            | 150 nm 8AI      | 180 nm 4Al2Cu | 180 nm 4Al2Cu | 180 nm 4Al2Cu   |

| 648 Mbit/s      | 1.32 Gbit/s     | 2.0 Gbit/s    | 1.6 Gbit/s    | 3.43 Gbit/s     |

| 1.13 GHz        | n.a.            | 172 MHz       | 125 MHz       | 295 MHz         |

| 41.4 W          | 490 mW          | n.a.          | 56 mW         | 86 mW           |

| n.a.            | 1.5 V           | 1.8 V         | 1.8 V         | 1.8 V           |

| 2000            | ≈ 2002          | 2007          | 2002          | 2004            |

#### Observation

ASIP combines excellent throughput and low power with the agility of a program-controlled architecture.

## Example: AES cipher encrypter/decrypter revisited

| General purpose | Special purpose |               |               | ASIP            |

|-----------------|-----------------|---------------|---------------|-----------------|

| CISC Processor  | FPGA Xilinx     | ASIC (ETH)    | ASIC (UCLA)   | Cryptoprocessor |

| Pentium III     | Virtex-II       | CryptoFun     | Rijndael core | core UCLA       |

| motherboard     | 1 + config.     | 1             | 1             | 1               |

| Assembler       | none            | none          | none          | Assembler       |

| n.a.            | n.a.            | 76 kGE        | 173 kGE       | 73.2 kGE        |

| n.a.            | 150 nm 8AI      | 180 nm 4Al2Cu | 180 nm 4Al2Cu | 180 nm 4Al2Cu   |

| 648 Mbit/s      | 1.32 Gbit/s     | 2.0 Gbit/s    | 1.6 Gbit/s    | 3.43 Gbit/s     |

| 1.13 GHz        | n.a.            | 172 MHz       | 125 MHz       | 295 MHz         |

| 41.4 W          | 490 mW          | n.a.          | 56 mW         | 86 mW           |

| n.a.            | 1.5 V           | 1.8 V         | 1.8 V         | 1.8 V           |

| 2000            | ≈ 2002          | 2007          | 2002          | 2004            |

#### Observation

ASIP combines excellent throughput and low power with the agility of a program-controlled architecture.

Catch: proprietary instruction set → special assembler, libraries, debuggers, ...

The antipodes

What makes an algorithm suitable for a dedicated VLSI architecture

There is plenty of land between the antipodes

Digest

### A framework for accelerating ASIP design

#### LISA = Language for Instruction Set Architectures

(developed by CoWare Inc. acquired by Synopsys in 2010)

#### The design flow essentially goes

- 1. Define the most adequate instruction set for a target application,

- 2. Refine the architecture into a cycle-accurate model (optional),

- 3. Cast your architecture into an RTL-type model (optional) using the LISA language.

#### System-level software tools then generate

- Assembler, linker, and simulator tools.

- ▶ VHDL synthesis code (from the RTL model).

Predefined processor templates also available.

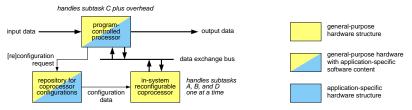

#### 4. Reconfigurable computing (promoted by FPL vendors)

Figure: General-purpose processor with juxtaposed reconfigurable coprocessor.

#### General procedure:

- 1. Designers come up with a specific circuit structure for each major piece of suitable computation.

- 2. All configurations get stored in memory.

- 3. Whenever the host encounters a call to one of those computations, it downloads the pertaining configuration file into the FPL

- 4. Host feeds coprocessor with data and fetches results.

- 5. Host proceeds after computation completes.

#### 4. Reconfigurable computing (promoted by FPL vendors)

Figure: General-purpose processor with juxtaposed reconfigurable coprocessor.

#### General procedure:

- 1. Designers come up with a specific circuit structure for each major piece of suitable computation.

- 2. All configurations get stored in memory.

- 3. Whenever the host encounters a call to one of those computations, it downloads the pertaining configuration file into the FPL  $\leadsto$  dead time!

- 4. Host feeds coprocessor with data and fetches results.

- 5. Host proceeds after computation completes.

#### 5. Extendable instruction set processor (by Stretch Inc.)

#### General procedure:

- 1. System developers write application programs in C or C++.

- 2. Proprietary EDA tools identify instruction sequences that are executed many times over (hot spots).

- 3. For each such sequence, reconfigurable logic is synthesized into a parallel computation network that completes within one clock cycle.

- 4. Each occurrence of the original instruction sequence gets replaced by a function call that activates the custom-made logic.

The antipodes

What makes an algorithm suitable for a dedicated VLSI architecture?

There is plenty of land between the antipodes

Dicest

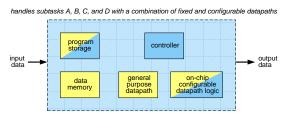

# 6. Domain-specific programmable platform (DSPP) (new)

= generous and heterogeneous circuit resources in one malleable platform

The antipodes What makes an algorithm suitable for a dedicated VLSI architecture? There is plenty of land between the antipodes Direst

# DSPP = platform ICs (continued)

- Specification is using a domain-specific high-level language.

- Developer tools assign most adequate execution units such as to meet performance target at minimum energy.

- ► The FPL is used to extend datapaths and/or instruction sets where beneficial (in terms of throughput, energy efficiency, updates, etc.).

- ▶ Little or no on-the-fly reconfiguration.

- All inactive subcircuits are turned off.

# DSPP = platform ICs (continued)

- Specification is using a domain-specific high-level language.

- Developer tools assign most adequate execution units such as to meet performance target at minimum energy.

- ► The FPL is used to extend datapaths and/or instruction sets where beneficial (in terms of throughput, energy efficiency, updates, etc.).

- ▶ Little or no on-the-fly reconfiguration.

- ▶ All inactive subcircuits are turned off.

#### Anticipated benefits

- + Good performance (intense computing done in hardware)

- + Energy-efficient (idem)

- + One platform covers a range of applications and products

- + Simplified design (essentially platform selection followed by assignment of subfunctions to the on-chip resources)

- + Agile, fast turnaround (unless fixed-function blocks need to be modified)

The antipodes What makes an algorithm suitable for a dedicated VLSI architecture? There is plenty of land between the antipodes Digest

### Reality check

- Transistors used lavishly, many subcircuits may never be put to service in a given application or product.

- Developer tools are in their infancy.

### Reality check

- Transistors used lavishly, many subcircuits may never be put to service in a given application or product.

- Developer tools are in their infancy.

Technological progress tends to make such concerns less and less relevant.

- ▶ Viability stands or falls with the tool chain.

- specification languages under development

- standards required to ensure code reuse and portability

- ▶ In line with trends from general-purpose computing and high-end FPGAs.

- costs per transistor \u00e1

- ▶ mask costs ↑

- ▶ verification costs ↑

- energy-efficient computing has become a prime concern

- ► CPU + GPU + FPL + fixed-function blocks + memory all on same chip

Cost structure to be discussed in chapter 16 "VLSI Economics and Project Management"

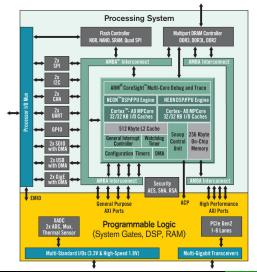

#### DSPP Forerunner: Zyng product family (by Xilinx Inc.)

"All Programmable SoC"

- ARM and DSP cores

- Hardwired fixed-function blocks

- Programmable logic

- Memories and memory controllers

The antipodes

What makes an algorithm suitable for a dedicated VLSI architecture

There is plenty of land between the antipodes

Digest

# DSPP = platform ICs (conclusion)

#### Preliminary assessment

Much remains to be done before platform ICs can dominate digital VLSI, but the concept benefits from numerous technological and economic trends.

"CPU and GPU cores are the new gates (EE Times, 2011)

### DSPP = platform ICs (conclusion)

#### Preliminary assessment

Much remains to be done before platform ICs can dominate digital VLSI, but the concept benefits from numerous technological and economic trends.

"CPU and GPU cores are the new gates (EE Times, 2011) ... and platform ICs are the new gate arrays (H. Kaeslin)."

The antipodes What makes an algorithm suitable for a dedicated VLSI architecture There is plenty of land between the antipodes Digest

### Insight gained

The antipodes What makes an algorithm suitable for a dedicated VLSI architecture. There is plenty of land between the antipodes Digest

### Insight gained

#### Guideline

- ▶ Rely on dedicated hardware only for those subfunctions that are called many times and are unlikely to change.

- ▶ Keep the rest programmable (via software or reconfiguration).

The antipodes What makes an algorithm suitable for a dedicated VLSI architecture There is plenty of land between the antipodes Digest

### The basic options of architecture design

The antipodes What makes an algorithm suitable for a dedicated VLSI architecture There is plenty of land between the antipodes Digest

# Example: An industrial SoC

Note the coexistence of

- general-purpose processors

- ASIPs, and

- hardwired helper engines on the same die.

Figure: Tegra 2 chip for smartphones and tablet computers (source Nvidia).

The architectural solution space Dedicated VLSI architectures and how to design them Equivalence transforms for combinational computations Options for temporary storage of data Equivalence transforms for non-recursive computations Equivalence transforms for accursive computations Ceneralizations of the transform approach

There is room for remodeling in the algorithmic domain ... and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative merits of architectural alternatives Computation cycle versus clock period

# Subject

How to design dedicated VLSI architectures

There is room for remodeling in the algorithmic domain... and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative merits of architectural alternatives Computation cycle versus clock period.

### Why do we focus on dedicated architectures?

Many techniques for obtaining high performance at low cost are shared between general- and special-purpose architectures.

Yet, our emphasis is on dedicated architectures because

- ▶ A priori knowledge of a computational problem offers room for ideas that do not apply to instruction set processors.

- ▶ Utmost performance requirements often ask for special-purpose designs.

- ► The same holds for energy efficiency.

- Industry provides us with a vast selection of micro- and signal processors making proprietary designs hard to justify.

- ▶ There exists a comprehensive literature on general-purpose architectures.

There is room for remodeling in the algorithmic domain ...

### Most processing algos must be reworked for hardware I

Departures from some mathematically ideal algorithm are almost always necessary to arrive at an economically feasible solution. Examples follow.

Digital filter Tolerate a somewhat lower stopband suppression in exchange for a reduced computational burden.

(e.g. lower order, smaller coefficients replaced by zeros.)

There is room for remodeling in the algorithmic domain ...

### Most processing algos must be reworked for hardware I

Departures from some mathematically ideal algorithm are almost always necessary to arrive at an economically feasible solution. Examples follow.

Digital filter Tolerate a somewhat lower stopband suppression in exchange for a reduced computational burden.

(e.g. lower order, smaller coefficients replaced by zeros.)

Viterbi decoder (for convolutional codes) Sacrifice 0.1 dB or so of coding gain for the benefit of doing computations in a more economic way. (e.g. truncated dynamic range, frequent rescaling, restricted

traceback.)

### Most processing algos must be reworked for hardware II

Autocorrelation function

Replace computation of

$$ACF_{xx}(k) = r_{xx}(k) = \sum_{n=-\infty}^{\infty} x(n) \cdot x(n+k)$$

by the average magnitude difference function

$$AMDF_{xx}(k) = r'_{xx}(k) = \sum_{n=0}^{N-1} |x(n) - x(n+k)|$$

### Most processing algos must be reworked for hardware III

#### Magnitude function

► Approximated with shift, add and compare.

| Name                  | aka                    | Formula                                          |  |

|-----------------------|------------------------|--------------------------------------------------|--|

| lesser                | $\ell^{-\infty}$ -norm | $I = \min( a ,  b )$                             |  |

| sum                   | $\ell^1$ -norm         | s =  a  +  b                                     |  |

| magnitude (reference) | $\ell^2$ -norm         | $m = \sqrt{a^2 + b^2}$                           |  |

| greater               | $\ell^\infty$ -norm    | $g = \max( a , b )$                              |  |

| Approximation 1       |                        | $m \approx \frac{3}{8}s + \frac{5}{8}g$          |  |

| Approximation 2       |                        | $m \approx \max(g, \frac{7}{8}g + \frac{1}{2}I)$ |  |

▶ Simply replaced by  $\ell^1$ - or  $\ell^\infty$ -norm. (finds applications in MIMO decoders, for instance.)

... and there is room in the architectural domain

### Finding an optimal hardware organization

#### Guideline

There is room for remodeling computations in two distinct domains:

- Processing algorithm.

- Hardware architecture.

... and there is room in the architectural domain

# Finding an optimal hardware organization

#### Guideline

There is room for remodeling computations in two distinct domains:

- Processing algorithm.

- Hardware architecture.

Alternative choices in the algorithmic domain. How to tailor an algorithm such as to cut the computational burden, to trim down memory requirements, and/or to speed up calculations without incurring unacceptable implementation losses?

There is room for remodeling in the algorithmic domain ... and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative ments of architectural alternatives Computation cycle versus clock period

### Finding an optimal hardware organization

#### Guideline

There is room for remodeling computations in two distinct domains:

- ► Processing algorithm.

- ▶ Hardware architecture.

Alternative choices in the algorithmic domain. How to tailor an algorithm such as to cut the computational burden, to trim down memory requirements, and/or to speed up calculations without incurring unacceptable implementation losses?

Equivalence transforms in the architectural domain. How to (re)organize a computation such as to optimize throughput, circuit size, energy efficiency and overall costs while leaving the input-to-output relationship unchanged except, possibly, for latency?

We shall focus on the latter.

There is room for remodeling in the algorithmic domain and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative merits of architectural alternatives Computation cycle versus clock period

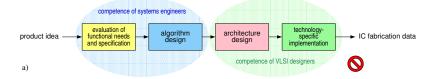

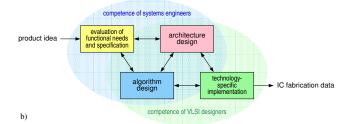

#### Systems engineers and VLSI designers must collaborate

Figure: Sequential thinking (a) versus networked team (b).

There is room for remodeling in the algorithmic domain ... and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative ments of architectural alternatives Computation cycle versus clock period

# Insight gained

#### Observation

It is always necessary to balance many contradicting requirements to arrive at a working and marketable embodiment of an algorithm.

- ► There is more to VLSI design than accepting a given algorithm and turning that into hardware with the aid of some HDL synthesizer.

- ► Algorithm design is not covered in this course, but nevertheless extremely important for VLSI design.

There is room for remodeling in the algorithmic domain ... and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative ments of architectural alternatives Computation cycle versus clock period

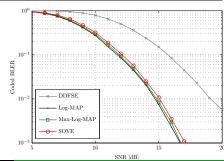

### Example: Sequence estimation for EDGE receiver

| Algorithm           | Delayed           | Max-log-MAP | Soft Output       |

|---------------------|-------------------|-------------|-------------------|

|                     | Decision Feedback |             | Viterbi Equalizer |

| Soft output         | no                | yes         | yes               |

| Forward recursion   | yes               | yes         | yes               |

| Backward recursion  | no                | yes         | no                |

| Backtracking step   | yes               | no          | no                |

| Memory requirements | 1x                | 50×         | 0.13x             |

#### Key design targets:

- ▶ soft output

- ▶ less than 577  $\mu$ s per burst

- small circuit, low power

- min. block error rate at any given signal-to-noise ratio

Which option would you go for?

There is room for remodeling in the algorithmic domain, and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative merits of architectural alternatives Computation cycle versus clock period

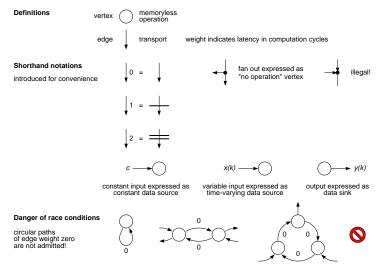

# Data dependency graphs (DDG)

There is room for remodeling in the algorithmic domain ., and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative merits of architectural alternatives Computation cycle versus clock period

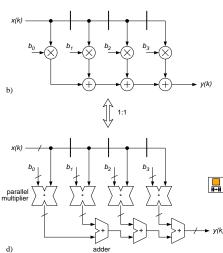

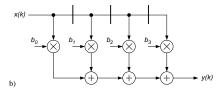

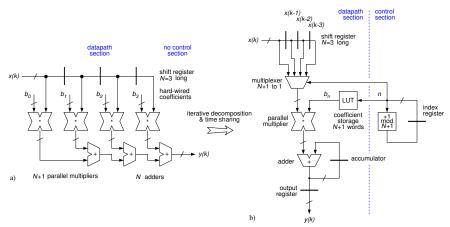

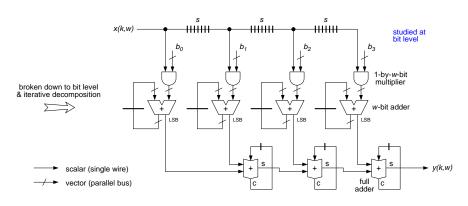

### The isomorphic architecture

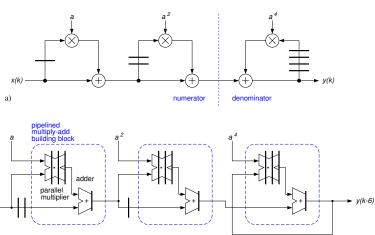

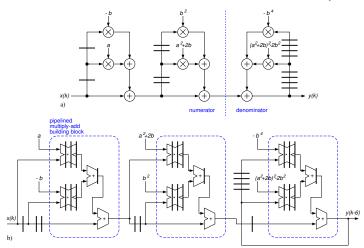

$$y(k) = \sum_{n=0}^{N=3} b_n x(k-n)$$

a)

x(k)  $b_0$   $b_1$   $b_2$   $b_3$  c) y(k)

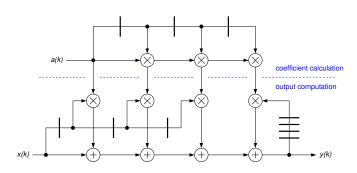

Figure: Example: A third order transversal filter in various notations. Equation (a), DDG (b), and isomorphic architecture (d). SFG for comparison (c).

Relative merits of architectural alternatives

### Figures of merit for hardware architectures I (Perform.-related)

Cycles per data item  $\Gamma$ , number of computation cycles between releasing two subsequent data items.

Longest path delay  $t_{lo}$ , the lapse of time required for data to propagate along the longest path. A circuit cannot function correctly unless  $t_{lp} \leq T_{cp}$

Relative merits of architectural alternatives

### Figures of merit for hardware architectures I (Perform.-related)

Cycles per data item  $\Gamma$ , number of computation cycles between releasing two subsequent data items.

Longest path delay  $t_{lp}$ , the lapse of time required for data to propagate along the longest path. A circuit cannot function correctly unless  $t_{lp} \leq T_{cp}$

Time per data item T, the lapse of time between releasing two subsequent data items, e.g. in  $\mu$ s/sample, ms/frame, or s/computation.  $T = \Gamma \cdot T_{cp} \geq \Gamma \cdot t_{lp}$ .

Data throughput  $\Theta = \frac{1}{\tau} = \frac{f_{cp}}{\Gamma}$  expressed in pixel/s, sample/s, frame/s, record/s, FFT/s, or the like.

There is room for remodeling in the algorithmic domain , and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative merits of architectural alternatives Computation cycle versus clock period

### Figures of merit for hardware architectures I (Perform.-related)

- Cycles per data item  $\Gamma$  , number of computation cycles between releasing two subsequent data items.

- Longest path delay  $t_{lp}$ , the lapse of time required for data to propagate along the longest path. A circuit cannot function correctly unless  $t_{lp} \leq T_{cp}$ .

- Time per data item T, the lapse of time between releasing two subsequent data items, e.g. in  $\mu s/sample$ , ms/frame, or s/computation.  $T = \Gamma \cdot T_{cp} \geq \Gamma \cdot t_{lp}$ .

- Data throughput  $\Theta = \frac{1}{T} = \frac{f_{cp}}{\Gamma}$  expressed in pixel/s, sample/s, frame/s, record/s, FFT/s, or the like.

- Latency L , number of computation cycles from a data item entering a circuit until the pertaining result becomes available.

Relative merits of architectural alternatives

### Figures of merit for hardware architectures II (Cost-related)

Circuit size A expressed in mm<sup>2</sup>,  $F^2$  or GE (gate equivalent).

Size-time product AT, the hardware resources spent to obtain a given throughput.  $AT = \frac{A}{\Box}$ .

Relative merits of architectural alternatives

#### Figures of merit for hardware architectures II (Cost-related)

Circuit size A expressed in mm<sup>2</sup>,  $F^2$  or GE (gate equivalent).

Size-time product AT, the hardware resources spent to obtain a given throughput.  $AT = \frac{A}{\Omega}$ .

Energy per data item E, the amount of energy dissipated for a given computation on a data item e.g. in pJ/MAC, nJ/sample,  $\mu$ J/datablock, or in mWs/frame.

> Can also be understood as power-per-throughput ratio  $E = \frac{P}{\Box}$ measured in  $\frac{mW}{Mbit/s}$  or  $\frac{W}{Gon/s}$ .

because

$$\frac{\text{energy}}{\text{data item}} = \frac{\text{energy per second}}{\text{data item per second}} = \frac{\text{power}}{\text{throughput}}$$

Energy-time product ET indicates how much energy gets spent for achieving a given throughput (synonym "energy-per-throughput ratio").  $ET = \frac{E}{\Theta} = \frac{P}{\Theta^2}$ , e.g. in  $\frac{\mu J}{datablock/s}$  or  $\frac{mWs}{videoframe/s}$ .

There is room for remodeling in the algorithmic domain ... and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative merits of architectural alternatives Computation cycle versus clock period

### Example

#### Approximations

- Interconnect delays neglected (overly optimistic).

- ▶ Delays of arithmetic operations summed up (sometimes pessimistic).

- ▶ Glitching ignored (optimistic).

$$A = 3A_{reg} + 4A_* + 3A_+$$

$$\Gamma = 1$$

$$t_{lp} = t_{reg} + t_* + 3t_+$$

$$AT = (3A_{reg} + 4A_* + 3A_+)(t_{reg} + t_* + 3t_+)$$

$$L = 0$$

$$E = 3E_{reg} + 4E_* + 3E_+$$

There is room for remodeling in the algorithmic domain ... and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative merits of architectural alternatives Computation cycle versus clock period

## A symbolic representation of hardware

Figure: DDG (a), reference hardware configuration (b), key characteristics (c).

Reference hardware = isomorphic architecture + output register(s)

There is room for remodeling in the algorithmic domain ... and there is room in the architectural domain Systems engineers and VLSI designers must collaborate Relative ments of architectural alternatives Computation cycle versus clock period

# Computation cycle versus clock period

- ▶ A computation period  $T_{cp}$  is the time span that separates two consecutive computation cycles.

- ▶ During each computation cycle, fresh data emanate from a register, propagate through combinational circuitry before the result gets stored in the next analogous register.

- ▶ It is the combinational circuitry that performs all arithmetic, logic, and data routing operations.

- ▶ Computation rate  $f_{cp} = \frac{1}{T_{cp}}$  denotes the inverse.

- ► For all circuits that adhere to single-edge-triggered one-phase clocking, computation cycle and clock period are the same.

$$f_{cp} = f_{clk} \quad \Leftrightarrow \quad T_{cp} = T_{clk}$$

The architectural solution space

Dedicated VLSI architectures and how to design them

Equivalence transforms for combinational computations

Options for temporary storage of data

Equivalence transforms for non-recursive computations

Equivalence transforms for recursive computations

Ceneralizations of the transform approach

rative decomposition

pelining

plication

me sharing

sociativity and other algebraic transforms

# Subject

# Transforms for combinational computations

terative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

# What do we mean by combinational computation?

A computation is termed combinational if

- Result depends on the present arguments exclusively.

- All edges in the DDG have weight zero.

- ▶ DDG is free of circular paths.

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Direct

# Darwin stepping off the boat at Galapagos

► Biological evolution has led to great diversity and adaptation. Can we achieve something similar in VLSI architecture design?

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Digest

# Darwin stepping off the boat at Galapagos

- ► Biological evolution has led to great diversity and adaptation. Can we achieve something similar in VLSI architecture design?

- → Let us try with architectural transformations.

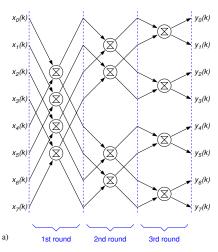

## Example: 8-point FFT

What do you suggest?

If the combinational function f is complex ( $8 \ll n$ -point FFT, AES, JPEG) then the isomorphic architecture is a rather expensive proposition.

lterative decomposition Pipelining Replication Time sharing Associativity and other algebraic transforms

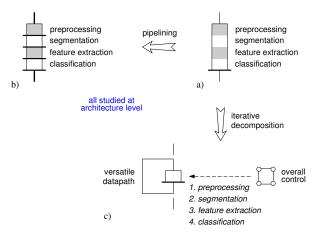

# Options at the architecture level

Decomposing function f into a sequence of subfunctions that get executed one after the other on same hardware.

Pipelining of the functional unit for *f* to improve computation rate by cutting down combinational depth.

Replicating the hardware for f and having all units work concurrently.

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Digest

## Options at the architecture level

Decomposing function f into a sequence of subfunctions that get executed one after the other on same hardware.

Pipelining of the functional unit for *f* to improve computation rate by cutting down combinational depth.

Replicating the hardware for f and having all units work concurrently.

#### Open questions:

- ▶ Does it make sense to combine pipelining with iterative decomposition in spite of their contrarian effects?

- ► How do replication and pipelining compare?

Are there situations where one should be preferred over the other?

## Iterative decomposition

#### Paradigm: Step-by-step execution

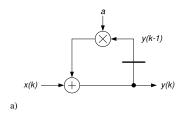

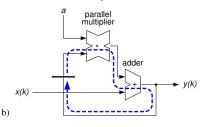

Figure: DDG (a) and hardware configuration for d = 3 (b).

Iterative decomposition

## Performance and cost analysis

As a first-order approximation, iterative decomposition by a factor of d leads to the following figures of merit:

$$rac{A_f}{d} + A_{reg} + A_{ctl} \leq A(d) \leq A_f + A_{reg} + A_{ctl}$$

$\Gamma(d) = d$

$t_{lp}(d) pprox rac{t_f}{d} + t_{reg}$

$d(A_{reg} + A_{ctl})t_{reg} + (A_{reg} + A_{ctl})t_f + A_f t_{reg} + rac{1}{d}A_f t_f$

$\leq AT(d) \leq$

$d(A_f + A_{reg} + A_{ctl})t_{reg} + (A_f + A_{reg} + A_{ctl})t_f$

$L(d) = d$

$E(d) \geqslant E_f + E_{reg}$

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Direct

# Insight gained

#### Iterative decomposition

▶ Is attractive when a computation makes repetitive use of a single subfunction because a lot of area can then be saved.

Example: multiplication → repeated shift & add operations

▶ Is unattractive when subfunctions are very disparate and, therefore, cannot be made to share much hardware resources.

Example: square root, logarithm, multiplication modulo some prime

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Dijeest

# Insight gained

#### Iterative decomposition

- ▶ Is attractive when a computation makes repetitive use of a single subfunction because a lot of area can then be saved.

- Example: multiplication → repeated shift & add operations

- Is unattractive when subfunctions are very disparate and, therefore, cannot be made to share much hardware resources.

- Example: square root, logarithm, multiplication modulo some prime

- ▶ Does not impact throughput much as long as  $t_{reg} \ll t_{lp}$ .

- May or may not improve energy efficiency.

- yes, if cutting overly long signal propagation paths mitigates excessive glitching and the associated energy losses.

- no, if the extra activity of data registers, control logic, and data recycling circuitry dominates.

Iterative decomposition

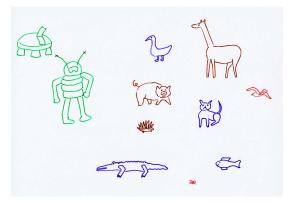

## Example: block cipher IDEA

bitwise addition modulo 2

addition modulo 2<sup>16</sup>

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic tra

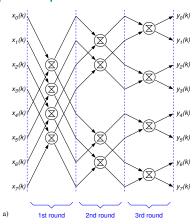

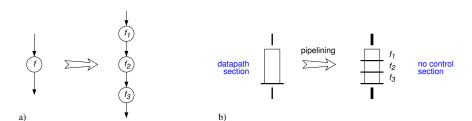

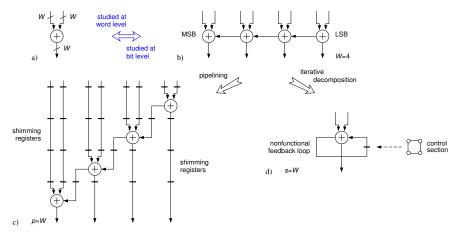

# **Pipelining**

Paradigm: Assembly line operated by specialized workers

Figure: DDG (a) and hardware configuration for p = 3 (b).

Generalizations of the transform approach

**Pipelining**

## Performance and cost analysis

Pipelining by a factor of p changes performance and cost figures as follows

$$egin{aligned} A(p) &= A_f + p A_{reg} \ \Gamma(p) &= 1 \ \ t_{lp}(p) &pprox rac{t_f}{p} + t_{reg} \ AT(p) &pprox p A_{reg} t_{reg} + (A_{reg} t_f + A_f t_{reg}) + rac{1}{p} A_f t_f \ L(p) &= p \ E(p) &pprox left reg rain \ pprox left F_f + E_{reg} \end{aligned}$$

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transform

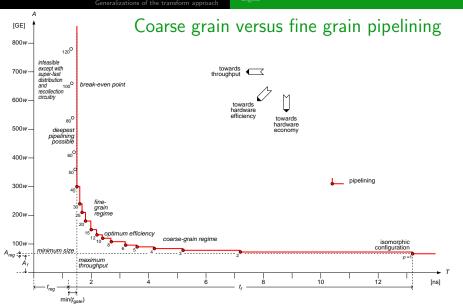

# Insight gained

Must distinguish between two regimes of pipelining:

Coarse grain pipelining.

Few registers evenly inserted into a deep combinational network.

- + Little extra area for much better throughput.

- + AT-product lowered dramatically.

- + Long reconvergent fanout paths cut → reduced glitching.

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Digest

# Insight gained

Must distinguish between two regimes of pipelining:

Coarse grain pipelining.

Few registers evenly inserted into a deep combinational network.

- + Little extra area for much better throughput.

- + AT-product lowered dramatically.

- + Long reconvergent fanout paths cut → reduced glitching.

Fine grain pipelining.

Combinational delay in each stage approaches register delay.

- $\sim\,$  Diminishing speedup for more and more overhead.

- AT-product augments significantly.

- Significant register activity added → waste of energy.

- More exposed to OCV.

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic trans

### Theoretical bound

- ▶ Pipeline stage must accomodate at least one 2-input NAND or NOR.

- → Computation rate and clock frequency are bounded.

$$T_{cp} \geq \min(t_{lp}) = \min(t_{gate}) + t_{reg} = \min(t_{nand}, t_{nor}) + t_{su\,ff} + t_{pd\,ff}$$

#### Numerical example:

- Standard cell library for a 130 nm CMOS process.

- Computation period bounded from below to

$$T_{cp} \geq t_{\mathsf{NAN2D1}} + t_{\mathsf{DFFPB1}} = 18 \ \mathsf{ps} + 249 \ \mathsf{ps} pprox 267 \ \mathsf{ps}$$

$\rightsquigarrow$  Absolute maximum computation rate  $\approx 3.7$  GHz.

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic tra

# A glance at microprocessors I

| _                  |      |          |                     |

|--------------------|------|----------|---------------------|

|                    | year | clock    | FO4 inverter delays |

| CPU                |      | [MHz]    | per pipeline stage  |

| Intel 80386        | 1989 | 33       | ≈ 80                |

| Intel Pentium 4    | 2003 | 3200     | 1216                |

| Core 2 Duo         | 2007 | 2167     | ≈ 40                |

| Core i7 980X       | 2011 | 33333600 | 4246                |

| IBM POWER5         | 2004 | 16501900 | 22                  |

| IBM POWER6         | 2007 | 35005000 | 13                  |

| IBM Cell Processor | 2006 | 3200     | 11                  |

FO4 = fanout 4

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic trans

# A glance at microprocessors I

|                    | year | clock    | FO4 inverter delays |

|--------------------|------|----------|---------------------|

| CPU                |      | [MHz]    | per pipeline stage  |

| Intel 80386        | 1989 | 33       | ≈ 80                |

| Intel Pentium 4    | 2003 | 3200     | 1216                |

| Core 2 Duo         | 2007 | 2167     | ≈ 40                |

| Core i7 980X       | 2011 | 33333600 | 4246                |

| IBM POWER5         | 2004 | 16501900 | 22                  |

| IBM POWER6         | 2007 | 35005000 | 13                  |

| IBM Cell Processor | 2006 | 3200     | 11                  |

FO4 = fanout 4

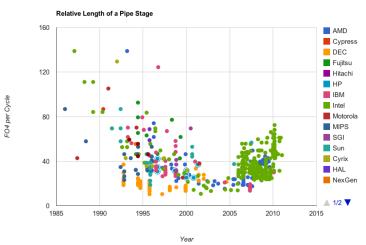

#### Observations

- ▶ Pipelining has been instrumental in pushing processor clock frequencies.

- ▶ 12 or so FO4 inverter delays per stage is close to practical limit.

- ► Trend towards ever deeper pipelines reversed in the Intel Core family to reclaim energy efficiency.

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transform

# A glance at microprocessors II

Figure: Evolution of pipeline depth over the years (source Stanford CPU database).

```

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

```

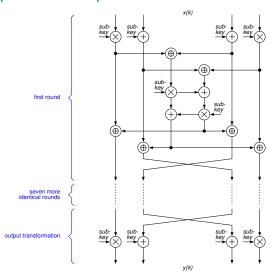

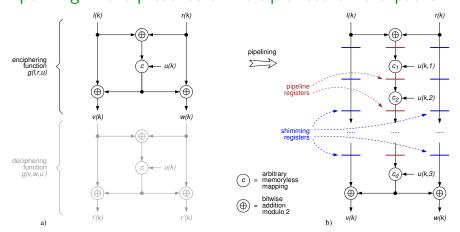

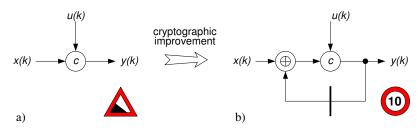

# Pipelining in the presence of multiple feedforward paths

Figure: Involutory cipher algorithm. DDG before (a) and after pipelining (b).

Replication

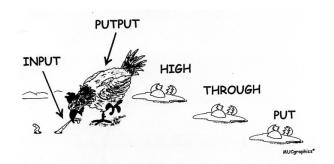

# A brute force approach to performance I

Figure: If one functional unit does not meet your performance goals ...

What can you do?

## A brute force approach to performance II

Figure: ... try to get more of them.

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transform

### Replication

#### Paradigm: Multi-piston pump

Figure: DDG (a) and hardware configuration for q = 3 (b).

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Digest

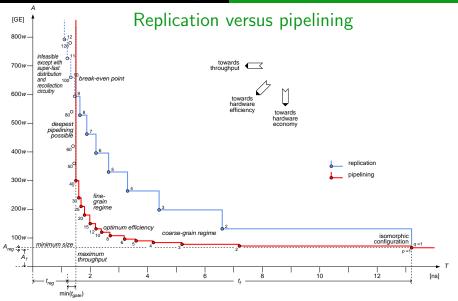

## Performance and cost analysis

The key characteristics of replication by a factor of q are

$$egin{align} A(q) &= q(A_f + A_{reg}) + A_{ctl} \ &\Gamma(q) = rac{1}{q} \ &t_{lp}(q) pprox t_f + t_{reg} \ &AT(q) pprox (A_f + A_{reg} + rac{1}{q} A_{ctl})(t_f + t_{reg}) pprox (A_f + A_{reg})(t_f + t_{reg}) \ &L(q) = 1 \ &E(q) pprox E_f + E_{reg} + E_{ctl} \ & \end{array}$$

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Digest

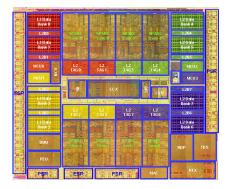

# Example: Microprocessor architectures I

- ightharpoonup Superscalar  $\mapsto$  multiple ALUs, FPUs, etc. under common control.

- ► Multicore → multiple processor cores working independently.

Figure: Floorplan of a Sun Microsystems UltraSPARC T2 CPU (Niagara 2) that combines 8 cores on a single die (separate integer and floating point units in each core, 8 threads/core, 1831 pins, 65 nm CMOS, 342 mm<sup>2</sup>, 1.4 GHz).

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Digest

# Example: Microprocessor architectures II

#### Computer industry has been pushed towards replication because

- ► CMOS offered more room for increasing circuit complexity than for pushing clock frequencies higher.

- ► The faster the clock, the smaller the region on a semiconductor die that can be reached within a single clock period.

- Fine grain pipelines dissipate a lot of energy for relatively little computation.

- Reusing a well-tried subsystem benefits design productivity and lowers risks.

- A multicore processor can still be of commercial value even if one of its CPUs is found to be defective

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic tran

### Time sharing

► Many applications ask for the simultaneous processing of multiple parallel data streams.

Paradigm: Student sharing his time between various subjects

Figure: DDG (a) and hardware configuration for s = 3 (b).

Iterative decomposition

Pipelining

Replication

There sharing

Associativity and other alreby

Associativity and other algebraic transforn Digest

## Performance and cost analysis

Time sharing by a factor of s yields the following picture

$$\max_{f,g,h}(A) + A_{reg} + A_{ctl} \leq A(s) \leq \sum_{f,g,h} A + A_{reg} + A_{ctl}$$

$$\Gamma(s) = s$$

$$t_{lp}(s) \approx \max_{f,g,h}(t) + t_{reg}$$

$$s(\max_{f,g,h}(A) + A_{reg} + A_{ctl})(\max_{f,g,h}(t) + t_{reg}) \leq AT(s) \leq$$

$$s(\sum_{f,g,h} A + A_{reg} + A_{ctl})(\max_{f,g,h}(t) + t_{reg})$$

$$L(s) = s$$

$$E(s) \approx s \max_{f,g,h}(E) + E_{reg} + E_{ctl}$$

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transfor

# Insight gained

#### Time sharing

- ▶ is most favorable when one monofunctional datapath proves sufficient because all streams are to be processed in exactly the same way

- ▶ is unattractive when subfunctions are very disparate because no savings can be obtained from concentrating their processing into one multifunctional datapath

- refrains from taking advantage of the parallelism inherent in the original problem

- may be viewed as antithetic to replication

lterative decomposition Pipelining Replication

Time sharing

sociativity and other algebraic transforms

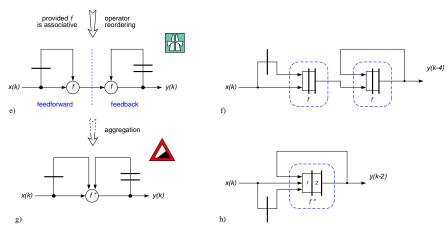

# Example: 8-point FFT

DDG of 8-point FFT (a) and DDG of butterfly operator (b).

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transf

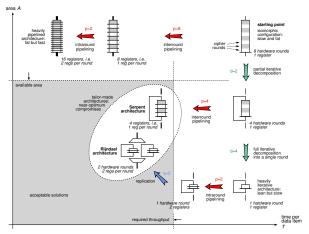

#### size A A roadmap for tailoring combinational hardware actual effect replication towards throughput pipelining iterative decomposition time sharing towards hardware efficiency towards hardware 1/3 economy 1/9

```

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic

```

## Example: Two cryptochip architectures compared

Figure: Two competing teams have taken different routes but have arrived at similar compromises between throughput and area (ETH CHES 2002).

Associativity and other algebraic transforms

## Universal versus algebraic transforms

Universal transforms. Whether and how to apply them can be decided from the DDG alone, no matter what operations the vertices stand for.

- Iterative decomposition

- Pipelining

- Replication

- Time sharing

more to follow later in this chapter

Associativity and other algebraic transforms

## Universal versus algebraic transforms

Universal transforms. Whether and how to apply them can be decided from the DDG alone, no matter what operations the vertices stand for.

- Iterative decomposition

- Pipelining

- Replication

- Time sharing

more to follow later in this chapter

Algebraic transforms. Take advantage of specific algebraic properties of the operations involved.

- Associativity transform, commutativity transform

- ► Horner's scheme (for evaluating polynomials)

- Method of finite differences (to calculate equidistant values)

- Karatsuba multiplication (for wide data words)

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

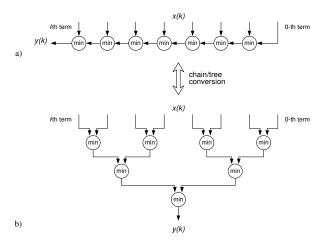

## Example: Associativity transform

Figure: 8-way minimum function. Chain-type DDG (a), tree-type DDG (b).

Iterative decomposition

Pipelining

Replication

Time sharing

Associativity and other algebraic transforms

Digest

## Recapitulation

### Equivalence transforms that help optimize combinational computations

Iterative decomposition. Pipelining. Replication. Algebraic transforms. Time sharing (in the presence of parallel data streams).

- ▶ Iterative decomposition and time sharing are most effective when a computational unit can be reused several times.

- Pipelining is generally superior to replication.

Coarse grain pipelining improves throughput dramatically, but benefits decline as more and more stages are included.

- Pipelining and iterative decomposition are complementary, they both can contribute to lowering the AT product.

- ▶ Lowering AT always implies cutting down the longest path  $t_{lp}$ .

The architectural solution space

Dedicated VLSI architectures and how to design them

Equivalence transforms for combinational computations

Options for temporary storage of data

Equivalence transforms for non-recursive computations

Equivalence transforms for recursive computations

Generalizations of the transform approach

Data access patterns Available memory configurations and area occupatior Wiring and the costs of going off-chip Digest

## Subject

# Options for temporary storage of data

## Why and when do we need to stora data?

Except for trivial SSI/MSI circuits, any IC includes some form of memory.

#### This is either because

the data processing algorithm is of sequential nature and, therefore, asks for functional memory,

#### or because

nonfunctional storage got introduced into the circuit as a consequence from architectural transformations.

## Options for temporary storage of data

Architectural options for temporary storage of data:

- o On-chip registers built from individual flip-flops or latches.

- o On-chip memory i.e. SRAM macrocell (or possibly embedded DRAM).

- o Off-chip memory i.e. SRAM or DRAM catalog part.

## Options for temporary storage of data

Architectural options for temporary storage of data:

- o On-chip registers built from individual flip-flops or latches.

- o On-chip memory i.e. SRAM macrocell (or possibly embedded DRAM).

- o Off-chip memory i.e. SRAM or DRAM catalog part.

#### Differences that impact high-level design decisions:

- ▶ One-at-a-time versus all-at-a-time data access patterns

- ► Available memory configurations and area occupation

- Storage capacities

- ▶ Wiring and the costs of going off-chip

- Energy efficiency

- ► Latency and timing

## Data access patterns

RAMs impose access one data word after the other

Fine in architectures obtained from

- iterative decomposition and

- time sharing.

Perfect match for microprocessors

```

("fetch, load, execute, store").

```

Registers allow for simultaneous access to all data words stored

Mandatory in high-throughput architectures obtained from

- pipelining,

- retiming, to be introduced later in this chapter

- ▶ loop unfolding idem

where data are kept moving in every computation cycle.

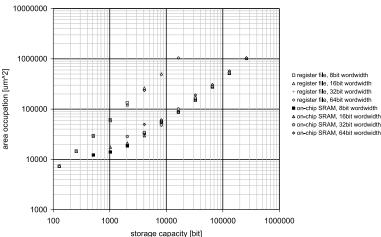

## Available memory configurations

Figure: Area occupation of registers and on-chip RAMs for a 130 nm CMOS.

# Wiring and the costs of going off-chip

Off-chip memories add to pin count, package count, and board space.

- Extra parasitic capacitances

- Extra delays

- Extra energy dissipation

# Wiring and the costs of going off-chip

Off-chip memories add to pin count, package count, and board space.

- Extra parasitic capacitances

- Extra delays

- ► Extra energy dissipation

- ► Commodity RAMs impose bidirectional pads → special attention required

- ► Stationary and transient drive conflicts must be avoided.

- ATE must be made to alternate between read and write modes with no physical access to any control signal within the chip.

- Test patterns must address bidirectional operation and high-impedance states.

- ► Electrical and timing measurements become more complicated.

#### Conclusion

Off-chip data storage is associated with important penalties.

# Options for temporary data storage compared

| on-chip                  |                                                             |                                                                                    |                                                        | off-chip                                               |

|--------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| bistables                |                                                             | embedded                                                                           |                                                        | commodity                                              |

| flip-flop                | latch                                                       | SRAM                                                                               | DRAM                                                   | DRAM                                                   |

| compatible with logic    |                                                             |                                                                                    | optimized                                              |                                                        |

| 2030T                    | 1216T                                                       | 6T                                                                                 | 1T1C                                                   | 1T1C                                                   |

| 17002800                 | 11001800                                                    | 135170                                                                             | 1830*                                                  | 68                                                     |

| none                     |                                                             | $1.3 \leq factor \leq 2$                                                           |                                                        | off-chip                                               |

|                          | none                                                        |                                                                                    |                                                        | y e s                                                  |

| none                     |                                                             | none                                                                               |                                                        | addr. & data bus                                       |

| multitude of local lines |                                                             | on-chip busses                                                                     |                                                        | package & board                                        |

| none                     |                                                             | optional                                                                           |                                                        | mandatory                                              |

| all at a time            |                                                             | one at a                                                                           |                                                        | time                                                   |

| any                      |                                                             | restric                                                                            |                                                        | ted                                                    |

| good                     |                                                             | fair                                                                               | poor                                                   | very poor                                              |

| none                     |                                                             | no fixed rules                                                                     |                                                        | yes                                                    |

| minor                    |                                                             | substantial                                                                        |                                                        | severe                                                 |

|                          | flip-flop  2030T  17002800  no  multitude of no  all at ago | bistables flip-flop   latch  compatible w 2030T   1216T  17002800   11001800  none | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

<sup>\*</sup> As low as 6...8 for processes that accomodate 3D capacitors (4 to 6 extra masks)

## Example: RAMs in a CMOS ASIC technology

Cu-11 is an ASIC technology by IBM (2002)

- ▶ gate length 110 nm, supply voltage 1.2 V

- Cu interconnect combined with low-k interlevel dielectrics.

#### **SRAM**

macrocell generator from 128 bit to 1 Mibit

Embedded DRAM megacells up to 16 Mibit (with trench caps)

- ► cycle time of 1 Mibit eDRAM is 15 ns (equivalent to 555 · t<sub>pd</sub> of a 2-input NAND)

- ightharpoonup eDRAM bit cell area is 0.31  $\mu$ m<sup>2</sup>

- ▶ 1 Mibit eDRAM occupies an area of 2.09 mm² (84% overhead)

- ▶ 16 Mibit eDRAM occupies 14.1 mm² (63% overhead)

## Recapitulation

#### Observation

There is no such thing as an optimal solution for temporary storage of data, what is best strongly depends on the situation and requirements.

- ▶ Only registers allow for simultaneous access to all data, but occupy a lot of die area per bit.

- ► SRAMs can hold more significant quantities of data than registers but are slower than registers, yet faster than DRAMs.

- ▶ DRAMs require periodical refresh → power dissipated even when idle.

- ▶ DRAM and Flash memories are cost-efficient for large data quantities.

- ▶ Flash is used for permanent storage, but is much slower than RAM.

- Commodity memories offer virtually unlimited capacities at low costs, but are is associated with speed, energy and other penalties.

Retiming Pipelining revisited Iterative decomposition and time sharing revisite Digest

# Subject

# Transforms for non-recursive computations

## What do we mean by non-recursive computation?

A computation is termed (sequential and) non-recursive if

- ▶ Result is dependent on past arguments, not just present.

- ▶ Edges with weights greater than zero are present in the DDG.

- ▶ DDG is free of circular paths.

### Example: Nonlinear time-invariant third order correlator

▶ Pipelining helps boost throughput but is rather inefficient in this case.

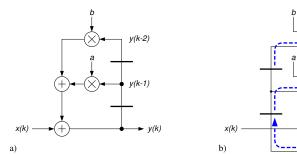

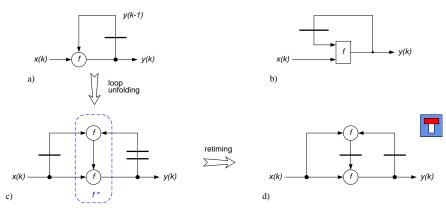

## Retiming

Paradigm: Repartition workloads evenly for all workers on an assembly line

Figure: DDG (a) and hardware configuration for l = 1 (b).

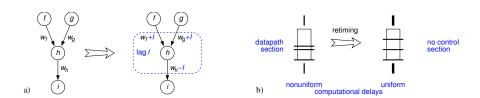

### Formal rules

To be legal, any retiming must observe the following rules:

- 1. Neither outputs nor sources of time-varying inputs may be part of a supervertex that is to be retimed.

- 2. When a supervertex is assigned a lag (lead) by *I* computation cycles, the weights of all its incoming edges are in- (de-)cremented by *I* and the weights of all its outgoing edges are de- (in-)cremented by *I*.

- 3. No edge weight may be changed to assume a negative value.

- 4. Any circular path must always include at least one edge of strictly positive weight (roundtrip weights will never change).

Retiming Pipelining revisited Iterative decomposition and time sharing revisite Digest

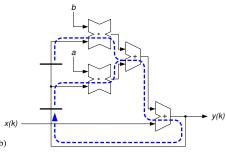

# Pipelining revisited

#### Same rules as for retiming except

1. Any supervertex to be assigned a lag (lead) must include all outputs (all time-varying inputs).

# Pipelining revisited

#### Same rules as for retiming except

1. Any supervertex to be assigned a lag (lead) must include all outputs (all time-varying inputs).

#### Comparison

- ▶ Both transforms aim at shortening the longest path.

- Pipelining increases latency as registers get added.

- ▶ Retiming leaves latency unchanged as registers get relocated.

Retiming

Pipelining revisited

Iterative decomposition and time sharing revisited

Digest

Example: Nonlinear timeinvariant third order correlator

### Example: Nonlinear time-invariant third order correlator

The subsequent transforms change the circuit's performance as follows:

|                             | Architectural variant   |          |                       |                            |  |

|-----------------------------|-------------------------|----------|-----------------------|----------------------------|--|

|                             | original                | reversed | + retimed             | + pipelined                |  |

| Key characteristics         | (a)                     | (b)      | (c)                   | (d)                        |  |

| arithmetic units            | $(N+1)A_h + NA_+$       | idem     | idem                  | idem                       |  |

| functional registers        | NA <sub>reg</sub>       | idem     | idem                  | idem                       |  |

| nonfunctional registers     | 0                       | idem     | idem                  | $(N+1)A_{reg}$             |  |

| cycles per data item Γ      | 1                       | idem     | idem                  | idem                       |  |

| longest path delay $t_{lp}$ | $t_{reg} + t_h + N t_+$ | idem     | $t_{reg} + t_h + t_+$ | $t_{reg} + \max(t_h, t_+)$ |  |

| for $N=3$ [ns]              | 9.5                     | idem     | 5.5                   | 3.5                        |  |

| for $N = 30$ [ns]           | 63.5                    | idem     | 5.5                   | 3.5                        |  |

| latency L                   | 0                       | idem     | idem                  | 1                          |  |

### Example: Nonlinear time-invariant third order correlator

The subsequent transforms change the circuit's performance as follows:

|                             | Architectural variant   |          |                       |                            |  |

|-----------------------------|-------------------------|----------|-----------------------|----------------------------|--|

|                             | original                | reversed | + retimed             | + pipelined                |  |

| Key characteristics         | (a)                     | (b)      | (c)                   | (d)                        |  |

| arithmetic units            | $(N+1)A_h + NA_+$       | idem     | idem                  | idem                       |  |

| functional registers        | NA <sub>reg</sub>       | idem     | idem                  | idem                       |  |

| nonfunctional registers     | 0                       | idem     | idem                  | $(N+1)A_{reg}$             |  |

| cycles per data item Γ      | 1                       | idem     | idem                  | idem                       |  |

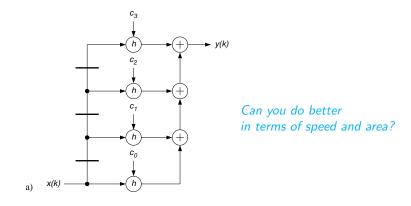

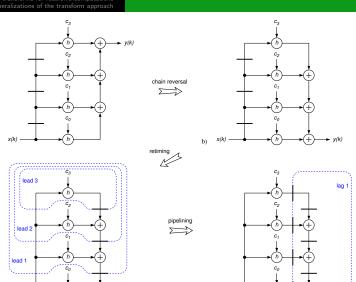

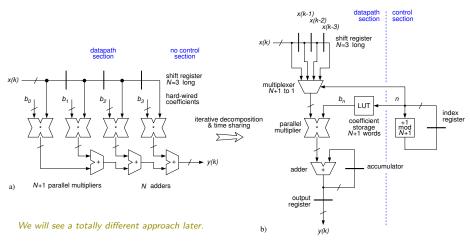

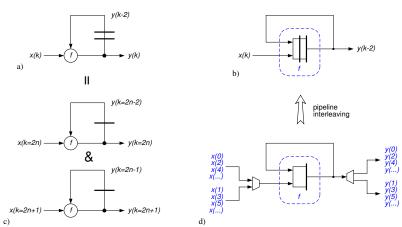

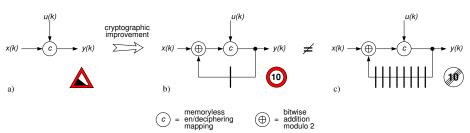

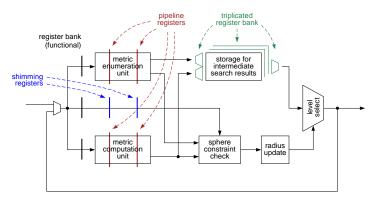

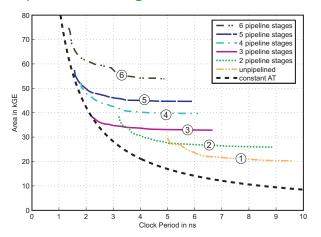

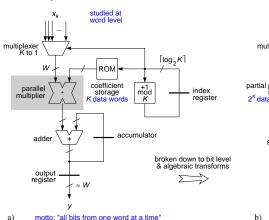

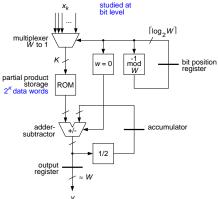

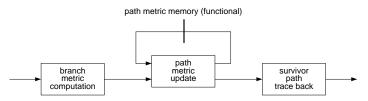

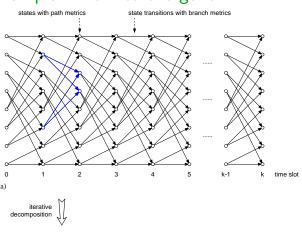

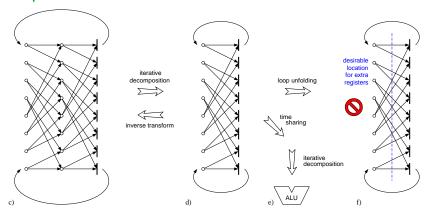

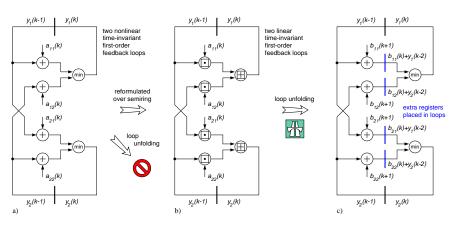

| longest path delay $t_{lp}$ | $t_{reg} + t_h + N t_+$ | idem     | $t_{reg} + t_h + t_+$ | $t_{reg} + \max(t_h, t_+)$ |  |