# SYSTEM SPECIFICATIONS USING VERILOG HDL

Dr. Mohammed M. Farag

Faculty of Engineering Alexandria University

### Outline

- Introduction

- Basic Concepts

- Modules and Ports

- Gate-Level Modeling

- Dataflow Modeling

- Behavioral Modeling

- Tasks and Functions

Textbook:Verilog HDL:A Guide to Digital Design and Synthesis, Second Edition By Samir Palnitkar

### Introduction

2014

### Hardware Description Language

- Better be standard than be proprietary

- Can describe a design at some levels of abstraction

- Can be interpreted at many level of abstraction

- Cross functional, statistical behavioral, multi-cycles behavioral, RTL

- Can be used to document the complete system design tasks

- Testing, simulation, ..., related activities

- User define types, functions and packages

- Comprehensive and easy to learn

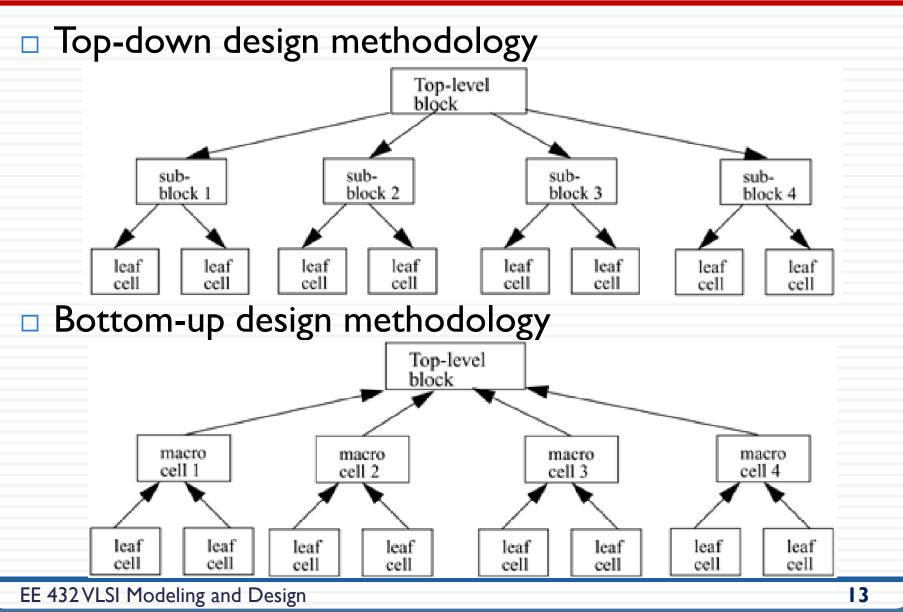

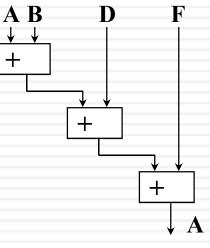

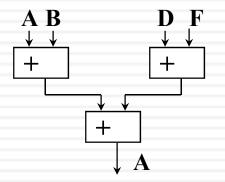

## Design Methodologies

- Top-Down Design

- Start with system specification

- Decompose into subsystems, components, until indivisible

- Realize the components

- Bottom-up Design

- Start with available building blocks

- Interconnect building blocks into subsystems, then system

- Achieve a system with desired specification

- Meet in the middle

- A combination of both

### Importance of HDLs

- Designs can be described at very abstract levels without predefining the fabrication technology

- Functional verification of the design can be done early in the design cycle

- Designers can optimize and modify the RTL description until it meets the desired functionality

- Designing with HDLs is analogous to computer programming

- With rapidly increasing complexities of digital circuits and increasingly sophisticated EDA tools, HDLs are now the dominant method for large digital designs

# Verilog History

- Gateway Design Automation

Phil Moorbr in 1984 and 1985

- Verilog-XL, "XL algorithm", 1986

- Gate-level simulation

- Verilog logic synthesizer, Synopsis, 1988

- Top-down design methodology

- Cadence Design Systems acquired Gateway

- December 1989

- □ a proprietary HDL

# Verilog History

Open Verilog International (OVI), 1991

```

Language Reference Manual (LRM)

```

- The IEEE 1364 working group, 1994

- Verilog become an IEEE standard (1364-1995)

- December, 1995

- 2001, IEEE standard 1364-2001

# Popularity of Verilog HDL

- Verilog HDL is a general-purpose hardware description language that is easy to learn and easy to use

- □ It is similar in syntax to the C programming language

- Verilog HDL allows different levels of abstraction to be mixed in the same model

- Most popular logic synthesis tools support Verilog HDL

- All fabrication vendors provide Verilog HDL libraries for post logic synthesis simulation

- The Programming Language Interface (PLI) is a powerful feature that allows the user to write custom C code to interact with the internal data structures of Verilog

# Trends in HDLs

- The speed and complexity of digital circuits have increased rapidly

- Designers have responded by designing at higher levels of abstraction

- Designers have to think only in terms of functionality.

- EDA tools take care of the implementation details and optimization

- The most popular trend currently is to design in HDL at an RTL level, because logic synthesis tools can create gate-level netlists from RTL level design

# Trends in HDLs (2)

- Behavioral synthesis allowed engineers to design directly in terms of algorithms and the behavior of the circuit

- However, behavioral synthesis did not gain widespread acceptance

- Today, RTL design continues to be very popular

- Designers often mix gate-level description directly into the RTL description to achieve optimum results

- Another technique that is used for system-level design is a mixed bottom-up methodology

# Hierarchical Modeling Concepts

# **Design Methodologies**

# Design Methodologies (2)

- Typically, a combination of top-down and bottom-up flows is used

- Design architects define the specifications of the top-level block

- Logic designers decide how the design should be structured by breaking up the functionality into blocks and sub-blocks

- At the same time, circuit designers are designing optimized circuits for leaf-level cells

- The flow meets at an intermediate point

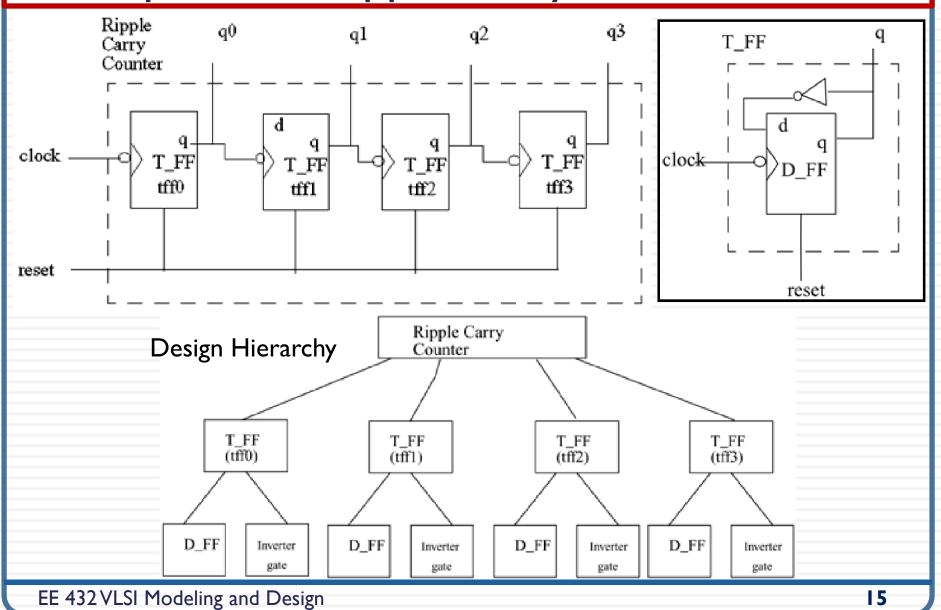

### **Example: 4-bit Ripple Carry Counter**

### Modules

- A module is the basic building block in Verilog

- A module can be an element or a collection of lower-level design blocks

- Typically, elements are grouped into modules to provide common functionality that is used at many places in the design

- A module provides the necessary functionality to the higher-level block through its port interface, but hides the internal implementation

- This allows the designer to modify module internals without affecting the rest of the design

# Module Declaration

- In Verilog, a module is declared by the keyword module

- In Verilog, a module is declared by the keyword module

- Each module must have a module\_name, which is the identifier for the module, and a module\_terminal\_list, which describes the input and output terminals of the module

```

module <module_name> (<module_terminal_list>);

```

```

<module internals>

```

#### endmodule

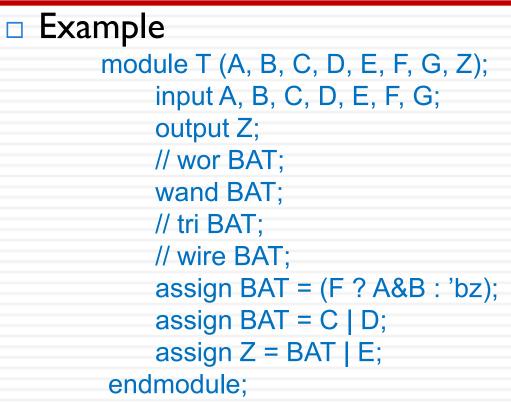

Example

# The T-flip flop could be defined as a module as follows

```

module T_FF (q, clock, reset);

```

```

<functionality of T-flipflop>

```

endmodule

# Verilog Abstraction Levels

- Verilog is both a behavioral and a structural language

- Internals of each module can be defined at four levels of abstraction, depending on the needs of the design include

- Behavioral or algorithmic level:

- This is the highest level of abstraction provided by Verilog HDL (similar to C programming)

- A module can be implemented in terms of the desired design algorithm without concern for the hardware implementation details

# Verilog Abstraction Levels (2)

- Dataflow level

- The module is designed by specifying the data flow

- The designer is aware of how data flows between hardware registers and how the data is processed in the design

- Gate level

- The module is implemented in terms of logic gates and interconnections between these gates

- Design at this level is similar to describing a logic design

#### Switch level

- This is the lowest level of abstraction provided by Verilog

- A module can be implemented in terms of switches, storage nodes, and the interconnections between them

# Verilog Abstraction Levels (3)

- Verilog allows the designer to mix and match all four levels of abstractions in a design

- The term register transfer level (RTL) is frequently used for a Verilog description that uses a combination of behavioral and dataflow constructs

- Normally, the higher the level of abstraction, the more flexible and technology-independent the design

- However, at this level, the designer does not have the control over low-level details which are automatically generated by the synthesis tool

# Mixing Structure and Behavior

**module** *module\_name* (port\_list); **Declarations:** Net declarations. Reg declarations. Parameter declarations. Initial statements. Gate instantiation statements. Module instantiation statements. UDP instantiation statements. Always statements. Continuous assignment. endmodule

22

2014

#### Instances

- A module provides a template from which you can create actual objects

- Verilog creates a unique object from the template when a module is invoked

- The process of creating objects from a module template is called instantiation, and the objects are called instances

- In Verilog, it is illegal to nest modules

- One module definition cannot contain another module definition within the module and endmodule statements

- Instead, a module definition can incorporate copies of other modules by instantiating them

### Example-I

// Define the top-level module called ripple carry// counter. It instantiates 4 T-flipflops. Interconnections are// shown in Section 2.2, 4-bit Ripple Carry Counter.

module ripple\_carry\_counter(q, clk, reset); output [3:0] q; //I/O signals and vector declarations //will be explained later. input clk, reset; //I/O signals will be explained later. //Four instances of the module T FF are created. Each has a unique //name.Each instance is passed a set of signals. Notice, that //each instance is a copy of the module T FF. T FF tff0(q[0],clk, reset); T\_FF tff1(q[1],q[0], reset); T FF tff2(q[2],q[1], reset); T FF tff3(q[3],q[2], reset); endmodule

### Example-2

// Define the module T FF. It instantiates a D-flipflop. We assumed // that module D-flipflop is defined elsewhere in the design. Refer // to Figure 2-4 for interconnections. module T FF(q, clk, reset); //Declarations to be explained later output q; input clk, reset; wire d; D FF dff0(q, d, clk, reset); // Instantiate D FF. Call it dff0. not n1(d, q); // not gate is a Verilog primitive. Explained later. endmodule

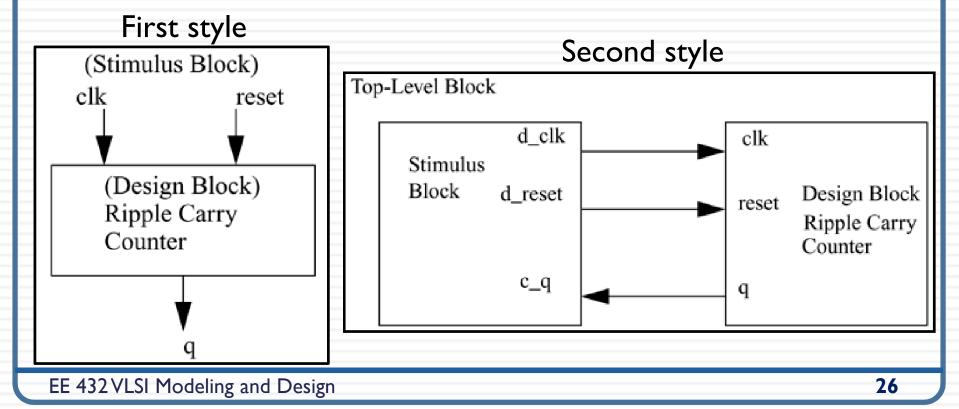

# **Components of Simulation**

- The functionality of the design block can be tested by applying stimulus and checking results

- We call such a block the stimulus block or a test bench

- Two styles of stimulus application are possible

# Example

Ripple Carry Counter

Top Block

module ripple\_carry\_counter(q, clk,

reset);

output [3:0] q; input clk, reset; //4 instances of the module T\_FF are created. T\_FF tff0(q[0],clk, reset); T\_FF tff1(q[1],q[0], reset); T\_FF tff2(q[2],q[1], reset); T\_FF tff3(q[3],q[2], reset); endmodule

# Flipflop T\_FF

module T FF(q, clk, reset); output q; input clk, reset; wire d; D FF dff0(q, d, clk, reset); not n1(d, q); /\* not is a Verilog-provided primitive. case sensitive\*/ endmodule

# Example (2)

// module D FF with synchronous reset module D FF(q, d, clk, reset); output q; input d, clk, reset; reg q; // Lots of new constructs. Ignore the functionality of the // constructs. // Concentrate on how the design block is built in a top-down fashion. always @(posedge reset or negedge clk) if (reset) q <= 1'b0; else

#### endmodule

EE 432 VLSI Modeling and Design

28

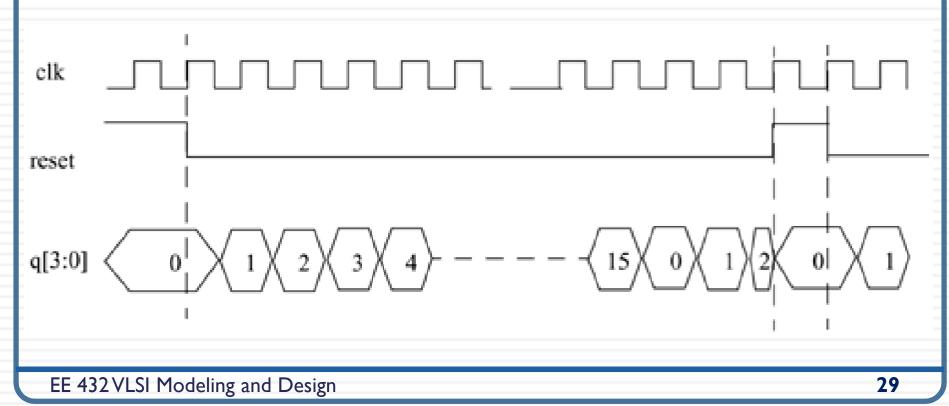

# Example (3)

- Stimulus Block

- We control the signals clk and reset so that the regular function of the ripple carry counter

- Waveforms for clk, reset, and 4-bit output q are shown

# Example: Stimulus Block

module stimulus; reg clk; reg reset; wire[3:0] q; // instantiate the design block ripple\_carry\_counter r1(q, clk, reset); // Control the clk signal that drives the //design block. Cycle time = 10 initial clk = 1'b0; //set clk to 0 always #5 clk = ~clk; //toggle clk every 5 time units

/\* Control the reset signal that drives the design block \*/ initial begin reset = 1'b1; #15 reset = 1'b0; #180 reset = 1'b1; #10 reset = 1'b0; #20 \$finish; //terminate the //simulation end // Monitor the outputs initial \$monitor(\$time, " Output q = %d", q); endmodule

# Basic Concepts

# Basics

- Free format

- Case sensitive

- white space (blank, tab, newline) can be used freely

- - symbol RI2 3\$

- \_R2

- Escaped identifiers: starts with a \ (backslash) and end with white space

- \7400 \.\*.\$ .{\*} \~Q

Keywords: Cannot be used as identifiers E.g. initial, assign, module

#### Basics (Contd) Comments: Two forms /\* First form: cam extend over many lines \*/ // Second form: ends at the end of this line \$SystemTask / \$SystemFunction **\$time \$monitor** Compiler-directive: directive remains in effect through the rest of compilation. // Text substitution 'define MAX BUS SIZE 32

```

reg['MAX_BUS_SIZE-1:0] ADDRESS;

```

# Lexical Conventions

- Whitespace

- Blank spaces (\b), tabs (\t) and newlines (\n) comprise the whitespace

- Whitespace is ignored by Verilog except when it separates tokens

- Whitespace is not ignored in strings

- Comments

- Comments can be inserted in the code for readability and documentation

- There are two ways to write comments

- A one-line comment starts with "//"

- A multiple-line comment starts with "/\*" and ends with "\*/"

# Lexical Conventions (2)

Comment examples

a = b && c; // This is a one-line comment /\* This is a multiple line comment \*/

/\* This is /\* an illegal \*/ comment \*/

/\* This is //a legal comment \*/

Operators

a = ~ b; // ~ is a unary operator. b is the operand a = b && c; // && is a binary operator. b and c are operands

a = b ? c : d; // ?: is a ternary operator. b, c and d are operands

### Number Specification

- There are two types of number specification in Verilog: sized and unsized

- Sized numbers <size> '<base format> <number> 4'b1111 // This is a 4-bit binary number 12'habc // This is a 12-bit hexadecimal number 16'd255 // This is a 16-bit decimal number Unsized numbers: Decimal numbers with a default size 23456 // This is a 32-bit decimal number by default 'hc3 // This is a 32-bit hexadecimal number 'o21 // This is a 32-bit octal number

## Number Specification

- Negative numbers

- Negative numbers can be specified by putting a minus sign before the size for a constant number

- -6'd3 // 8-bit negative number stored as 2's complement of 3

-6'sd3 // Used for performing signed integer math

4'd-2 // Illegal specification

- X or Z values

- An unknown value is denoted by an x

- A high impedance value is denoted by z 12'h13x // This is a 12-bit number; 4 least significant bits unknown 6'hx // This is a 6-bit hex number 32'bz // This is a 32-bit high impedance number

## Strings

#### Strings

- A string is a sequence of characters that are enclosed by double quotes

- It cannot be on multiple lines

- Strings are treated as a sequence of one-byte ASCII values

"Hello Verilog World" // is a string

"a / b" // is a string

reg [8\*18:1] string\_value; // Declare a variable that is 18 bytes wide

Initial

string\_value = "Hello Verilog World"; // String can be stored in variable

An underscore character "\_" is allowed anywhere in a number except the first character to improve readability

## Identifiers and Keywords

- Keywords are special identifiers reserved to define the language constructs written in lowercase

- Identifiers are names given to objects so that they can be referenced in the design

- Identifiers are made up of alphanumeric characters, the underscore ( \_ ), or the dollar sign (\$)

- Identifiers are case sensitive

- Identifiers start with an alphabetic character or an underscore

reg value; // reg is a keyword; value is an identifier input clk; // input is a keyword, clk is an identifier

# Data Types

I

| Value Set                  | Value Level                      | Condition in Hardw          | are Circuits |

|----------------------------|----------------------------------|-----------------------------|--------------|

|                            | 0                                | Logic zero, false condition |              |

| Verilog supports four      | 1 Logic one, true condition      |                             | tion         |

| values and eight strengths | x Unknown logic value            |                             |              |

| to model the functionality | z High impedance, floating state |                             | ting state   |

| of real hardware           | Steven oth Laural                | True                        | Desma        |

| The four value levels are: | -                                | Туре                        | Degree       |

|                            | supply                           | Driving                     | strongest    |

| 0, I, x, z                 | strong                           | Driving                     |              |

| strength levels are often  | pull                             | riving                      | Î            |

| used to resolve conflicts  | large                            | Storage                     |              |

| between drivers of         | weak                             | Driving                     |              |

| different strengths in     | medium                           | Storage                     |              |

| digital circuits           | small                            | Storage                     |              |

|                            | highz                            | High Impedance              | weakest      |

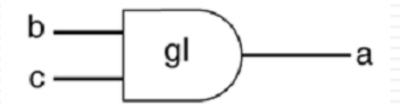

#### Nets

- Nets represent connections between hardware elements

- Nets are declared primarily with the keyword wire

- The terms wire and net are often used interchangeably

- Nets get the output value of their drivers

- The default value of a net is z

Example:

wire a; // Declare net a for the above circuit

wire b,c; // Declare two wires b,c for the above circuit

wire d = 1'b0; // Net d is fixed to logic value 0 at declaration.

## Registers

- Registers represent data storage elements

- Registers retain value until another value is placed onto them

- Unlike a net, a register does not need a driver

- Register data types are commonly declared by the keyword reg

- Registers can also be declared as signed variables

- The default value for a reg data type is x

reg reset; // declare a variable reset that can hold its value initial // this construct will be discussed later begin

reset = 1'b1; //initialize reset to 1 to reset the digital circuit. #100 reset = 1'b0; // after 100 time units reset is deasserted. end

42

#### Vectors

Nets or reg data types can be declared as vectors (multiple bit widths)

wire a; // scalar net variable, default

wire [7:0] bus; // 8-bit bus

wire [31:0] busA,busB,busC; // 3 buses of 32-bit width.

reg clock; // scalar register, default

reg [0:40] virtual\_addr; // Vector register, virtual address 41 bits

Vectors can be declared at [high# : low#] or [low# :

high#], but the left number in the squared brackets is always the most significant bit of the vector

## Vector Part Select

□ For the vector declarations shown above, it is possible to address bits or parts of vectors busA[7] // bit # 7 of vector busA bus[2:0] // Three least significant bits of vector bus, // using bus[0:2] is illegal because the significant bit should // always be on the left of a range specification virtual\_addr[0:1] // Two most significant bits of vector virtual\_addr Variable Vector Part Select Another ability provided in Verilog HDL is to have variable part selects of a vector Check the Palnitkar Verilog reference (page 48)

## Integer Numbers

An integer is a general purpose register data type

Integers are declared by the keyword integer

Integers store values as signed quantities

integer counter; // general purpose variable used as a counter.

initial

counter = -1; // A negative one is stored in the counter

## Integer Numbers (2)

#### Integers: Decimal, hexadecimal, octal, binary

- □ Simple decimal form:

- 32 decimal 32

- -15 decimal -15

- Signed integers

- Negative numbers are in two's complement form

- Base format form:

[<size>] '<base><value> 'hAF (h, A, F are case insensitive) // 8-bit hex 'o721 // 9-bit octal 5'O37 // 5-bit octal 4'D2 // 4-bit decimal 4'B1x02 // 4-bit binary 7'hx (x is case insensitive) // 7-bit x (x enteded) 4'hz // 4-bit z (z extended)

## Integer Numbers (3)

- Unsigned integers

- Padding: 10'b10 // padded with 0's 10'bx10 // padded with x's

- can replace z in a number: used to enhance readability where z is a high impedance

- (underscore) can be used anywhere to enhance readability, except as the first character

- Example:

- 8'd-6 // illegal -8'd6 // -6 held in 8 bits

## **Real Numbers**

- Real number constants and real register data types are declared with the keyword real

- Real numbers cannot have a range declaration, and their default value is 0

- real delta; // Define a real variable called delta

- initial

- begin

```

delta = 4e10; // delta is assigned in scientific notation

delta = 2.13; // delta is assigned a value 2.13

```

#### end

- integer i; // Define an integer i

- initial

i = delta; // i gets the value 2 (rounded value of 2.13)

2014

## Real Numbers (2)

- Decimal notation

- 10.5

- 1.41421

- 0.01

- Scientific notation

- 235.1e2 (e is case insensitive)

// 23510.0

3.6E2

// 360.0

5E-4

// 0.0005

- Must have at least one digit on either side of decimal

Stored and manipulated in double precision (usually 64 bits)

## Time Data Type

- Verilog simulation is done with respect to simulation time

- A special time register data type is used in Verilog to store simulation time

- A time variable is declared with the keyword time

- The system function \$time is invoked to get the current simulation time

time save\_sim\_time; // Define a time variable save\_sim\_time initial

save\_sim\_time = \$time; // Save the current simulation time

2014

## Strings

"Sequence of characters"

\n, \t, \\, \", %%

\n = newline

\t = tab

\\ = backslash

\" = quote mark (")

%% = % sign

#### Arrays

- Arrays are allowed in Verilog for reg, integer, time, real, realtime and vector register data types

- Multi-dimensional arrays can also be declared with any number of dimensions

- Arrays of nets can also be used to connect ports of generated instances

- Arrays are accessed by <array\_name>[<subscript>]

integer count[0:7]; // An array of 8 count variables reg bool[31:0]; // Array of 32 one-bit boolean register variables time chk\_point[1:100]; // Array of 100 time checkpoint variables integer matrix[4:0][0:255]; // Two dimensional array of integers wire [7:0] w\_array2 [5:0]; // Declare an array of 8 bit vector wire wire w\_array1[7:0][5:0]; // Declare an array of single bit wires

#### Memories

- Memories are modeled in Verilog simply as a onedimensional array of registers

- Each element of the array is known as an element or word and is addressed by a single array index

- Each word can be one or more bits

reg mem1bit[0:1023]; // Memory mem1bit with 1K 1-bit words reg [7:0] membyte[0:1023]; // Memory membyte with 1K //8-bit words(bytes)

membyte[511] // Fetches 1 byte word whose address is 511.

#### Parameters

- Verilog allows constants to be defined in a module by the keyword parameter

- Parameters cannot be used as variables

- Parameter values for each module instance can be overridden individually at compile time

- This allows the module instances to be customized

- Parameters values can be changed at module instantiation or by using the defparam statement

parameter port\_id = 5; // Defines a constant port\_id

parameter cache\_line\_width = 256; // Defines width of cache\_line

parameter signed [15:0] WIDTH; // Fixed sign and range for width

## Module Parameter Values

- Two ways

- defparam statement:

Parameter value in any module instance can be changed by using hierarchical name.

defparam FA.n1.XOR\_DELAY = 2, FA.n2.AND\_DELAY = 3;

Module instance parameter value assignment:

□ Specify the parameter value in the module instantiation.

Order of assignment is the same as order of declarations within module

HA # (2, 3) h1 (.A(p), .B(Q), .S(S1), .C(X1));

## System Tasks

- Verilog provides standard system tasks for certain routine operations

- All system tasks appear in the form \$<keyword>

- Displaying information: \$display is the main system task for displaying values of variables or strings or expressions

\$display(p1, p2, p3,...., pn); // p1, p2, p3,..., pn can be quoted //strings or variables or expressions

```

/Display value of current simulation time 230

```

- \$display(\$time);

- -- 230

- //Display value of port\_id 5 in binary

- reg [4:0] port\_id;

- \$display("ID of the port is %b", port\_id);

- -- ID of the port is 00101

EE 432 VLSI Modeling and Design

## System Tasks (2)

Monitoring information: \$monitor continuously monitors the values of the variables or signals specified in the parameter list and displays all parameters in the list whenever the value of any one variable or signal changes

//Monitor time and value of the signals clock and reset //Clock toggles every 5 time units and reset goes down at 10 time units initial

begin

end

# System Tasks (3)

- Stopping and finishing in a simulation

- □ The task **\$stop** is provided to stop during a simulation

- The \$stop task puts the simulation in an interactive mode to enable debuging

- The \$finish task terminates the simulation

- // Stop at time 100 in the simulation and examine the results

- // Finish the simulation at time 1000.

- initial // to be explained later. time = 0

- begin

end

```

clock = 0;

```

```

reset = 1;

```

#100 \$stop; // This will suspend the simulation at time = 100

#900 \$finish; // This will terminate the simulation at time = 1000

## **Compiler Directives**

- Compiler directives are provided in Verilog

- All compiler directives are defined by using the `<keyword> construct

- We deal with the two most useful compiler directives: `define and `include:

- The `define directive is used to define text macros in Verilog

- //define a text macro that defines default word size

//Used as 'WORD\_SIZE in the code

'define WORD\_SIZE 32

- The `include directive allows you to include entire contents of a Verilog source file in another Verilog file during compilation

## Modules and Ports

#### Components of a Verilog Module

Module Name, Port List, Port Declarations (if ports present) Parameters (optional),

Declarations of wires, regs and other variables

Data flow statements (assign)

Instantiation of lower level modules

always and initial blocks. All behavioral statements go in these blocks.

Tasks and functions

endmodule statement

EE 432 VLSI Modeling and Design

## **Components of a Verilog Module**

To understand the components of a module shown above, check Example 4-1 (Palnitkar, P# 63)

#### Ports

- Ports provide the interface by which a module can communicate with its environment

- The internals of the module are not visible to the environment

- This provides a very powerful flexibility to the designer

- The internals of the module can be changed without affecting the environment as long as the interface is not modified

- Ports are also referred to as terminals

## List of Ports

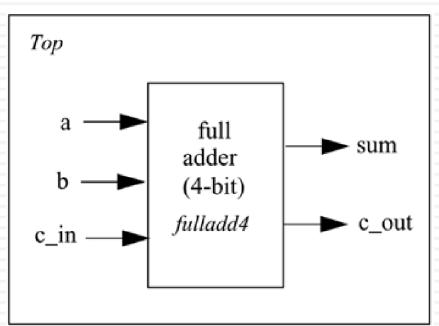

A module definition contains an optional list of ports

Consider a 4-bit full adder that is instantiated inside a

top-level module Top

<u>Example</u>

module fulladd4(sum, c\_out, a, b, c\_in); //Module with a list of ports module Top; // No list of ports, top-level module in simulation

## Port Declaration

All ports in the list of ports must be declared in the module as

follows

| Verilog Keyword | Type of Port       |

|-----------------|--------------------|

| input           | Input port         |

| output          | Output port        |

| inout           | Bidirectional port |

Each port in the port list is defined as input, output, or inout, based on the direction of the port signal

module fulladd4(sum, c\_out, a, b, c\_in);

//Begin port declaration

output[3:0] sum;

output c\_cout;

input [3:0] a, b;

input c\_in;

//End port declaration

#### **Alternative Declaration**

module fulladd4(output reg [3:0] sum, output reg c\_out, // output and c\_out are //declared as reg input [3:0] a, b, //wire by default input c\_in); //wire by default

## Port Declaration (2)

- Note that all port declarations are implicitly declared as wire in Verilog

- Thus, if a port is intended to be a wire, it is sufficient to declare it as output, input, or inout

- Input or inout ports are normally declared as wires

- However, if output ports hold their value, they must be declared as reg (inout cannot be declared as reg)

module DFF(q, d, clk, reset);

```

output q;

```

reg q; // Output port q holds value; therefore it is //declared as reg.

```

input d, clk, reset;

```

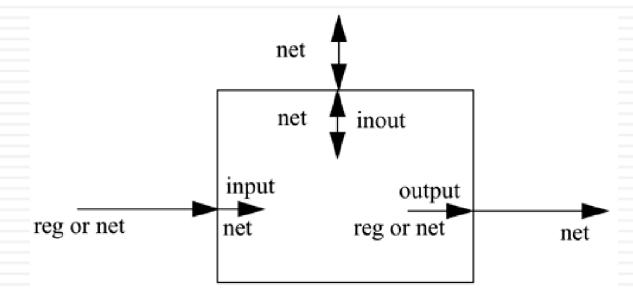

## Port Connection Rules

There are rules governing port connections when modules are instantiated within other modules

- Width matching

- Unconnected ports: Verilog allows ports to remain unconnected

#### Connecting Ports to External Signals

- There are two methods of making connections between signals specified in the module instantiation and the ports in a module definition

- Connecting by ordered list: The signals to be connected must appear in the module instantiation in the same order as the ports in the port list in the module definition

```

module Top;

//Declare connection variables

reg [3:0]A,B;

reg C_IN;

wire [3:0] SUM;

wire C_OUT;

//Instantiate fulladd4, call it fa_ordered.

//Signals are connected to ports in order (by position)

fulladd4 fa_ordered(SUM, C_OUT, A, B, C_IN);

```

#### Connecting Ports to External Signals (2)

- Connecting ports by name: Verilog provides the capability to connect external signals to ports by the port names, rather than by position

- Note that only those ports that are to be connected to external signals must be specified in port connection by name

Unconnected ports can be dropped

// Instantiate module fa\_byname and connect signals to ports by name fulladd4 fa\_byname(.sum(SUM), .b(B), .c\_in(C\_IN), .a(A),);

#### Hierarchy

- Module definition:

- module module\_name (port\_list);

- declarations\_and\_statements

- endmodule

- Module instantiation statement:

- module\_name instance\_name (port\_associations);

- Port associations can be positional or named; cannot be mixed

- local\_net\_name // positional

Port\_Name(local\_net\_name) // Named

- Ports can be: input, output, inout

- Port can be declared as a net or a reg; must have same size as port

Hierarchy (2)

Unconnected module inputs are driven to z state

Unconnected module outputs are simply unused

DFF d1 (.Q(QS), .QBAR(), .DADA(D), .PRESET(), .CLOCK(CK)); // Named

DFF d2 (QS, , D, , CK); // Positional // Output QBAR is not connected // Input PRESET is open and hence set to calue z

#### **Hierarchical Instantiation** module top (din1, din2, dout1, module sub\_block1 (a, z); dout2); input a; input din1; output z; input din2; wire a, z; output dout1; IV U1 (.A(a), .Z(z)); output dout2; endmodule wire din1, din2, dout1, dout2; module sub\_block2 (a, z); input a; sub\_block1 U1(.a(din1), .z(dout1));; output z; sub\_block2 U2(.a(din2), .z(dout2));; wire a, z; endmodule IV U1 (.A(a), .Z(z)); endmodule

EE432 VLSI Modeling and Design

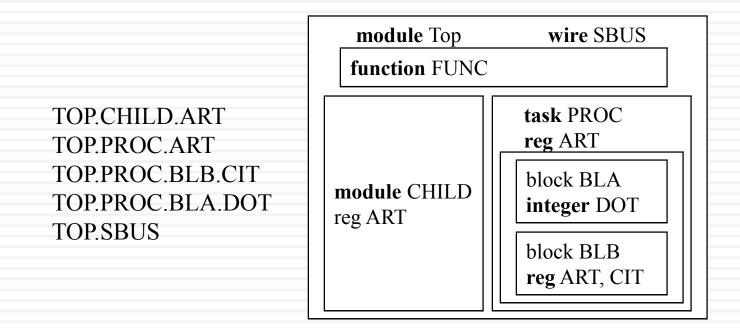

## **Hierarchical Path Name**

- Every identifier has a unique hierarchical path name

- Period character is the separator

- New hierarchy is defined by: module instantiation, task definition, function definition, named block

#### Introduction

- Four levels of abstraction used to describe hardware

- At gate level, the circuit is described in terms of gates

- Actually, the lowest level of abstraction is switch-(transistor-) level modeling

- Most digital design is now done at gate level or higher levels of abstraction

# Gate Types

- Verilog supports basic logic gates as predefined primitives

- These primitives are instantiated like modules except that they are predefined in Verilog and do not need a module definition

- There are two classes of basic gates: and/or gates and buf/not gates

## And/Or Gates

The and/or gates available in Verilog are and or xor nand nor xnor The output terminal is denoted by out Input terminals are denoted by il and i2 More than two inputs can be specified in a gate instantiation il il and 0 х Z nand Ô 0 0 0 1 1 0 0 0 i1 1 out 0 х х 1 0 i2 12 х 0 х 1 х х х х and 0 х z х z х х EE 432 VLSI Modeling and Design

х

1

х

х

х

х

77

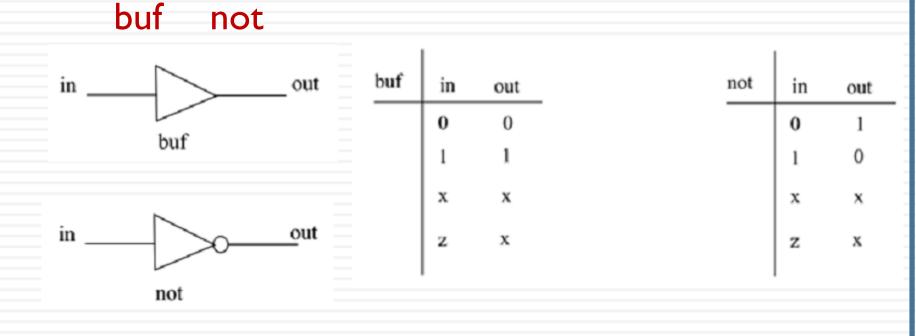

# **Buf/Not Gates**

- Buf/not gates have one scalar input and one or more scalar outputs

- Two basic buf/not gate primitives are provided in Verilog

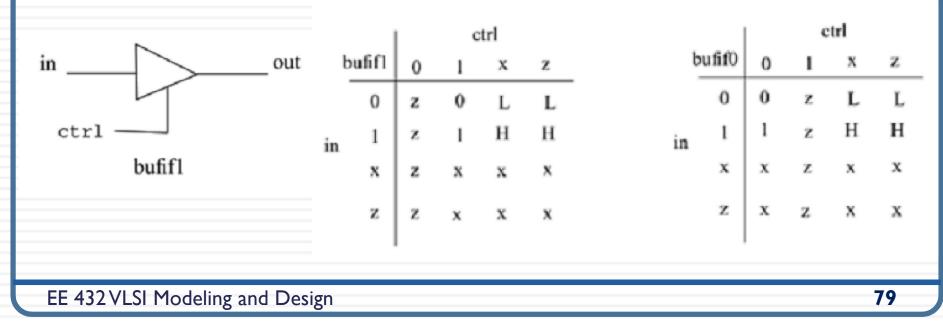

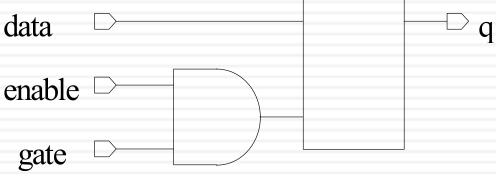

# Bufif/notif

- Gates with an additional control signal on buf and not gates are also available

- bufifl notifl

- bufif0 notif0

- These gates propagate only if their control signal is asserted

- They propagate z if their control signal is deasserted

## Array of Instances

- There are many situations when repetitive instances are required

- Verilog HDL allows an array of primitive instances to be defined

#### Example:

wire [3:0] OUT, IN1, IN2; // basic gate instantiations. nand n\_gate[3:0](OUT, IN1, IN2); // This is equivalent to the following 4 instantiations nand n\_gate0(OUT[0], IN1[0], IN2[0]); nand n\_gate1(OUT[1], IN1[1], IN2[1]); nand n\_gate2(OUT[2], IN1[2], IN2[2]); nand n\_gate3(OUT[3], IN1[3], IN2[3]);

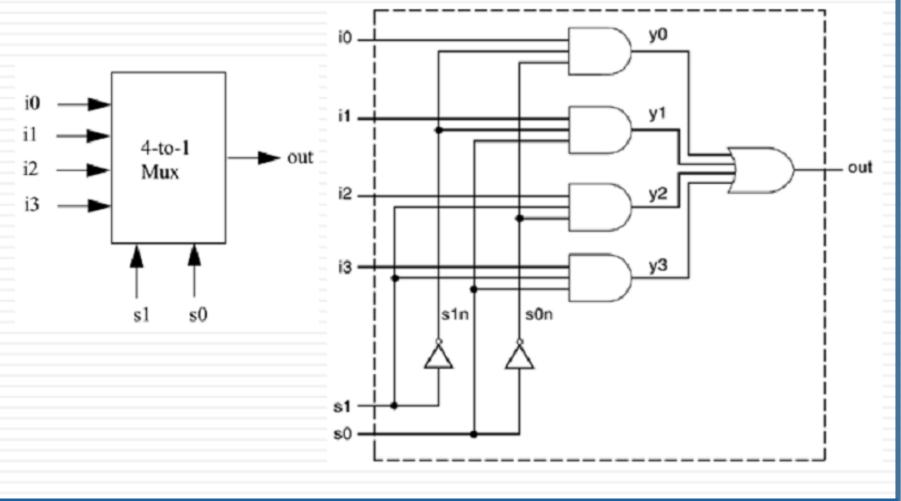

#### **Examples**

J

#### Gate-level multiplexer

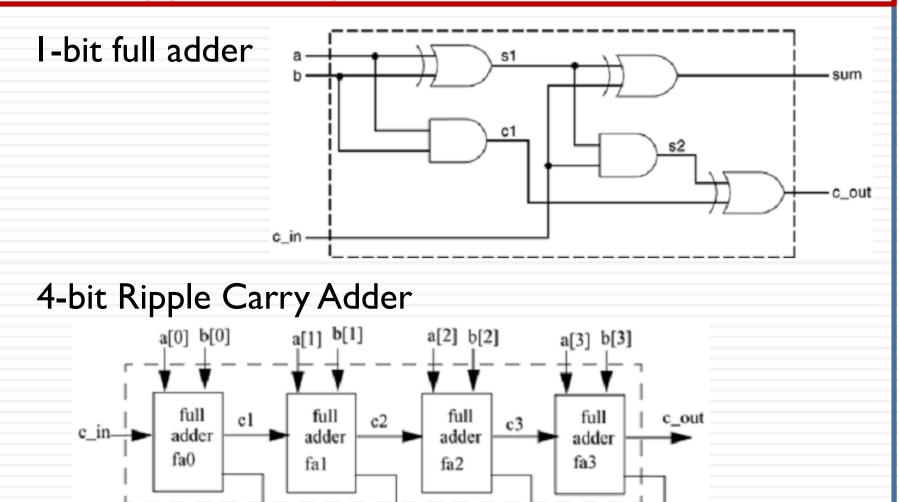

# 4-bit Ripple Carry Full Adder

sum[0]

sum[1]

sum[2]

sum[3]

2014

EE 432 VLSI Modeling and Design

## Gate Delays

- Gate delays allow the Verilog user to specify delays through the logic circuits

- Three types of delay specifications are allowed

- $\Box \operatorname{Rise}(0, x, z \rightarrow I)$

- □ Fall (I, x,  $z \rightarrow 0$ )

- $\Box \text{ Turn-off } (0, 1, x \rightarrow z)$

#### If no delays are specified, the default value is zero

// Delay of delay\_time for all transitions and #(delay\_time) a1(out, i1, i2); // Rise and Fall Delay Specification. and #(rise\_val, fall\_val) a2(out, i1, i2); // Rise, Fall, and Turn-off Delay Specification bufif0 #(rise\_val, fall\_val, turnoff\_val) b1 (out, in, control);

# Gate Delays (2)

Signal propagation delay from any gate input to the gate output

Up to three values per output: rise, fall, turn-off delay

not N1 (XBAR, X); **nand** #(6) (out, in1, in2); // All delays = 6 and #(3,5) (out, in1, in2, in3); /\* rise delay = 3, fall delay = 5,

// Zero delay

to x or z = min(3,5) \*/

Each delay can be written in min:typ:max form as well

**nand** #(2:3:4, 4:3:4) (out, in1, in2);

Can also use a specify block to specify delays

## Example

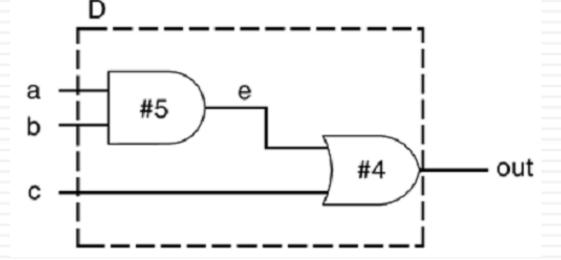

// Define a simple combination module called D

module D (out, a, b, c);

// I/O port declarations

output out;

input a,b,c;

// Internal nets

wire e;

// Instantiate primitive gates to build the circuit and #(5) a1(e, a, b); //Delay of 5 on gate a1 or #(4) o1(out, e,c); //Delay of 4 on gate o1 endmodule

85

2014

### A Clock Generator

module CLOCK (CLK,START); output CLK; Input START;

> initial begin START = 1; #3 START = 0; end

nor #5 (CLK, START, CLK); endmodule

// Generate a clock with on-off width of 5// Not synthesizable// For waveform only

EE432 VLSI Modeling and Design

## **Time Unit and Precision** Compiler directive: 'timescale 'timescale time\_unit / time\_precision; □ 1, 10, 100 /s, ms, us, ns, ps, fs 'timescale Ins / 100ps **module** AND\_FUNC (Z, A, B); output Z; input A, B; and # (5.22, 6.17) A1 (Z,A,B); endmodule Therefore,

/\* Delays are in ns. Delays are rounded to one-tenth of a ns (100ps).

5.22 becomes 5.2ns, 6.17 becomes 6.2ns and 8.59 becomes 8.6ns \*/

// If the following timescale directive is used:

'timescale |Ons / Ins

// Then 5.22 becomes 52ns, 6.17 becomes 62ns, 8.59 becomes 86ns

# **Getting Simulation Time**

System function, **\$time**: returns the simulation time as an integer value scaled time unit specified.

> **'timescale** 10ns / 1ns **module** TB;

initial \$monitor ("PUT\_A=%d PUT\_B=%d", PUT\_A, PUT\_B, "GET\_O=%d", GET\_O, "at time %t", \$time);

endmodule

PUT\_A=0 PUT\_B=0 GET\_O=0 at time 0 PUT\_A=0 PUT\_B=1 GET\_O=0 at time 5 PUT\_A=0 PUT\_B=0 GET\_O=0 at time 11

/\* \$time value is scaled to the time unit and then rounded \*/

. . . . . .

2014

### Introduction

- Verilog provides the ability to design circuits at a MOS-transistor level

- Verilog HDL currently provides only digital design capability with logic values 0 1, x, z

- There is no analog capability

- Thus, in Verilog HDL, transistors are also known switches that either conduct or are open

- Design at this level is becoming rare with the increasing complexity of circuits

90

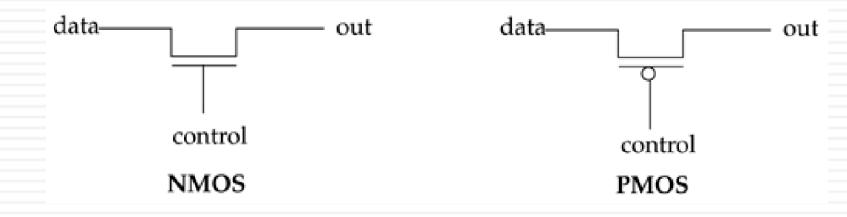

# **MOS Switches**

Two types of MOS switches can be defined with the keywords nmos and pmos

#### Example:

nmos n1(out, data, control); //instantiate a nmos switch pmos p1(out, data, control); //instantiate a pmos switch

# MOS Switches (2)

- The value of the out signal is determined from the values of data and control signals.

- Logic tables for out are shown in the following Table

- Some combinations of data and control cause the output to be either a 1 or 0, or to an z value without a preference for either value

- The symbol L stands for 0 or z; H stands for 1 or z

|                                 |    | control |   |   |   |                   | control |   |    |   |

|---------------------------------|----|---------|---|---|---|-------------------|---------|---|----|---|

| nm                              | os | 0       | 1 | x | z | pmos              | 0       | 1 | x  | z |

|                                 | 0  | z       | 0 | L | L | . 0               | 0       | z | L  | L |

| data                            | 1  | z       | 1 | Н | Н | data <sup>1</sup> | 1       | z | Н  | Н |

|                                 | x  | z       | x | x | x | x<br>z            | x       | z | x  | x |

|                                 | z  | z       | z | z | z |                   | z       | z | z  | z |

| EE 432 VLSI Modeling and Design |    |         |   |   |   |                   |         |   | 92 |   |

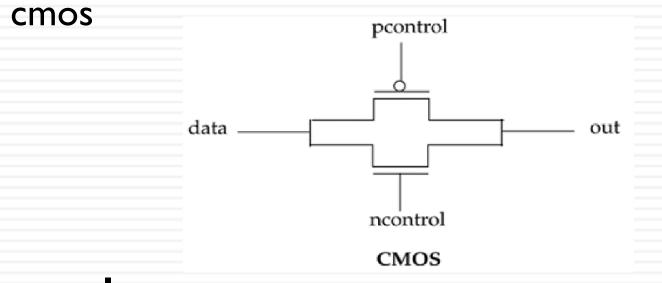

# **CMOS** Switches

#### CMOS switches are declared with the keyword

#### **Example:**

cmos c1(out, data, ncontrol, pcontrol);//instantiate cmos gate.

# **Bidirectional Switches**

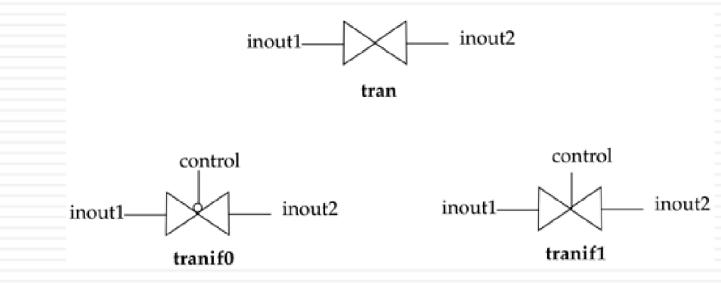

Three keywords are used to define bidirectional switches: tran, tranif0, and tranif1

#### Example:

tran t1(inout1, inout2); //instance name t1 is optional

tranif0 (inout1, inout2, control); //instance name is not specified

# Power and Ground

- The power (Vdd, logic 1) and Ground (Vss, logic 0) sources are needed when transistor-level circuits are designed

- Power and ground sources are defined with keywords supply I and supply0

#### Example:

supply1 vdd; supply0 gnd; assign a = vdd; //Connect a to vdd assign b = gnd; //Connect b to gnd

### **Resistive Switches**

Resistive switches have higher source-to-drain impedance than regular switches and reduce the strength of signals passing through them

Resistive switches are declared with keywords that have an "r" prefixed to the corresponding keyword for the regular switch

> rnmos rpmos //resistive nmos and pmos switches rcmos //resistive cmos switch rtran rtranif0 rtranif1 //resistive bidirectional switches

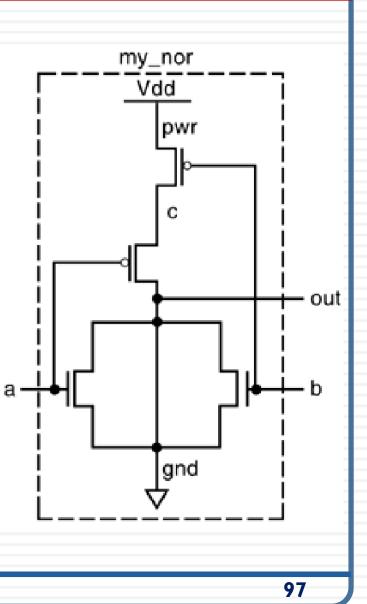

# Example: CMOS NOR Gate

| //Define our own nor gate, my_nor             |  |  |  |  |  |  |

|-----------------------------------------------|--|--|--|--|--|--|

| module my_nor(out, a, b);                     |  |  |  |  |  |  |

| output out;                                   |  |  |  |  |  |  |

| input a, b;                                   |  |  |  |  |  |  |

| //internal wires                              |  |  |  |  |  |  |

| wire c;                                       |  |  |  |  |  |  |

| //set up power and ground lines               |  |  |  |  |  |  |

| supply1 pwr; //pwr is connected to Vdd        |  |  |  |  |  |  |

| supply0 gnd ; //gnd is connected to Vss(groun |  |  |  |  |  |  |

| //instantiate pmos switches                   |  |  |  |  |  |  |

| pmos (c, pwr, b);                             |  |  |  |  |  |  |

| pmos (out, c, a);                             |  |  |  |  |  |  |

| //instantiate nmos switches                   |  |  |  |  |  |  |

| nmos (out, gnd, a);                           |  |  |  |  |  |  |

| nmos (out, gnd, b);                           |  |  |  |  |  |  |

| endmodule                                     |  |  |  |  |  |  |

EE 432 VLSI Modeling and Design

#### 2014

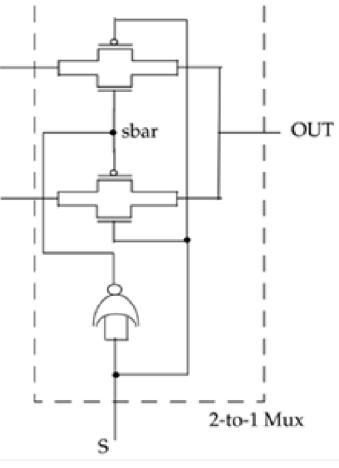

# Example: 2-to-1 Multiplexer

//Define a 2-to-1 multiplexer using switches module my mux (out, s, i0, i1); output out; input s, i0, i1; 10 //internal wire wire sbar; //complement of s //create the complement of s; //use my nor defined previously. my\_nor nt(sbar, s, s); //equivalent t //instantiate cmos switches cmos (out, i0, sbar, s); cmos (out, i1, s, sbar); endmodule

### Introduction

- Verilog provides the ability to define User-Defined Primitives (UDP)

- There are two types of UDPs: combinational and sequential

- Combinational UDPs are defined where the output is solely determined by a logical combination of the inputs

- Sequential UDPs take the value of the current inputs and the current output to determine the value of the next output.

100

#### 2014

# **UDP** Syntax

UDP definition in pseudo syntax form is as follows:

//UDP name and terminal list

primitive <udp\_name> (

<output\_terminal\_name>(only

one allowed)

<input\_terminal\_names> );

//Terminal declarations

output

<output\_terminal\_name>;

input <input\_terminal\_names>;

reg

<output\_terminal\_name>;(optio

nal; only for sequential UDP)

// UDP initialization (optional; only for sequential UDP initial <output\_terminal\_name> = <value>;

//UDP state table

table

endtable

//End of UDP definition

endprimitive

# **UDP** Rules

- UDPs can take only scalar input terminals (I bit)

- UDPs can have only one scalar output terminal (I bit) always appearing first in the terminal list

- In the declarations section, the output terminal is declared with the keyword output

- The output terminal of sequential UDP is declared as a reg

- The inputs are declared with the keyword input

- The state in a sequential UDP can be initialized with an initial statement

- The state table entries can contain values 0, 1, or x

- UDPs are defined at the same level as modules

- UDPs do not support inout ports.

### State Table Entries

- Each entry in the state table in a combinational UDP has the following pseudosyntax

- <input1> <input2> ..... <inputN> : <output>;

- The <input#> values in a state table entry must appear in the same order as they appear in the input terminal list

- Inputs and output are separated by a ":"

- A state table entry ends with a ";"

- All possible combinations of inputs, where the output produces a known value, must be explicitly specified.

Otherwise, if a certain combination occurs and the corresponding entry is not in the table, the output is x.

#### Combinational UDP primitive MUX1BIT (Z, A, B, SEL); output Z; input A, B, SEL; table // A SEL В : Z 1 0 ? 0; <u>1;</u> Don't care 0 ? 0 / 0 0: X endtable endprimitive

$\Box$  Any combination that is not specified is an x.

Output port must be the first port.

"?" represents iteration over "0", "1", or "x" logic values

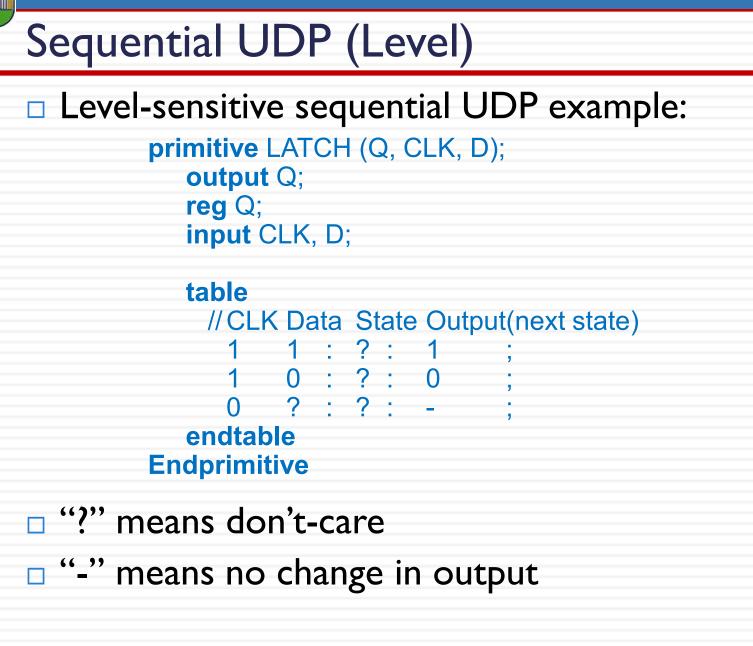

# Sequential UDPs

- The output of a sequential UDP is always declared as a reg

- An initial statement can be used to initialize output of sequential UDPs

- □ The format of a state table entry is slightly different

- <inputl> <input2> ..... <inputN> : <current\_state> : <next\_state>;

- There are three sections in a state table entry: inputs, current state, and next state separated by a colon (:) symbol

- The input specification of state table entries can be in terms of input levels or edge transitions

- The current state is the current value of the output register

- □ The next state is computed based on inputs and the current state

- All possible combinations of inputs must be specified to avoid unknown output values

#### Sequential UDP (Edge) Edge-sensitive sequential UDP example: primitive D\_EDGE\_FF (Q, CLK, D); output Q; reg Q; input CLK, D; table //CLK Data State Output(next state) (01) 0 : ? : 0 (01) 1 : ? : 1 (0x) 1 : 1 : 1 (0x) 0 : 0 : 0// Ignore negative edge of clock; (?0) ? : ? : -// Ignore data change on steady clock; ? (??) : ? : endtable endprimitive

EE432 VLSI Modeling and Design

## Introduction

- For small circuits, the gate-level modeling approach works very well

- However, in complex designs the number of gates is very large

- Thus, designers can design more effectively if they concentrate on implementing the function at a level of abstraction higher than gate level

- Dataflow modeling provides a powerful way to implement a design

- In logic synthesis, automated tools create a gate-level circuit from a dataflow description

## **Basics** Models behavior of combinational logic Dataflow style using continuous assignment Assign a value to a net Examples: wire [3:0] Z, PRESET, CLEAR; assign $\vec{Z} = PRESET \& CLEAR;$ wire COUT, CIN; wire [3:0] SUM, A, B; assign {COUT, SUM} = A+ B + CIN; assign MUX = (S == 0) ? A: 'bz, MUX = (S == 1) ? B: 'bz, MUX = (S == 2) ? C: bz,MUX = (S == 3)? D: 'bz; assign Z = ~(A | B) & (C | D);

Expression on right-hand side is evaluated whenever any operand changes

EE432 VLSI Modeling and Design

## Net Declaration

Can have an assignment in the net declaration wire [3:0] A = 4'b0;

assign PRESET = 'b1;

**wire** #10 A\_GT\_B = A > B;

- Only one assignment to a net using net declaration

- Multiple assignments to a net is done using continuous assignments

- Continuous assignments have the following characteristics:

- □ The left hand side of an assignment must be a net (cannot be a reg)

- Continuous assignments are always active

- The operands on the right-hand side can be registers or nets or function calls

- Delay values can be specified for assignments in terms of time units

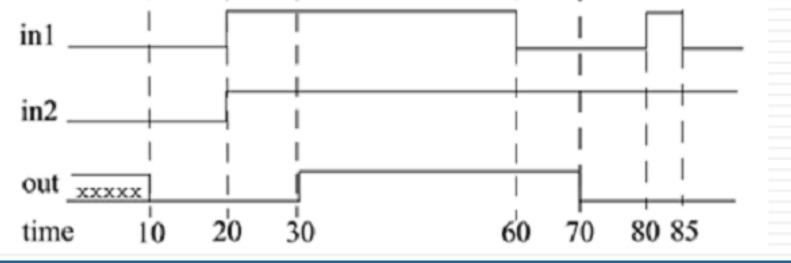

## Delays

Delay values control the time between the change in a right-hand-side operand and when the new value is assigned to the left-hand side

## Regular Assignment Delay

assign #10 out = in1 & in2; // Delay in a continuous assign

```

Delays (2)

Delay between assignment of right-hand side to left-

hand side

wire #10 A = B && C; // Continuous delay

Net delay

wire #10 A;

// Any change to A is delayed 10 time units before it takes effect

If delay is in a net declaration assignment, then delay is

not net delay

wire #10 A = B + C;

// 10 time units id it part of the continuous assignment and not net

delay

If value changes before it has a chance to propagate,

latest value change will be applied

Inertial delay

```

EE432 VLSI Modeling and Design

2014

## Expressions, Operators, and Operands

- Dataflow modeling describes the design in terms of expressions instead of primitive gates

- Expressions are constructs that combine operators and operands to produce a result

- // Examples of expressions. Combines operands and operators

a ^ b

addr1[20:17] + addr2[20:17]

in1 | in2

Operands can be any one of the data types defined previously

integer count, final\_count;

final\_count = count + 1;//count is an integer operand

## Operands

- I. Numbered operands

- 2. Functional call operands

- A functional call can be used as an operand within an expression wire [7:0] A;

// PARITY is a function described elsewhere

assign PAR OUT = PARITY(A);

3. Bit selects

input [3:0] A, B, C; output [3:0] SUM; assign SUM[0] = (A[0] ^ B[0] ^ C[0]);

- 4. Part selects

- 5. Memory addressing

reg [7:0] RegFile [0:10]; reg [7:0] A; RegFile[3] = A; //

// 11 b-bit registers

// A assigned to 3rd register in RegFile

## Operators

Operators act on the operands to produce desired results

#### d1 && d2 // && is an operator on operands d1 and d2

| Arithmetic    | * / + - % **         |

|---------------|----------------------|

| Logical       | ! &&                 |

| Relational    | > < >= <=            |

| Equality      | == != === !==        |

| Bitwise       | ~ &   ^ ^~ or ~^     |

| Reduction     | & ~&   ~  ^ ^~ or ~^ |

| Shift         | >> << >>> <<<        |

| Concatenation | {}                   |

| Replication   | { { } }              |

| Conditional   | ?:                   |

EE 432 VLSI Modeling and Design

## Arithmetic Operators

| + | (plus)     |

|---|------------|

| - | (minus)    |

| * | (multiply) |

| / | (divide)   |

| % | (modulus)  |

Integer division will truncate

- % gives the remainder with the sign of the first operand

- $\Box$  If any bit of operand is **x** or **z**, the result is **x**

- reg data type holds an unsigned value, while integer data type holds a signed value

```

reg [0:7] A;integer B;A = -4'd6;B = -4'd6;// reg A has value unsigned 10B = -4'd6;// integer B has value signed -6A-2A-2// result is 8B-2// result is -8

```

EE 432 VLSI Modeling and Design

## **Relational Operators**

- > (greater than)

- < (less than)

- >= (greater than or equal to)

- <= (less than or equal to)

## $\Box$ If there are x or z in operand, the result is x

If unequal bit lengths, smaller operand is zero-filled on most significant side (I.e., on left)

## **Equality Operators**

| ==<br>!=<br>unknown) | (logical equality, result may be unknown)<br>(logical inequality, result may be |

|----------------------|---------------------------------------------------------------------------------|

| ===                  | (case equality, x and z also compared)                                          |

| !==                  | (case inequality, x and z also compared)                                        |

$$A = b11x0;$$

$B = b11x0;$

A == B is known. A === B is true

Unknown is same as false in synthesis

Compare bit by bit, zero-filling on most significant side

# Logical Operators

&& (logical and)

|| (logical or)

A = 'b0110; // non-zero

B = 'b0100; // non-zero

A || B is 1. A && B is also 1

Non-zero value is treated as I

If result is ambiguous, set it to x

## **Bit-wise Operators**

(unary negation)

(binary and)

(binary or)

(binary exclusive-or)

^^,^~ (binary exclusive-nor)

A = 'b0110; B = 'b0100;

A | B is 0110 A & B is 0100

If operand sizes are unequal, smaller is zero-filed in the most significant bit side

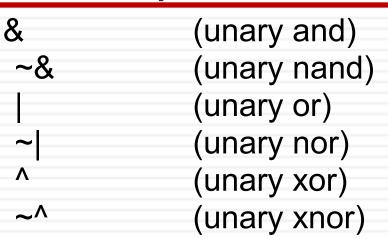

## **Reduction Operators**

A = 'b0110; B = 'b0100;

| B is 1 & B is 0

Bitwise operation on a single operand to produce I-bit result

## Shift Operators

| << | (left shift)  |

|----|---------------|

| >> | (right shift) |

reg [0:7] D;

D = 4'b0111;

D >> 2 has the value 0001

Logic shift, fill vacant bits with 0

If right operand is an x or a z, result is x

Right operand is always an unsigned number

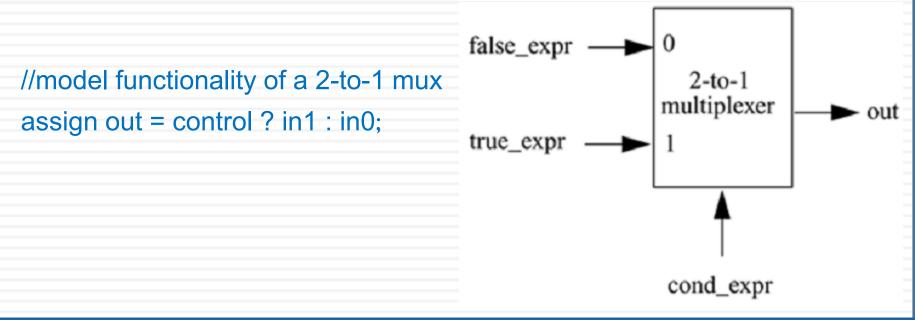

# Conditional Operators expr1 ? expr2:expr3 wire [0:2] GRADE = SCORE > 60 ? PASS:FAIL; If expr1 is an x or a z, expr2 and expr3 are combined bit by bit (all x's except 0 with 0 = 0, 1 with 1 = 1) Example:

#### EE 432 VLSI Modeling and Design

## **Concatenation and Replication**

wire [7:0] DBUS; wire [11:0] ABUS;

```

assign ABUS[7:4] = {DBUS[0], DBUS[1], DBUS[2], DBUS[3]};

assign ABUS = {DBUS[3:0], DBUS[7:4]};

assign DBUS[7:4] = {2{4'B1011}}; // 1011_1011

assign ABUS[7:4] = {{4{DBUS[7]}, DBUS}; // sign extension

```

## Examples

Write the Verilog description and test benches of the following circuits using dataflow modeling:

- 4-to-I Multiplexer

- Logic equation

- Conditional operator

- 4-bit Full Adder

- Dataflow operators

- Full adder with carry lookahead

- Ripple Counter

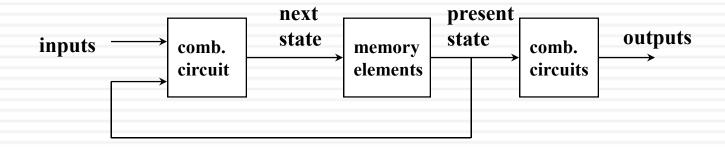

## Introduction

- Designers need to be able to evaluate the trade-offs of various architectures and algorithms in the earlier design stages

- Architectural evaluation takes place at an algorithmic level

- Verilog provides designers the ability to describe design functionality in an algorithmic manner

- In other words, the designer describes the behavior of the circuit

- Behavioral modeling represents the circuit at a very high level of abstraction

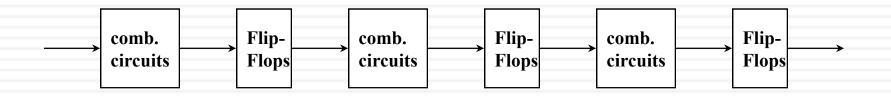

# **Procedure Blocks**

Use procedural blocks to describe the operation of the circuit

Two procedural blocks:

always block: executes repetitively

initial block: executes once

Concurrent procedural blocks

□All execute concurrently

□All activated at time 0

# The initial Block

- An initial block starts at time

0, executes exactly once

during a simulation

- Ports and variables can be initialized in declaration

- The initial block is always used in testbenches

## Example:

module stimulus;

reg x,y, a,b, m;

initial

m = 1'b0; //single statement; //does //not need to be grouped

#### initial

#### begin

#5 a = 1'b1; //multiple //statements; need to be grouped #25 b = 1'b0; end initial begin #10 x = 1'b0; #25 y = 1'b1; end initial #50 \$finish; endmodule

# The always Block

Can model:

- combinational logic

- sequential logic

Syntax:

// Single statement

always @ (event expression)

statement

// Sequential statements

always @ (event expression)

begin

sequential statements

end

# The always Block (2)

- "event expression" specified a set of events based on which statements within the always block are executed sequentially

- The type of logic synthesized is based on what is specified in the "event expression"

- Four forms of event expressions are supported

- An OR of several identifiers (comb/seq logic)

- The rising edge clock (register inference)

- The falling edge clock (register inference)

- Asynchronous reset (register inference)

## **Event Expressions**

I. An OR of several identifiers

```

Combinational or synchronous logic may be represented by a set of sequential statements

always @ (id1 or id2 or id3 or ... or idn)

begin

sequential_statements

end

```

A synchronous block may appear inside an always block (representing synchronous logic) in two forms:

always @ (posedge clock\_name)

begin

sequential\_statements

end

always @ (negedge clock\_name)

begin

```

sequential_statements

```

```

end

```

Sequential statements not within a sequential block represents combinational logic

## Example

```

module Comb (A, B, C, Y);

input A, B, C;

output Y;

reg Y;

```

```

always @ (A or B or C)

begin

Y = A ^ B ^ C;

end

endmodule

```

# **Event Expressions**

2. The rising edge clock (register inference)

- The event expression denotes the rising edge of a clock

- The behavior within block represents synchronous logic triggered on the rising edge of clock

always @ (posedge CLK)

begin

Q = D;

```

end

```

- 3. The falling edge clock (register inference)

- The event expression denotes the falling edge of a clock

```

The behavior within block represents synchronous logic triggered on the rising edge of clock

always @ (negedge CLK)

begin

Next_state = Current_state;

end

```

# **Register Inference**

```

module SEQ (CLK, A, B, Y);

input CLK, A, B;

output Y;

reg Y;

always @ (posedge CLK)

begin

Y = A + B;

end

\diamond \mathbf{Y}

D

0

endmodule A

ШK

B

\mathrm{UK}^{\diamond}

```

EE432 VLSI Modeling and Design

## **Event Expressions**

## 4. Asynchronous reset (register inference)

```

Asynchronous resets in addition to register inferences (2 & 3)

above)

always (a) (negedge reset1 or posedge CLK or posedge reset2)

begin

if (!reset1)

begin

/* sequential_statements

asynchronous input triggered by the false condition of reset1 to the registers */

end

else

begin

/* sequential statement

Optional for sequential statements. Could well have "else-if" clauses*/

if (!reset2)

begin

/* sequential statements: Asynchronous inputs triggered by reset2 */

end

else

begin

// sequential statements: register inference statements.

end

end

end

```

# **Register Inference**

- The language constructs "registers" is synthesized as a hardware register (flip-flop) if the register is assigned a value in:

- A sequential block

- An "always" block that has an event expression denoting a rising or falling clock edge

- It is illegal to assign a register value on both rising and falling edges of a clock

## Sequential Statements and the Always Block

- Only "registers" and "integers" may be assigned values in sequential statements

- If an output port of the module is to be assigned a value in an always block it generally must be declared to be of a register type as well

- Possible sequential statements within an always block are procedure assignment synchronous block if statement case statement for-loop statement repeat loop statement block statement task enabling

## Sequential Statements and the Always Block (2)

An "always" block is concurrent and so may appear in any order within a module body with other continuous assignments (module instantiations or other always block)

Data is passed out of an always block using register variables

# **Procedural Assignments**

- Procedural assignments update values of reg, integer, real, or time variables

- The value placed on a variable will remain unchanged until another procedural assignment updates the variable with a different value

- The syntax of procedural assignment assignment ::= variable\_lvalue = [ delay\_or\_event\_control ] expression

- The left-hand side of a procedural assignment <lvalue> can be

- □ A reg, integer, real, or time register variable or a memory element

- □ A bit select of these variables (e.g., addr[0])

- A part select of these variables (e.g., addr[31:16])

- A concatenation of any of the above

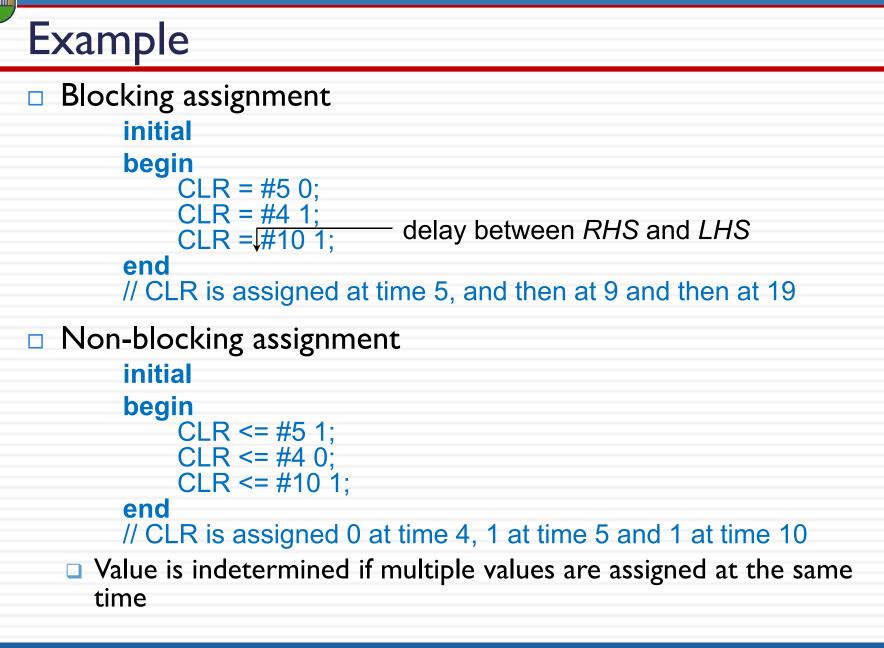

- There are two types of procedural assignment statements: blocking and nonblocking

4

# **Blocking versus Non-Blocking**

- Blocking procedural assignment:

- Assignment is executed before any of the following ones are executed.

### Only applies to its own sequential block.

$reg_a = 10;$

- Non-blocking procedural assignment.

- The procedural flow is not blocked

# 2

reg\_a <= LOAD; reg\_b <= STORE;</pre>

Evaluate right-hand side and schedules the assignment.

At the end of the current loop, assignment to the left-hand side is made

#### 2014

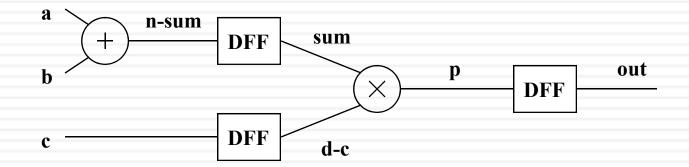

# Blocking versus Non-Blocking (2)

## Blocking (=)

Assignment are blocked, i.e., they must be executed before subsequent statements are executed always @ (posedge clock) begin B = A;C = B;D = C;end □ 1 flip-flop (Data in is A, data out is D)

## Non-blocking (<=)</p>

Assignment are not blocked, i.e., can be scheduled to occur without blocking the procedural flow always @ (posedge clock) begin B <= A; C <= B; D <= C; end

3 pipelined flip-flops (A to B to C to D)

## Application of Non-blocking Assignments

- It is recommended that blocking and non-blocking assignments not be mixed in the same always block

- Using non-blocking assignments in place of blocking assignments is highly recommended in places where concurrent data transfers take place after a common event

- blocking assignments can potentially cause race conditions because the final result depends on the order in which the assignments are evaluated

- Typical applications of non-blocking assignments include pipeline modeling and modeling of several mutually exclusive data transfers

- On the downside, non-blocking assignments can potentially cause a degradation in the simulator performance and increase in memory usage

# Procedural Continuous Assignment

- Allow expression to be driven continuously into integers or nets

- assign and deassign procedural statements: for integers

- force and release procedural statements: for nets

# Assign and Deassign

- An assign procedural statement overrides all procedural assignments to a register

- The deassign procedural statement ends the continuous assignment to a register

- Value remains until assigned again

- If assign applied to an already assigned register, it is deassigned first before making the new procedural continuous assignment

## Example

```

module DFF (D, CLR, CLK, PRESET, Q);

input D, CLR, CLK, PRESET;

output Q;

reg Q;

always @ (CLR or PRESET)

if (CLR)

assign Q = 0; // D has no effect on Q

else if (PRESET)

assign Q = 1; // D has no effect on Q

else

deassign Q;

always @ (posedge CLK)

Q = D;

endmodule;

```

## Force and Release

- Similar to assign-deassign, except that it can be applied to nets as well as registers

- force procedural statement on a net overrides all drivers of the net, until a *release* is executed on the net

```

or #1 (PRT, STD, DXZ);

```

EE432 VLSI Modeling and Design

# **High-Level Constructs**

## □ if statement

# loop statement (forever, repeat, while, for)

### case statement

# **Conditional Statements**

- Conditional statements are used for making decisions based upon certain conditions

- These conditions are used to decide whether or not a statement should be executed

- Keywords if and else are used for conditional statements

- There are three types of conditional statements

# Conditional Statements (2)

Usage of conditional statements is shown below //Type 1 conditional statement. No else statement. //Statement executes or does not execute. if (<expression>) true\_statement ;

//Type 2 conditional statement. One else statement

//Either true\_statement or false\_statement is evaluated

if (<expression>) true\_statement ; else false\_statement ;

//Type 3 conditional statement. Nested if-else-if. //Choice of multiple statements. Only one is executed. if (<expression1>) true\_statement1 ; else if (<expression2>) true\_statement2 ; else if (<expression3>) true\_statement3 ; else default\_statement ;

# Examples

```

//Type 1 statements

if (!lock) buffer = data;

if (enable) out = in;

//Type 2 statements

if (number queued <

MAX_Q_DEPTH)

begin

data queue = data;

number queued =

number queued + 1;

end

else

$display("Queue Full. Try

again");

```

//Type 3 statements //Execute statements based on //ALU control signal. if (alu\_control == 0) y = x + z;else if(alu\_control == 1) y = x - z;else if(alu\_control == 2) y = x \* z;else \$display("Invalid ALU control signal");

# Multi-way Branching (case Statement)

The keywords case, endcase, and default are used in the case statement

case (expression)

alternative1: statement1;

alternative2: statement2;

alternative3: statement3;

default: default\_statement; endcase

. . .

. . .

## case Statement

- Each of statement I, statement2, default\_statement can be a single statement or a block of multiple statements

- A block of multiple statements must be grouped by keywords begin and end

- The expression is compared to the alternatives in the order they are written

- For the first alternative that matches, the corresponding statement or block is executed

- If none of the alternatives matches, the default\_statement is executed

- The default\_statement is optional

- The case statement compares 0, 1, x, and z values in the expression and the alternative bit for bit.

## Example

```

module mux4 to 1 (out, i0, i1, i2, i3, s1, s0);

// Port declarations from the I/O diagram

output out;

input i0, i1, i2, i3;

input s1, s0;

reg out;

always @(s1 or s0 or i0 or i1 or i2 or i3)

case ({s1, s0}) //Switch based on concatenation of control signals

2'd0 : out = i0;

2'd1 : out = i1;

2'd2 : out = i2;

2'd3 : out = i3;

default: $display("Invalid control signals");

endcase

endmodule

EE 432 VLSI Modeling and Design

```

## casex, casez Keywords

- There are two variations of the case statement. They are denoted by keywords, casex and casez

- casez treats all z values in the case alternatives or the case expression as don't cares

- All bit positions with z can also represented by ? in that position.

- casex treats all x and z values in the case item or the case expression as don't cares

The use of casex and casez allows comparison of only non-x or -z positions in the case expression and the case alternatives IIII

# Sequential Statements in a Block

| <ul> <li>"case" statement</li> <li>Specifies a multi-way<br/>branch based on the value<br/>of an expression</li> <li>Is sequential and therefore<br/>may be nested to any level.</li> <li>\$parallel ensures not<br/>priority encoded (less<br/>logic)</li> </ul> | module EX_CASE (A, B, F, D, H, N);<br>input A, B;<br>input [3:0] F;<br>inout H, N;<br>output [1:0] D;<br>reg H, N;<br>reg [1:0] D;<br>always @(A or B or F or H or N)<br>begin<br>case (F) // \$parallel<br>0, 4, 8, 9: D = {H, A};<br>5: N = N & B;<br>7: H = B;<br>default: begin<br>D = {H, A}; N = N & A; H = B;<br>end<br>endcase<br>end<br>endmodule |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# case Statement (Full and Parallel)

```

module FULL (c1, c2, c3, c4, a, y);

input c1, c2, c3, c4;

output y;

input [1:0] a;

output [6:0] y;

reg [6:0] y;

always @ (posedge Pclk)

begin

if (Preset)

begin

y <= #2 {6'b0, 1'b0};

end

else casex ({c1, c2, c3, c4}) // $full $parallel

4'b1x0x: y[0] <= #2 a[0];

4'b1x1x: y[1:0] <= #2 a;

4'b01x0: y <= #2 y + 7'b1;

y <= #2 {y[6:2]+5'b1, 2'b0};

4'b1111:

endcase

end

EE432 VLSI Modeling and Design

```

## Loops

- There are four types of looping statements in Verilog: while, for, repeat, and forever

- All looping statements can appear only inside an initial or always block

- Loops may contain delay expressions

- Nested loops are allowed

# while Loop

The while loop executes until the whileexpression is not true If the loop is entered when the whileexpression is not true, the loop is not executed at all

#### Example:

//Illustration 1: Increment count from 0 to 127. Exit at count 128. //Display the count variable. integer count; initial begin count = 0;while (count < 128) //Execute //till count is 127. loop //exit at count 128 begin \$display("Count = %d", count); count = count + 1;end end

#### 2014

# for Loop

- The keyword for is used to specify this loop

- The for loop contains three parts:

- An initial condition

- A check to see if the terminating condition is true

- A procedural assignment to change value of the control variable

#### Example:

integer count;

initial

for ( count=0; count < 128; count = count + 1)

\$display("Count = %d", count);

- for loops are generally used when there is a fixed beginning and end to the loop

- If the loop is simply looping on a certain condition, it is better to use the while loop

## repeat Loop

- The keyword repeat is used for this loop. The repeat construct executes the loop a fixed number of times.

- A repeat construct cannot be used to loop on a general logical expression

- A repeat construct must contain a number, which can be a constant, a variable or a signal value

#### Example:

//Illustration 1 : increment and //display count from 0 to 127 integer count; initial begin count = 0;repeat(128) begin \$display("Count = %d", count); count = count + 1;end end

## forever loop

- The keyword forever is used to express this loop

- The loop does not contain any expression and executes forever until the \$finish task is encountered

- The loop is equivalent to a while loop with an expression that always evaluates to true

- A forever loop is typically used in conjunction with timing control constructs

#### Example:

```

//Example 1: Clock generation

reg clock;

initial

begin

clock = 1'b0;

forever #10 clock = ~clock;

//Clock with period of 20 units

end

//Example 2: Synchronize two register

//values at every +ve clock edge

reg clock;

reg x, y;

initial

forever @(posedge clock) x = y;

```

# Sequential and Parallel Blocks

- Block statements are used to group multiple statements to act together as one

- There are two types of blocks:

- Sequential blocks

- Parallel blocks

- Blocks can be named optionally

- Registers can be declared locally

- Blocks can be referenced (disable statement)

- Can uniquely identify registers

## Sequential blocks

- The keywords begin and end are used to group statements into sequential blocks

- Sequential blocks have the following characteristics

- The statements in a sequential block are processed in the order they are specified

- A statement is executed only after its preceding statement completes execution (except for nonblocking assignments with intra-assignment timing control)

- If delay or event control is specified, it is relative to the simulation time when the previous statement in the block completed execution

# Sequential Blocks (2)

begin

[ : block\_id { declarations } ]

statements

end

// Waveform generation

begin

#2 stream = 1;

#7 stream = 0;

#10 stream = 1;

#14 stream = 0;

#16 stream = 1;

#21 stream = 0;

end

## Parallel Blocks

- Parallel blocks, specified by keywords fork and join, provide interesting simulation features

- Parallel blocks have the following characteristics

- Statements in a parallel block are executed concurrently

- Ordering of statements is controlled by the delay or event control assigned to each statement

- If delay or event control is specified, it is relative to the time the block was entered

- The order in which the statements are written in the block is not important

- Parallel blocks might cause implicit race conditions if two statements that affect the same variable complete at the same time

# Parallel Blocks (2)

Control passes out of block after all statements finish

# fork [ : block\_id { declarations } ] statements join

```

// Waveform generation

fork

#2 stream = 1;

#5 stream = 0;

#3 stream = 1;

#4 stream = 0;

#2 stream = 1;

#5 stream = 0;

join

```

EE432 VLSI Modeling and Design

# Examples

//Example 1: Parallel blocks with delay. reg x, y; reg [1:0] z, w; initial fork x = 1'b0; //completes at //simulation time 0 #5 y = 1'b1; //completes at //simulation time 5 #10 z = {x, y}; //completes at //simulation time 10 #20 w = {y, x}; //completes //at simulation time 20 join

//Parallel blocks with deliberate //race condition reg x, y; reg [1:0] z, w; initial fork x = 1'b0;y = 1'b1; $z = \{x, y\};$  $w = \{y, x\};$ join

# Named Blocks

- Blocks can be given names.

- Local variables can be declared for the named block

- Named blocks are a part of the design hierarchy.

Variables in a named block can be accessed by using hierarchical name referencing.

- Named blocks can be disabled, i.e., their execution can be stopped

#### Example:

...

...

End

//Named blocks

module top;

initial

begin: block1 //sequential block named

block1

integer i; //integer i is static and local to //block1

// can be accessed by hierarchical name,

//top.blockl.i

## **Generate Blocks**

- Generate statements allow Verilog code to be generated dynamically at elaboration time before the simulation begins

- This facilitates the creation of parameterized models.

- Generate statements are particularly convenient when the same operation or module instance is repeated for multiple bits of a vector, or when certain Verilog code is conditionally included based on parameter definitions

- Generate statements allow control over the declaration of variables, functions, and tasks, as well as control over instantiations

- All generate instantiations are coded with a module scope and require the keywords generate - endgenerate

# Generate Blocks (2)

- Generated instantiations can be one or more of the following types

- Modules

- User defined primitives

- Verilog gate primitives

- Continuous assignments

initial and always blocks

- Generated declarations and instantiations can be conditionally instantiated into a design

- Generated variable declarations and instantiations can be multiply instantiated into a design

- Generated instances have unique identifier names and can be referenced hierarchically

- Generate statements permit the following Verilog data types to be declared

- 🗆 net, reg

- integer, real, time, realtime

- event

# Generate Blocks (3)

- There are three methods to create generate statements

- Generate loop

- Generate conditional

- Generate case

# Generate Loop

- A generate loop permits one or more of the following to be instantiated multiple times using a for loop:

- Variable declarations

- Modules

- User defined primitives, Gate primitives

- Continuous assignments

- initial and always blocks

## Example

// This module generates a bit-wise xor of two N-bit buses module bitwise\_xor (out, i0, i1); // Parameter Declaration. This can be redefined parameter N = 32; // 32-bit bus by default // Port declarations output [N-1:0] out; input [N-1:0] i0, i1; // Declare a temporary loop variable genvar j;

//Generate the bit-wise Xor with a single loop

generate for (j=0; j<N; j=j+1) begin: xor\_loop

xor g1 (out[j], i0[j], i1[j]);

end //end of the for loop inside the generate block

endgenerate //end of the generate block

endmodule</pre>

# Generate Conditional