## **CMOS Digital Integrated Circuits**

## Lec 11 Sequential CMOS Logic Circuits

1

**CMOS** Digital Integrated Circuits

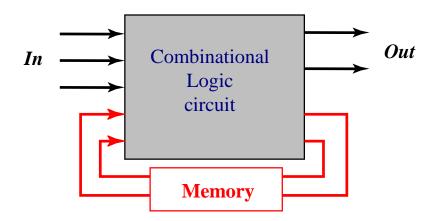

## **Sequential Logic**

#### Sequential

The output is determined by •Current inputs •Previous inputs

#### **Output** = f(In, Previous In)

• The regenerative behavior of sequential circuits is due to either a **direct** or an **indirect feedback** connection between the output and input

## Critical Components of Sequential Circuits Basic Regenerative Circuits

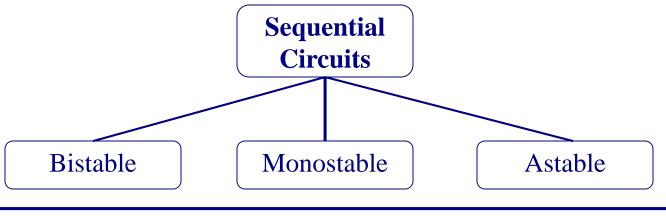

**Categories of Basic Regenerative Circuits**

3

- Bistable Circuits: Two stable states or operation modes, each of them can be attained under certain input and output conditions. The most widely used and the most important class which is used for the basic latch, flip-flop circuits, registers, and memory elements.

- 2. Monostable Circuits: One stable state or operation mode

- **3.** Astable Circuits: No stable operating point or state which the circuit can preserve for a certain time period. The output oscillates without settling into a stable operating mode.

## **Behavior of Bistable Elements (1/7)**

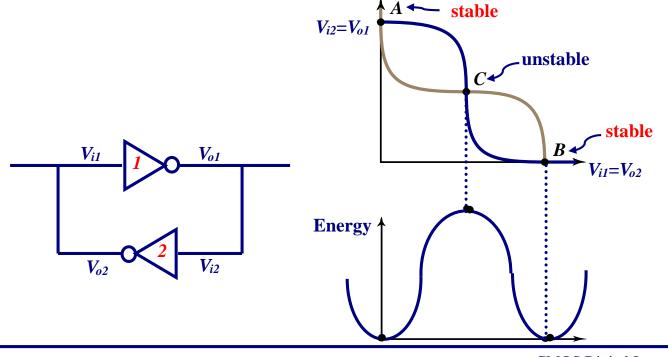

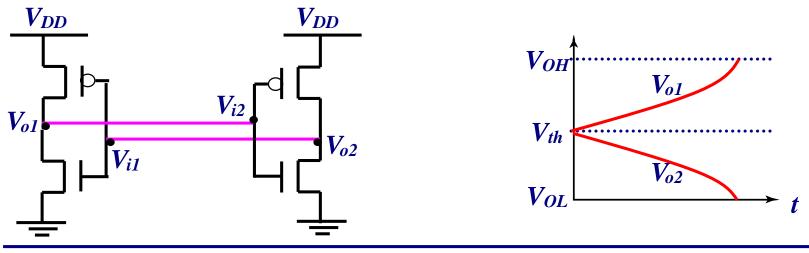

#### **Two Identical Cross-Coupled Inverter Circuit**

- Voltage Transfer Curves

- » The output voltage of inverter (1) is equal to the input voltage of inverter (2), and the output voltage of inverter (2) is equal to the input voltage of inverter (1).

- » *A* and *B* are stable points: If the circuit is initially operating at one of them, it will preserve this state. The gain is smaller than **unity**.

## **Behavior of Bistable Elements (2/7)**

- » *C* is an unstable point: The voltage gains of both inverters are larger than unity. A small voltage perturbation at this operating point will be amplified  $\Rightarrow$  the operating point will move to one of the stable operating points, *A* or *B*.

- Energy Levels:

- » The potential energy is at its minimum at A and B, since the voltage gains of both inverters are equal to zero.

- » The potential energy is at its maximum at C, since the voltage gains of both inverters are maximum. (all four transistors are in saturation modes)

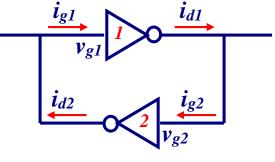

## Behavior of Bistable Elements (3/7) Analysis of the Output Voltages

- Let the initially operating point is at  $v_{o1}=v_{o2}=V_{th}$ , and assume that the gate capacitance  $(C_g)$  of each inverter is much larger than the drain capacitance  $(C_d)$ .

- The drain current of each inverter is equal to the gate current of the other inverter.

$$i_{g1} = i_{d2} = g_m v_{g2}$$

$i_{g2} = i_{d1} = g_m v_{g1}$  (Eq. A)

$g_m$  is the small-signal transconductance of the inverter.

• The gate voltages can be expressed by gate charges,  $q_1$  and  $q_2$

$$v_{g1} = q_1 / C_g$$

(Eq. B)

$$v_{g2} = q_2 / C_g$$

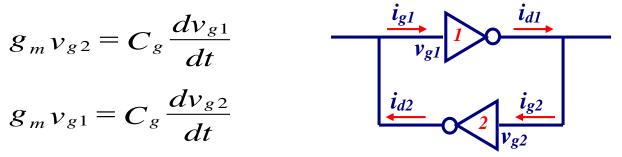

• Also the small-signal gate currents can be expressed as

$$i_{g1} = C_g \cdot dv_{g1} / dt$$

(Eq. C)

$$i_{g2} = C_g \cdot dv_{g2} / dt$$

## **Behavior of Bistable Elements (4/7) Analysis of the Output Voltages**

• Combine Eq. A and C, we have

• Replace the gate voltages by Eq. B, we obtain

$$\frac{g_m}{C_g}q_2 = \frac{dq_1}{dt}$$

$$\frac{g_m}{C_g}q_1 = \frac{dq_2}{dt}$$

• The above equations can be simplified to

$$\frac{g_m}{C_g} q_1 = \frac{C_g}{g_m} \frac{d^2 q_1}{dt^2} \Longrightarrow \frac{d^2 q_1}{dt^2} = \left(\frac{g_m}{C_g}\right)^2 q_1 = \frac{1}{\tau_0^2} q_1; \ \tau_0 = \frac{C_g}{g_m}$$

## Behavior of Bistable Elements (5/7) Analysis of the Output Voltages

• Therefore,

$$q_{1}(t) = \frac{q_{1}(0) - \tau_{0} q_{1}(0)}{2} e^{-\frac{t}{\tau_{0}}} + \frac{q_{1}(0) + \tau_{0} q_{1}(0)}{2} e^{-\frac{t}{\tau_{0}}}$$

where  $q_I(\theta) = C_g \cdot v_{gI}(\theta)$

• Replace the gate charge pf both inverters with the corresponding out-put voltages variables, we have

$$v_{o2}(t) = \frac{v_{o2}(0) - \tau_0 v_{o2}(0)}{2} e^{-\frac{t}{\tau_0}} + \frac{v_{o2}(0) + \tau_0 v_{o2}(0)}{2} e^{\frac{t}{\tau_0}}$$

$$v_{o1}(t) = \frac{v_{o1}(0) - \tau_0 v_{o1}(0)}{2} e^{-\frac{t}{\tau_0}} + \frac{v_{o1}(0) + \tau_0 v_{o1}(0)}{2} e^{\frac{t}{\tau_0}}$$

$$e^{-\frac{t}{\tau_0}} + \frac{v_{o1}(0) + \tau_0 v_{o1}(0)}{2} e^{\frac{t}{\tau_0}}$$

• For large values of *t*, the above equations can be approximated as

$$v_{o1}(t) \approx \frac{1}{2} (v_{o1}(0) + \tau_0 v_{o1}(0)) e^{\frac{t}{\tau_0}}$$

$$v_{o2}(t) \approx \frac{1}{2} (v_{o2}(0) + \tau_0 v_{o2}(0)) e^{\frac{t}{\tau_0}}$$

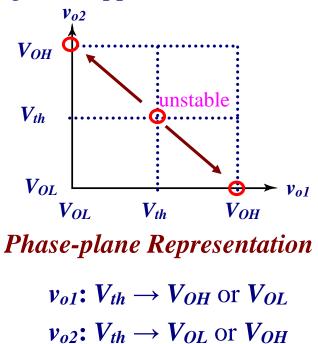

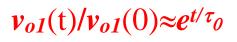

## Behavior of Bistable Elements (6/7) Analysis of the Output Voltages

- Depending on the polarity of the initial small perturbations  $dv_{o1}(0)$ and  $dv_{o1}(0)$ , the  $v_{o1}$  and  $v_{o2}$  will diverge from their initial values of  $V_{th}$  to either  $V_{OL}$  and  $V_{OH}$ .

- The polarity of *dv<sub>o1</sub>* must always be **opposite** to that of *dv<sub>o2</sub>*, because of the **charge-conservation principle**. Therefore, *v<sub>o1</sub>* and *v<sub>o2</sub>* always diverge into opposite directions.

**CMOS** Digital Integrated Circuits

## **Behavior of Bistable Elements (7/7) Analysis of the Output Voltages**

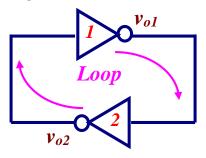

• As a bistable circuit settles from unstable operating point to its stable point, a signal travels around **2 INV loop n times.**

10

• If during interval t = T, the signal travels around the loop n times  $A^{n} \approx e^{T/\tau_{0}}$

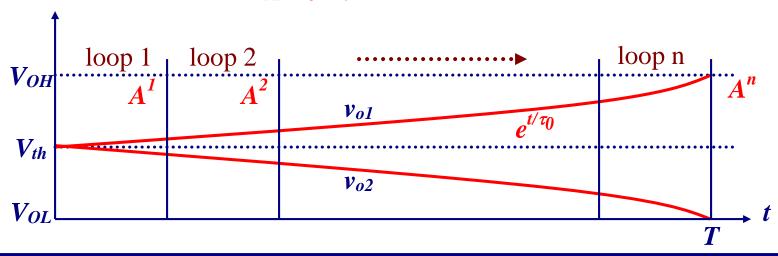

## **Naming Conventions**

- A latch is level sensitive

- A register is edge-triggered

- There are many different naming conventions

- For instance, many books call edge-triggered elements flip-flops

© Digital Integrated Circuits<sup>2nd</sup>

## Latch versus Register

**Register**

clock rises

stores data when

### Latch

# stores data when clock is low

**CMOS** Digital Integrated Circuits

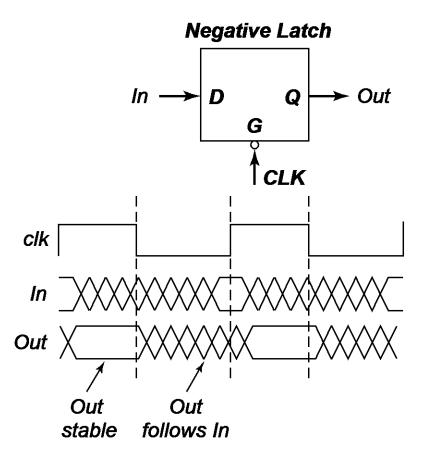

## Latches

**Positive Latch** In · Q - Out D G **↑с***і*к clk In Out Out Out stable follows In

13

© Digital Integrated Circuits<sup>2nd</sup>

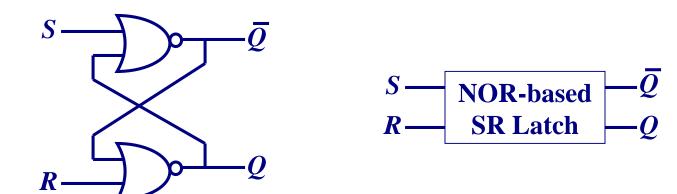

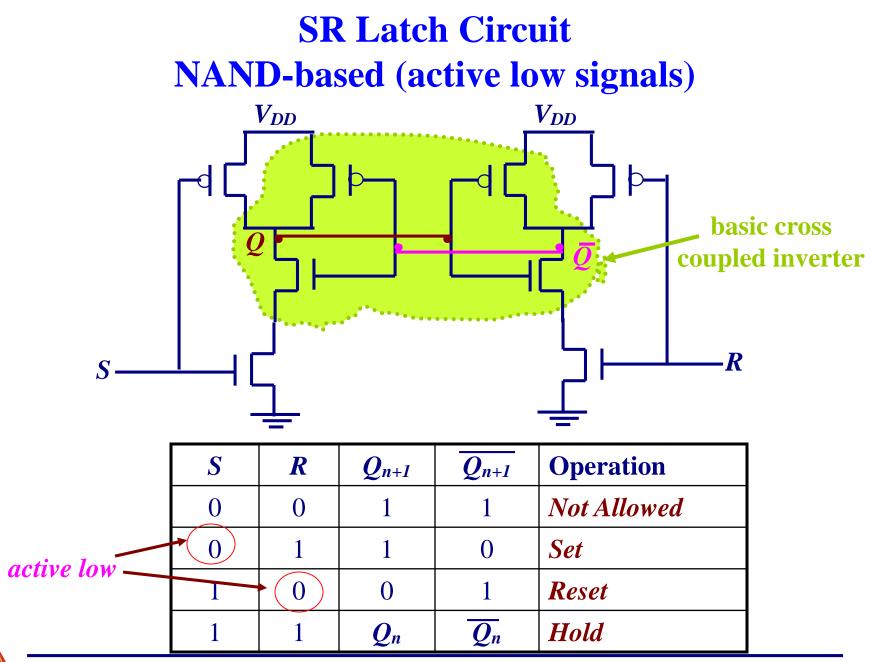

## **SR Latch Circuit**

- The two cross-coupled inverters can perform a simple memory function of *holding* its state. However, the two-inverter circuit alone has no provision for allowing its state to be changed externally from one stable operating point to other.

- In order to allow such a change of state, we need to *add simple switches* which can be used to force or trigger the circuit from one operating point to the other.

**Schematic Diagram of SR Latch**

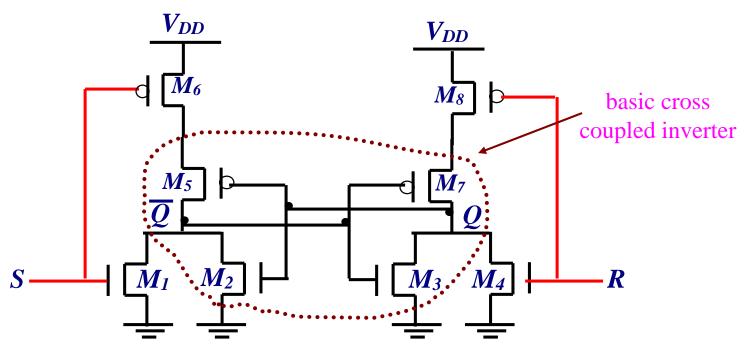

## **SR Latch Circuit (Cont.)**

- The below circuit shows the simple CMOS SR latch which consists of two triggering inputs, *S* (*set*) and *R* (*reset*).

- The SR Latch consists of two CMOS NOR2 gates. One of the input terminals of each NOR gate is used to cross-couple to the output of the other NOR gate. The second input enables triggering of the circuit.

## SR Latch Circuit Truth Table

- Set: S=1,  $R=0 \Rightarrow Q_{n+1}=1$ ,  $\overline{Q_{n+1}}=0$ . The SR latch will be *set* regardless of its previous state.

- **Reset:** S=0,  $R=1 \Rightarrow Q_{n+1}=0$ ,  $\overline{Q_{n+1}}=1$ . The SR latch will be *reset* regardless of its previous state.

- Hold: S=0,  $R=0 \Rightarrow Q_{n+1}=Q_n$ ,  $Q_{n+1}=Q_n$ . The previous states will be *held*.

|               | S | R | $Q_{n+1}$ | $\overline{Q_{n+1}}$ | Operation   |

|---------------|---|---|-----------|----------------------|-------------|

| active high — | 0 | 0 | Qn        | $\overline{Q_n}$     | Hold        |

|               |   | 0 | 1         | 0                    | Set         |

|               | 0 |   | 0         | 1                    | Reset       |

|               | 1 | 1 | 0         | 0                    | Not Allowed |

Truth Table of NOR-based (active high inputs) SR latch

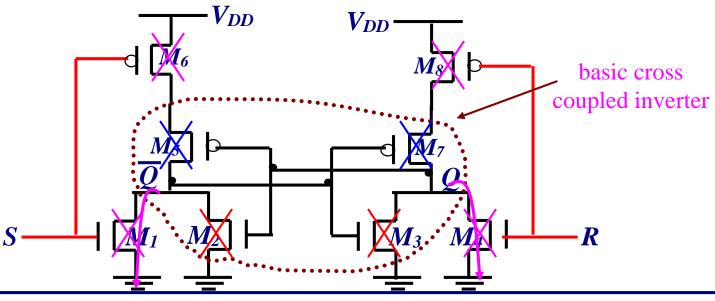

## **SR Latch Circuit Operation Modes of the Transistors**

| S                      | R   | $Q_{n+1}$       | $Q_{n+1}$              | Operation                                                                     |                                                                                                                             |  |  |  | Operation |  |  |

|------------------------|-----|-----------------|------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|-----------|--|--|

|                        |     |                 |                        | NMOS                                                                          | PMOS                                                                                                                        |  |  |  |           |  |  |

| <b>V</b> <sub>OH</sub> | VOL |                 |                        | $M_{1}^{(1)}, M_{2}^{(3)}$ on; $M_{3,}^{(2)}M_{4}^{(1)}$ off                  | $M_{7}^{2}, M_{8}^{0}$ on; $M_{5}^{3}, M_{6}^{0}$ off                                                                       |  |  |  |           |  |  |

| Vol                    | VOH | $V_{OL}^{(0)}$  |                        | $M_{1}^{0}, M_{2}^{0}$ off; $M_{3}^{0}, M_{4}^{0}$ on                         | M <sup>3</sup> <sub>7</sub> , M <sup>0</sup> <sub>8</sub> off; M <sup>2</sup> <sub>5</sub> , M <sup>0</sup> <sub>6</sub> on |  |  |  |           |  |  |

| Vol                    | Vol | V <sub>OH</sub> | Vol                    | <i>M</i> <sub>1</sub> , <i>M</i> <sub>4</sub> off; <i>M</i> <sub>2</sub> , on | $M_{6}, M_{8} \text{ on; } M_{7}, \text{ on}$                                                                               |  |  |  |           |  |  |

| Vol                    | Vol | Vol             | <b>V</b> <sub>ОН</sub> | <i>M</i> <sub>1</sub> , <i>M</i> <sub>4</sub> off; <i>M</i> <sub>3</sub> , on | $M_{6}, M_{8}$ on; $M_{5}$ , on                                                                                             |  |  |  |           |  |  |

## **SR Latch Circuit Transient Analysis**

- For transient analysis, we have to consider an event which results in a state change, reset ⇒ set, or set ⇒ reset

- In either case, we note that both of the output nodes undergo simultaneous voltage transitions. One is from logic-low to logic-high, and the other is from logic-high to logic-low.

- The exact transient analysis need to solve two coupled differential equations.

- For simplicity, we can assume that the *two events take place in sequence rather than simultaneously*. (overestimation)

#### Switching Time Calculation

• The total lumped capacitance at each output node can be approximated as

$C_{Q} = C_{gb,2} + C_{gb,5} + C_{db,3} + C_{db,4} + C_{db,7} + C_{sb,7} + C_{db,8}$  $C_{\bar{Q}} = C_{gb,3} + C_{gb,7} + C_{db,1} + C_{db,2} + C_{db,5} + C_{sb,5} + C_{db,6}$

## SR Latch Circuit Transient Analysis (Cont.)

• Assuming that the latch is initially reset and that a set operation is being performed, the rise time associated with node *Q* can be estimated as

$V_{DD}$   $V_{DD}$   $V_{DD}$   $Q \uparrow \Rightarrow M_2 \text{ on}$   $Q \uparrow \Rightarrow M_2 \text{ on}$   $T_{rise,Q}(\text{NOR2})$   $M_1$   $M_2$   $C_2$   $M_3$   $M_4$   $I \rightarrow 0$

**CMOS** Digital Integrated Circuits

20

## **Clocked Latch and Flip-Flop Circuits**

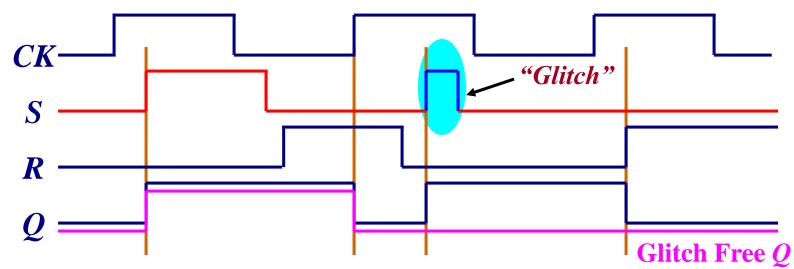

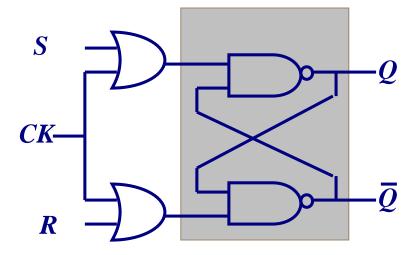

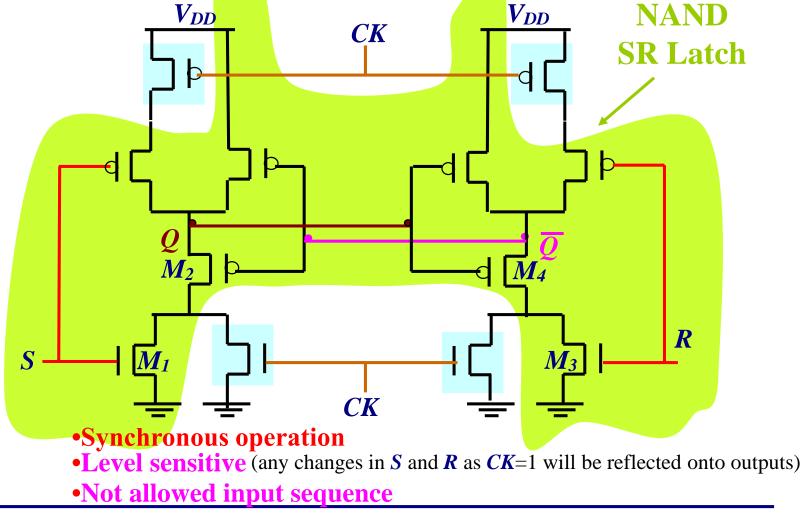

The previous SR latch circuits are *asynchronous* sequential circuits. The *synchronization* can be introduced through **clock CK**, which the outputs will respond to the input levels only during the active period of a clock pulse.

Clocked SR Latch

SR Latch

S  $\int \overline{Q}$

CK Q

R Q

• When CK=0, S, R have no influence of Q,  $\overline{Q} \Rightarrow Hold$ Set State: CK=1, S=1,  $R=0 \Rightarrow Q_{n+1}=1$ ,  $\overline{Q_{n+1}}=0$ Reset State: CK=1, S=0,  $R=1 \Rightarrow Q_{n+1}=0$ ,  $\overline{Q_{n+1}}=1$ Not Allowed: CK=1, S=1, R=1Active "High"

## AOI-based Implementation of Clocked NOR-based SR Latch

- The AOI-based implementation need a very small transistor count, compared with the circuit consisting of two AND2 and two NOR2 gates

- » NOR-based: 20 transistors

- **NOR SR** » **AOI-based: 12** transistors Latch **V<sub>DD</sub>** V<sub>DD</sub> CK  $\overline{M}_1$  $M_2$  $M_3$  $M_4$ S  $M_1$ CK-CK

## **Operation of Clocked SR Latch**

| Operation | СК | S | R | $Q_{n+1}$ | $\overline{Q_{n+1}}$ |

|-----------|----|---|---|-----------|----------------------|

| Hold      | 0  | X | X | Qn        | $\overline{Q_n}$     |

| Set       |    | 1 | 0 | 1         | 0                    |

| Reset     |    | 0 | 1 | 0         | 1                    |

| Not Allow | 1  | 1 | 1 | 1         | 1                    |

- When "Glitch" ON S (or R) occurs during CK = 1, Q is set (or reset).

- Level Sensitive: When CK = 1, any changes in *S*, *R* will effect *Q*.

### **Clocked NAND-based SR Latch**

• When CK = 1, S and R have no influence of Q and  $\overline{Q} \Rightarrow Hold$

| Operation | СК | S | R | $Q_{n+1}$ | $\overline{Q_{n+1}}$ |

|-----------|----|---|---|-----------|----------------------|

| Hold      | 1  | X | X | Qn        | $\overline{Q_n}$     |

| Set       | 0  | 0 | 1 | 1         | 0                    |

| Reset     | 0  | 1 | 0 | 0         | 1                    |

| Not Allow | 0  | 0 | 0 | 0         | 0                    |

#### **OAI-based Implementation of Clocked NAND-based SR Latch**

• The OAI-based implementation need a very small transistor count, compared with the circuit consisting of two OR2 and two NAND2 gates

25

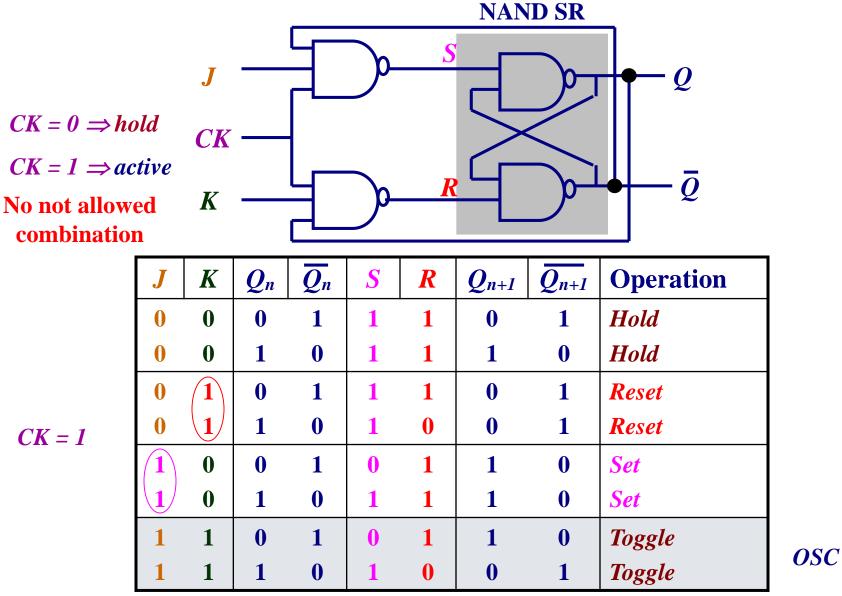

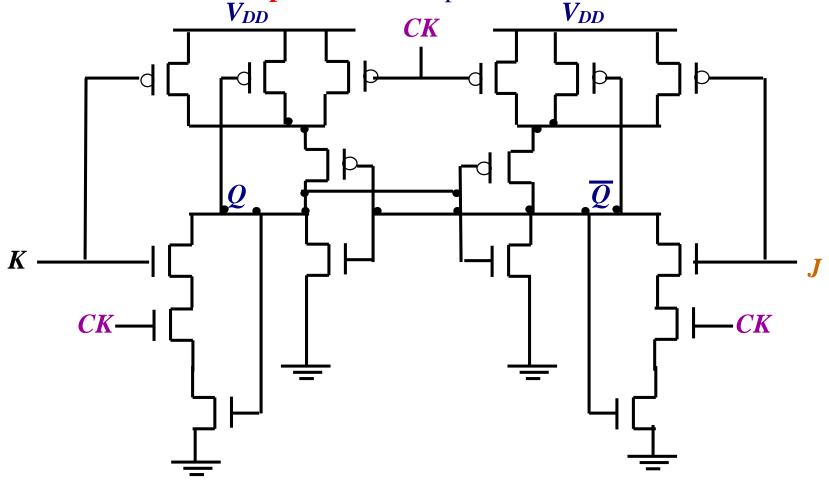

## **Clocked JK Latch**

24 26

**CMOS** Digital Integrated Circuits

## **AOI-based Implementation of NOR-based Clocked JK Latch**

• The AOI-based implementation has a **very small transistor count**, and a **more compact** circuit compared to all-NAND realization.

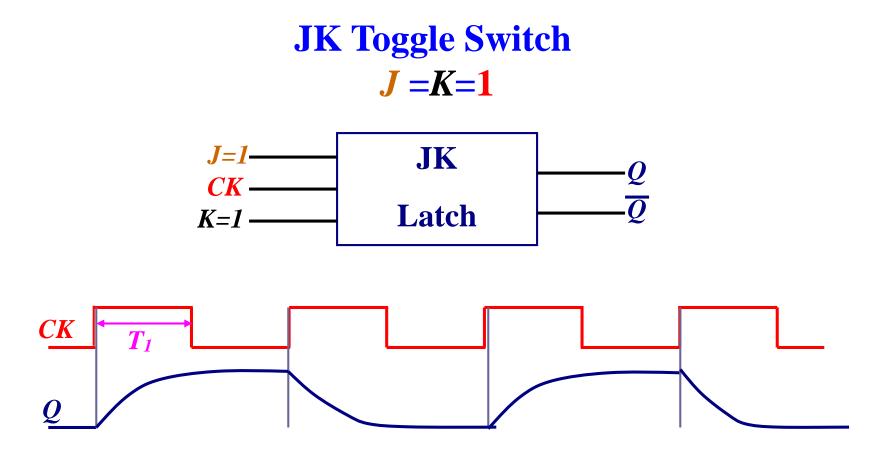

- Iff  $\tau_{JKP} > T_1$  (awkward to implement) Output Q changes only once per clock period

- » No not allowed input

- » Timing issues

- » Level sensitive

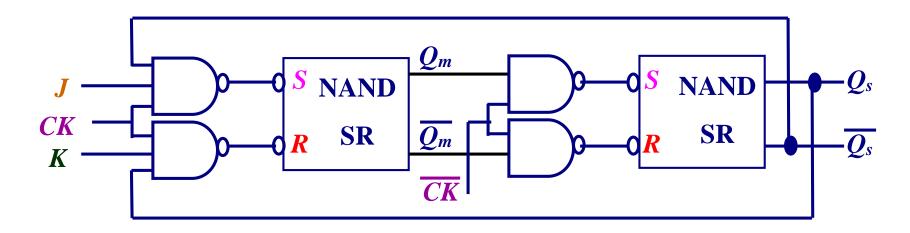

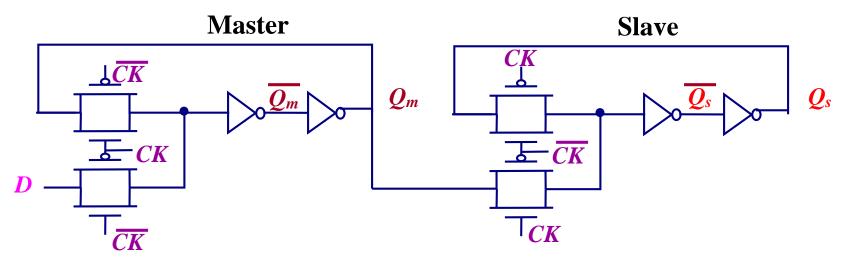

## **Master-Slave Flip-Flop**

- Two cascaded latches operating on opposite clock phases insures that the flip-flop is *never transparent*; i.e., a change occurring in the primary inputs is never reflected directly to the outputs.

- Eliminates oscillations when J = K = 1.

- Still level sensitive.

- Number of transistors:

- » NAND-based: 36

- » AOI-based: 28

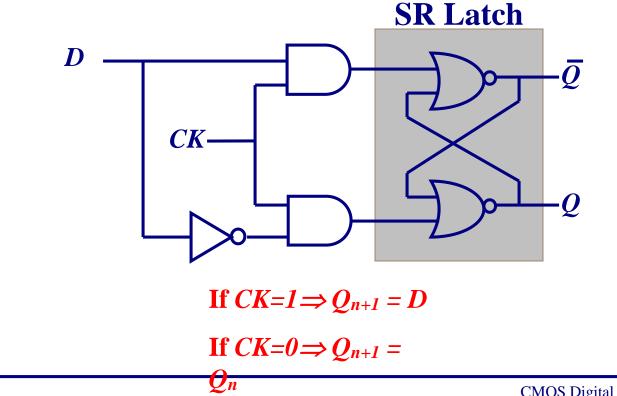

- D-latch is obtained by modifying the clocked NOR-based SR latch circuit. The circuit has a single input *D* which is connected to *S* input, and *D* is also inverted and connected to *R* input.

- The applications of D-latch are primarily for temporary storage of data or as a delay element.

30

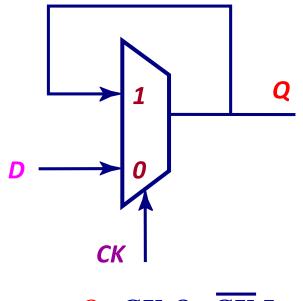

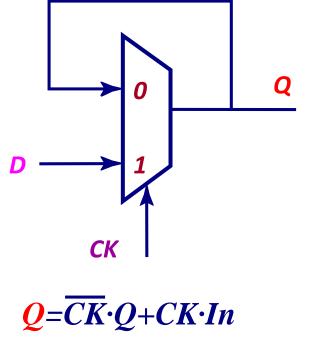

## **D-Latch (Cont.)**

• D-latch is a mux-based latch which can be represented as

$Q = CK \cdot Q + \overline{CK} \cdot In$

Negative latch (transparent when *CK*= 0) Positive latch (transparent when *CK*= 1)

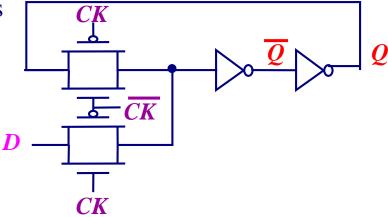

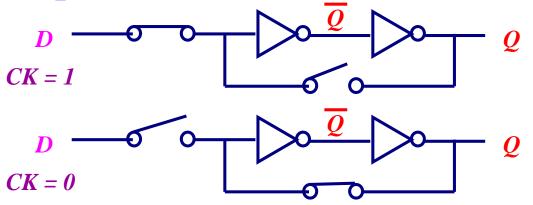

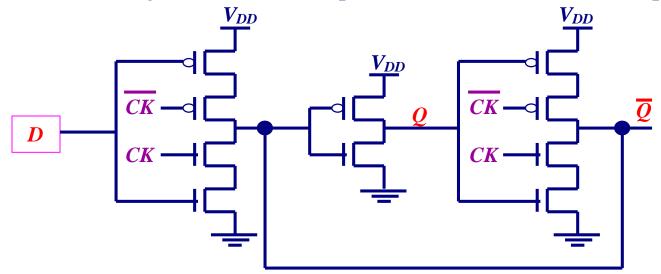

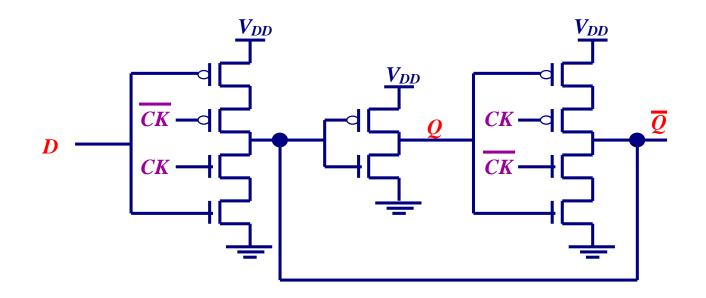

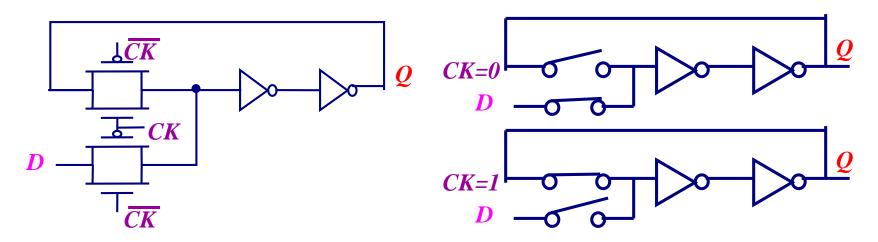

### **Implementation with Transmission Gates**

• Transmission gate **D-latch**: Use switch-like properties of

transmission gates

Operation: For CK = 1, Q<sub>n+1</sub>=D and Q<sub>n+1</sub>=D. A bit is loaded. For CK = 0, Q<sub>n+1</sub>=Q<sub>n</sub> and Q<sub>n+1</sub>=Q<sub>n</sub>. Thus, a bit is stored. Note that Propagation delay to Q is less than delay to Q. What about changes in D relative to changes in CK?

*Setup time* and *Hold time* relative to *CK*:  $1 \rightarrow 0$

- Device counts for TG-based reduced from AOI/OAI

- » AOI-based: 14

32

**» TG-based: 8 (plus 2 to invert clock)**

#### **Implementation with Three-State**

• Similar to the TG-based implementation, except as if connection between n and pFETs in a driving inverter and input side of a driven transmission gate is served. Require addition of inverter at input first.

33

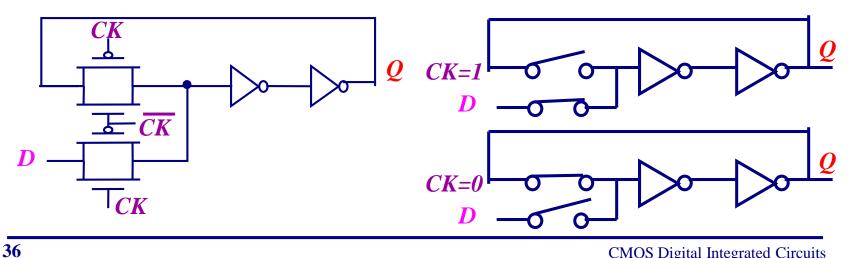

### **Implementation with Three-State (Cont.)**

- The first three-state inverter acts as the **input switch**. Accept the input signal when *CK* is high, the second three-state inverter is at its high impedance state, and Q = D.

- The first three-state inverter is **inactive** when the *CK* goes low, and the second three-state inverter completes the two-inverter loop, which preserves its state  $(Q_{n+1} = Q_n)$

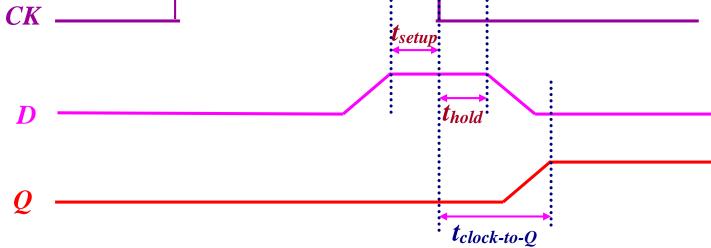

## **D-Latch Setup Time and Hold Time**

- **T**<sub>setup</sub>: time before the negative-CK edge the **D**-input has to be stable

- » The setup time is the delay between the data input of the register and the storage element. As the data takes a finite time to travel to the storage point, the clock cannot be changed until the correct data value appears.

- **T**<sub>hold</sub>: time after the negative-CK edge **D**-input has to remain stable •

- » The hold time relates to the delay between the clock input to the register and the storage element. That is, the data has to be held for this period while the clock travels to the point of storage.

- *T<sub>clock-to-Q</sub>*: Delay from the negative-CK edge to new value of Q output

35

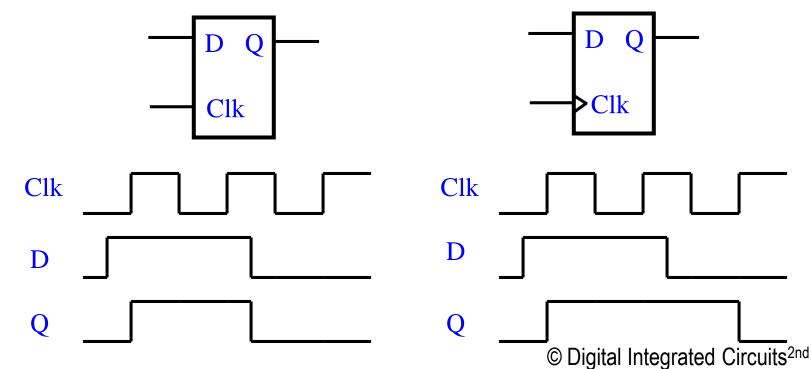

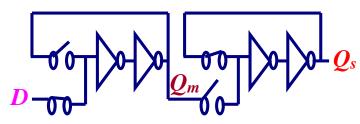

## **Edge Triggered Master-Slave Operation**

#### Negative D-Latch ?

**Positive D-Latch** ?

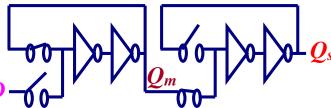

# **Positive Edge Triggered Master-Slave Flip-Flop**

For *CK*=0

For *CK*=1

37

*CK*=0: Master *Q<sub>m</sub>* tracks current *D*; Slave *Q<sub>s</sub>*=previous *D* sample

*CK*=0→1: Master stores *Q<sub>m</sub>* = *D*(new D sample).

3. CK=1:Master passes  $Q_m = D$  to Slave output  $Q_s$

4.  $CK=1 \rightarrow 0$ : Slave locks in new D, and Master  $Q_m$  begins tracking D.

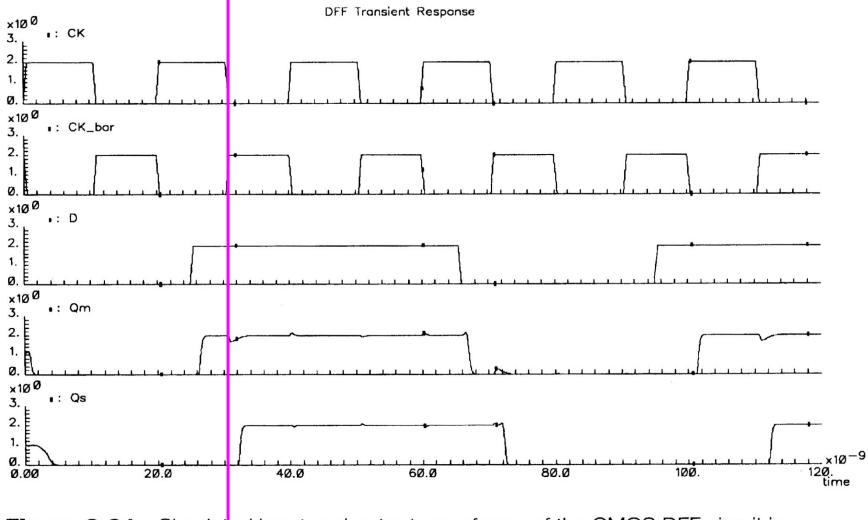

### **DFF Transient Response**

**Figure 8.31** Simulated input and output waveforms of the CMOS DFF circuit in Fig. 8.30.

38

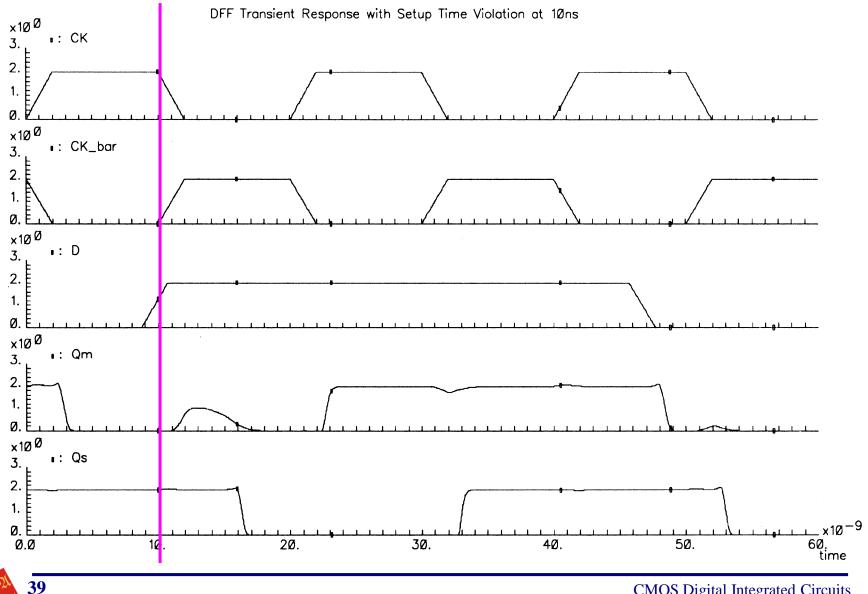

# **DFF Transient Response with Setup Time Violation**

**CMOS** Digital Integrated Circuits

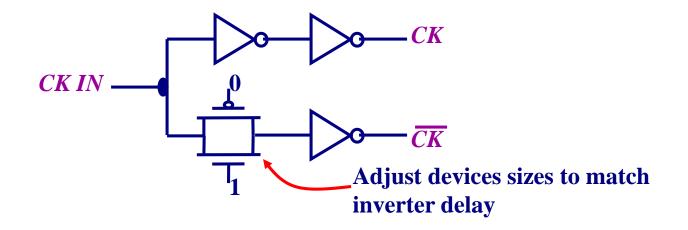

# D Flip-Flop Clock Skew Issues

- In a TG or three-state implemented flip-flop, if *CK* and *CK* changes are *skewed (misaligned) enough*, then a change in Master can immediately propagate into Slave violating the master-slave (edge-triggered) concept.

- If global or shared drivers used, can use the following to reduce skew:

• For the global case, skew can also arise due to interconnect delay.

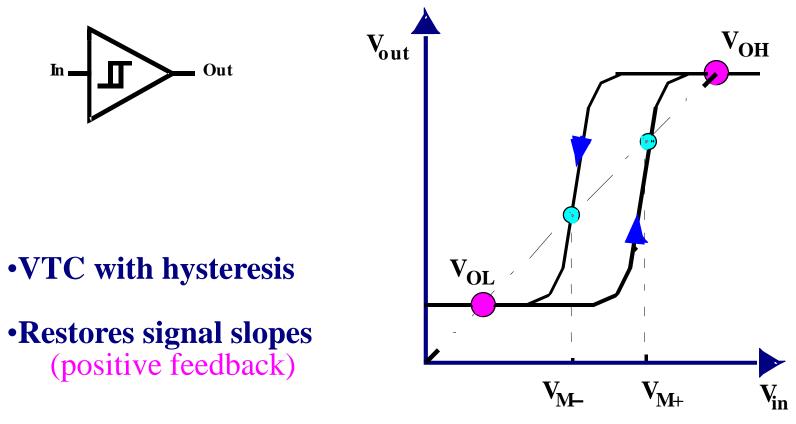

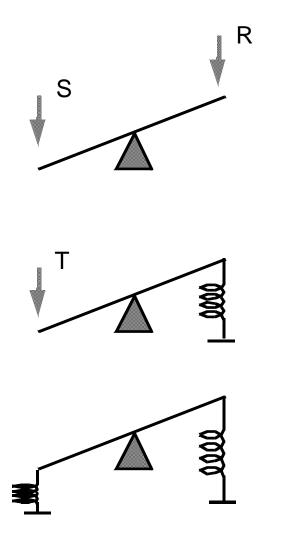

# Non-Bistable Sequential Schmitt Trigger

• The Schmitt trigger has an *inverter-like* voltage transfer characteristic, but with *two different threshold voltages* for increasing and decreasing input signals.

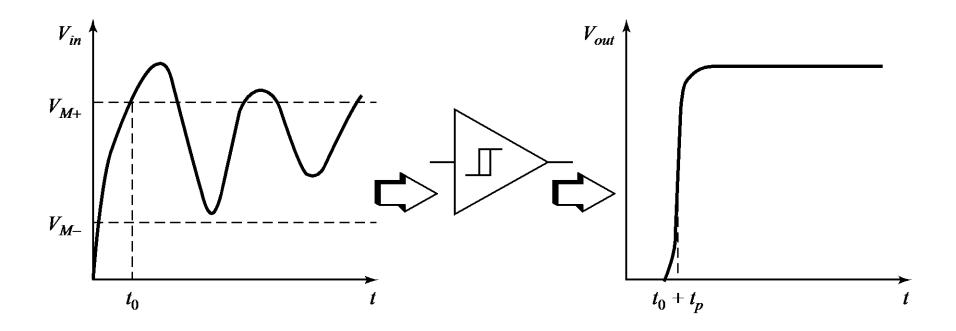

# Schmitt Trigger Application Noise Suppression

¢22 42

© Digital Integrated Circuits<sup>2nd</sup>

CMOS Digital Integrated Circuits

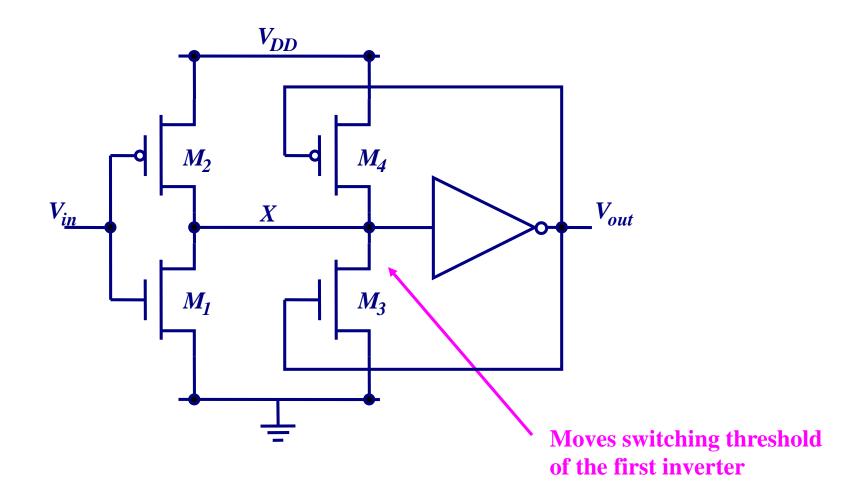

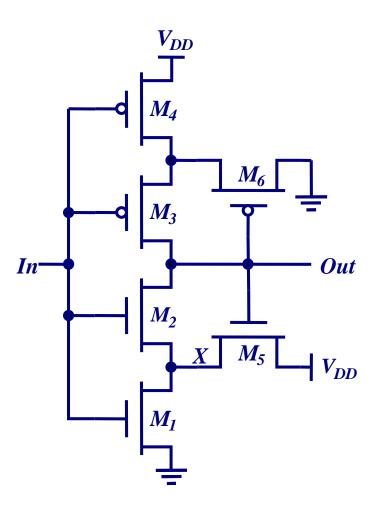

# Schmitt Trigger The Circuit(1)

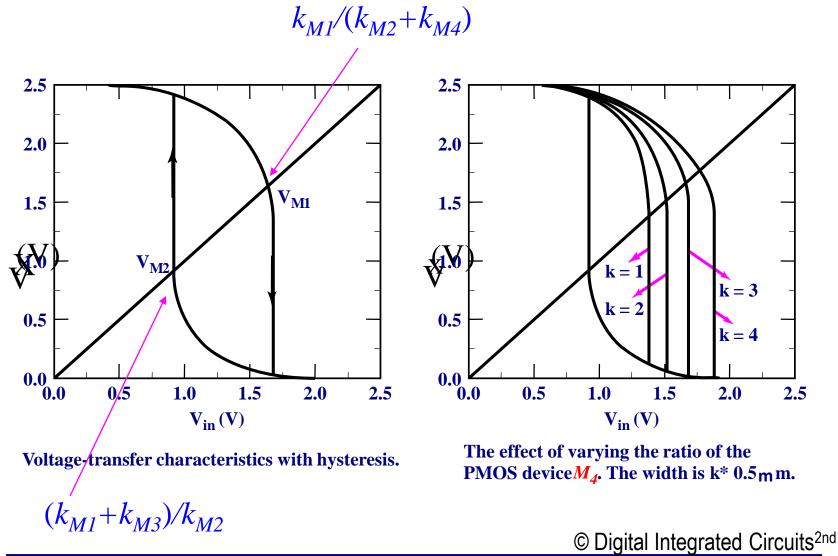

#### **Schmitt Trigger Simulated VTC**

CMOS Digital Integrated Circuits

44

### Schmitt Trigger The Circuit(2)

© Digital Integrated Circuits<sup>2nd</sup>

### **Multivibrator Circuits**

**Bistable Multivibrator** flip-flop, Schmitt Trigger

Monostable Multivibrator one-shot

Astable Multivibrator oscillator

© Digital Integrated Circuits<sup>2nd</sup>

46

**CMOS** Digital Integrated Circuits

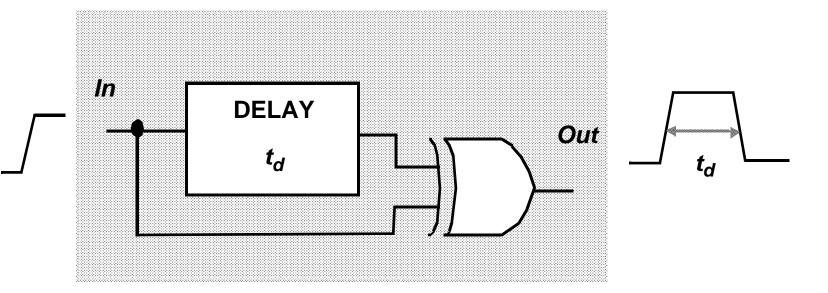

### **Transition-Triggered Monostable**

© Digital Integrated Circuits<sup>2nd</sup>

CMOS Digital Integrated Circuits

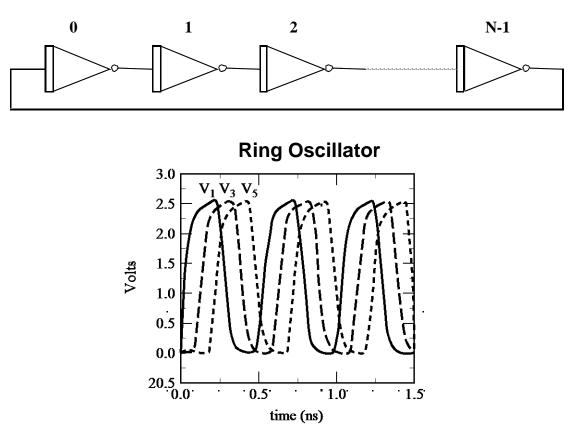

### **Astable Multivibrators (Oscillators)**

simulated response of 5-stage oscillator

© Digital Integrated Circuits<sup>2nd</sup>