## **CMOS Digital Integrated Circuits**

#### Lec 7

# **CMOS Inverters: Dynamic Analysis and Design**

1

**CMOS** Digital Integrated Circuits

#### **CMOS Inverters – Dynamic Analysis and Design**

#### **Goals**

- Understand the detail dynamic analysis of the CMOS inverter.

- Understand one set of design form CMOS equations.

- Understand the basic CMOS design process using the CMOS static and CMOS design form dynamic equations.

#### **CMOS Dynamic Analysis Capacitance Model for CMOS**

**CMOS** Digital Integrated Circuits

### **CMOS Dynamic Analysis Capacitance Model for CMOS**

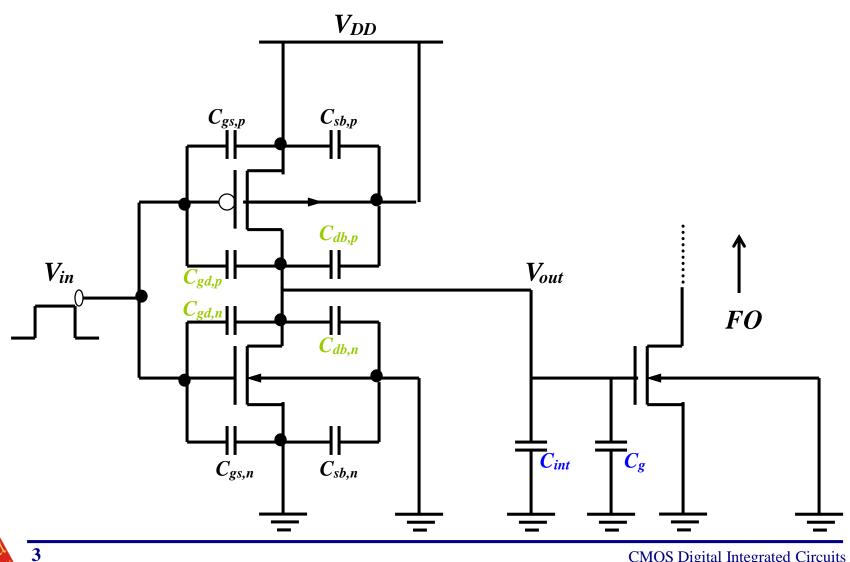

- The aggregate capacitance driven by the output node of a CMOS inverter is in detail working from left to right,

- $C_{load} = C_{input} + C_{int} + C_g$ in which

$C_{input} = C_{gd,n} + C_{gd,p} + C_{db,n} + C_{db,p}$  (intrinsic component)

*C<sub>int</sub>* = interconnect capacitance

(extrinsic component)

$C_g$  = thin-oxide capacitance over the gate area

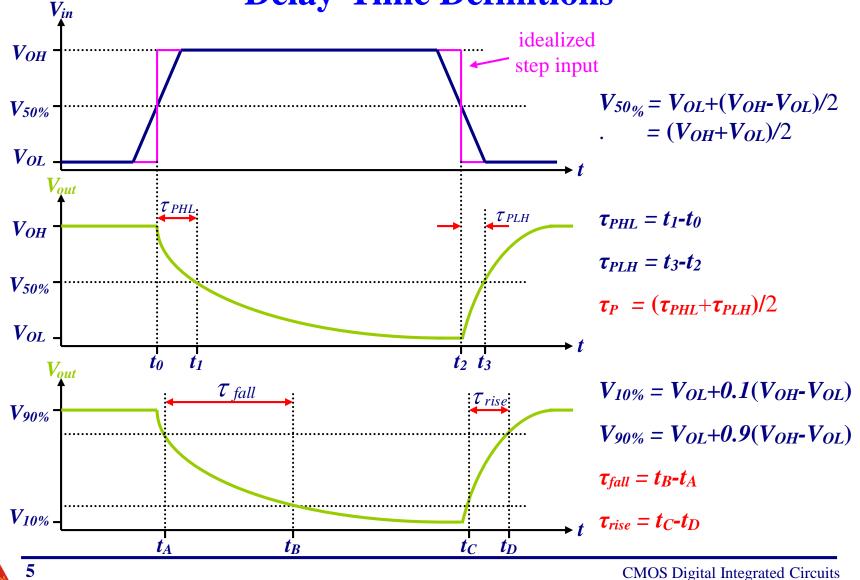

#### **CMOS Dynamic Analysis Delay-Time Definitions**

#### **CMOS Dynamic Analysis Delay-Time Calculation** (*First Order Estimates*)

• The simplest approach of calculating the propagation delay is based on estimating the *average capacitance current* during charge down/up.

$$\tau_{PHL} = \frac{C_{load} (V_{OH} - V_{50\%})}{I_{avg,HL}}$$

$$\tau_{PLH} = \frac{C_{load} (V_{50\%} - V_{OL})}{I_{avg,LH}}$$

where

$$I_{avg,HL} = \frac{1}{2} \Big[ i_C (V_{in} = V_{OH}, V_{out} = V_{OH}) + i_C (V_{in} = V_{OH}, V_{out} = V_{50\%}) \Big]$$

$$I_{avg,LH} = \frac{1}{2} \Big[ i_C (V_{in} = V_{OL}, V_{out} = V_{50\%}) + i_C (V_{in} = V_{OL}, V_{out} = V_{OL}) \Big]$$

#### CMOS Dynamic Analysis Delay-Time Calculation (*More Accurate*)(1/4)

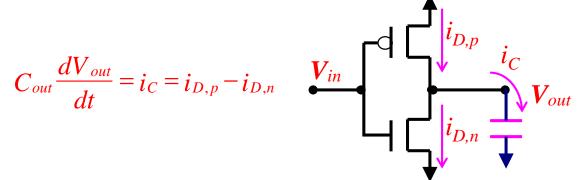

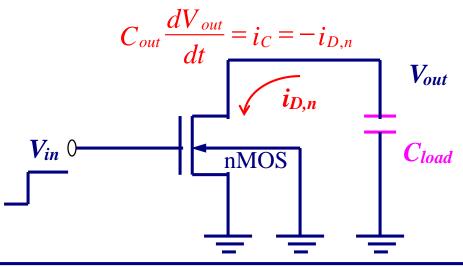

• The propagation delay can be found more accurately by solving the state equation of the output node. The current flowing through  $C_{load}$  is a function  $V_{out}$  as

•  $\tau_{PHL}$ : PMOS is off. The equivalent circuit during high-to-low output transition is

#### **CMOS Dynamic Analysis Delay-Time Calculation** (2/4)

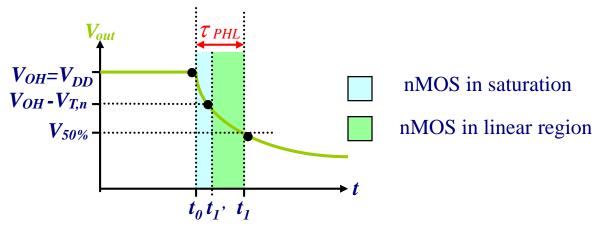

The nMOS operates in two regions, *saturation and linear*, during the interval of  $\tau_{PHL}$ .

• Saturation Region

$i_{D,n} = (k_n/2)(V_{in} - V_{T,n})^2 = (k_n/2)(V_{OH} - V_{T,n})^2$ » Plug  $i_{D,n}$  into  $C_{load} dV_{out}/dt = -i_{D,n}$ , and integrate both sides, we get

$t_1' - t_0 = 2C_{load} V_{T,n} / [k_n (V_{OH} - V_{T,n})^2]$

#### **CMOS Dynamic Analysis Delay-Time Calculation (3/4)**

• Linear Region

$$i_{D,n} = (k_n/2) [2(V_{in} - V_{T,n}) V_{out} - V_{out}^2]$$

=  $(k_n/2) [2(V_{OH} - V_{T,n}) V_{out} - V_{out}^2]$

» Plug  $i_{D,n}$  into  $C_{load} dV_{out}/dt = -i_{D,n}$ , and integrate both sides, we have

$$\boldsymbol{t}_{I} - \boldsymbol{t}_{I}' = \frac{C_{load}}{\kappa_{n}(V_{DD} - V_{T,n})} \ln\left(\frac{4(V_{DD} - V_{T,n})}{V_{50\%}}\right)$$

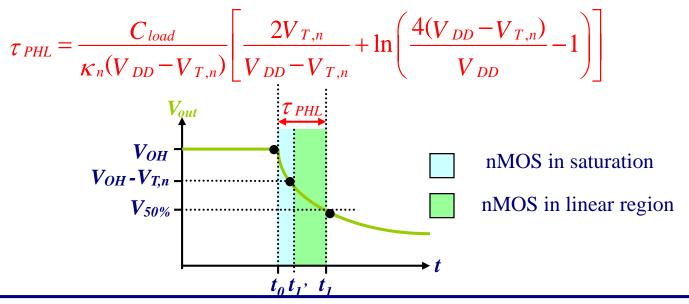

• Finally, since  $V_{OH} = V_{DD}$  and  $V_{OL} = 0$ , we have

#### **CMOS Dynamic Analysis Delay-Time Calculation** (4/4)

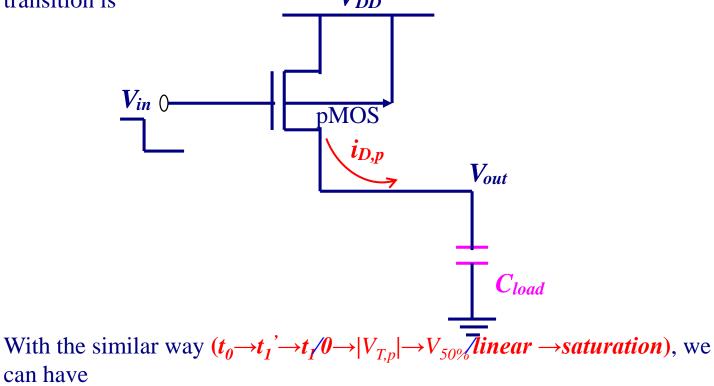

•  $\tau_{PLH}$ : NMOS is off. The equivalent circuit during low-to-high output transition is  $V_{DD}$

$$\tau_{PLH} = \frac{C_{load}}{\kappa_{p}(V_{DD} - |V_{T,p}|)} \left[ \frac{2|V_{T,p}|}{V_{DD} - |V_{T,p}|} + \ln\left(\frac{4(V_{DD} - |V_{T,p}|)}{V_{DD}} - 1\right) \right]$$

#### **CMOS Inverter Design**

- Design for Performance

- Keep capacitance small

- Increase transistor size

- » Watch out for self-loading!

- Increase *V*<sub>DD</sub> (????)

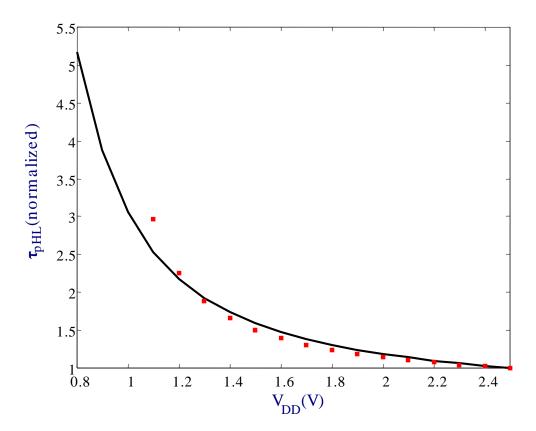

#### **CMOS Inverter Design Delay as a Function of** *VDD*

•  $V_{DD}$  increases  $\rightarrow \tau_{PHL}/\tau_{PLH}$  decreases. However, the power consumption also increases.

#### CMOS Inverter Design Device Sizing (1/5)

**CMOS** Digital Integrated Circuits

#### CMOS Inverter Design Device Sizing (2/5)

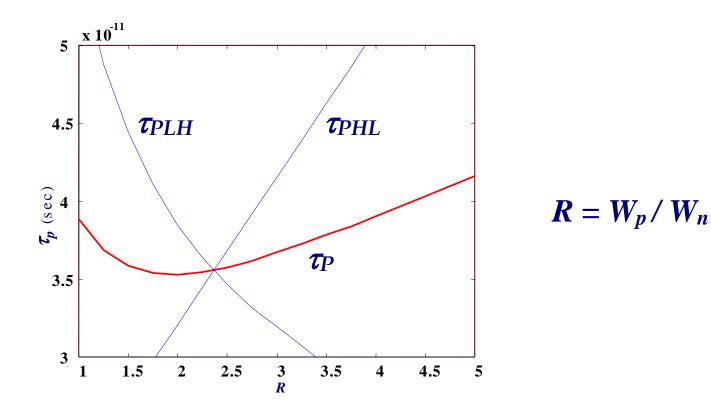

#### NMOS/PMOS Ratio

**CMOS** Digital Integrated Circuits

#### CMOS Inverter Design Device Sizing (3/5)

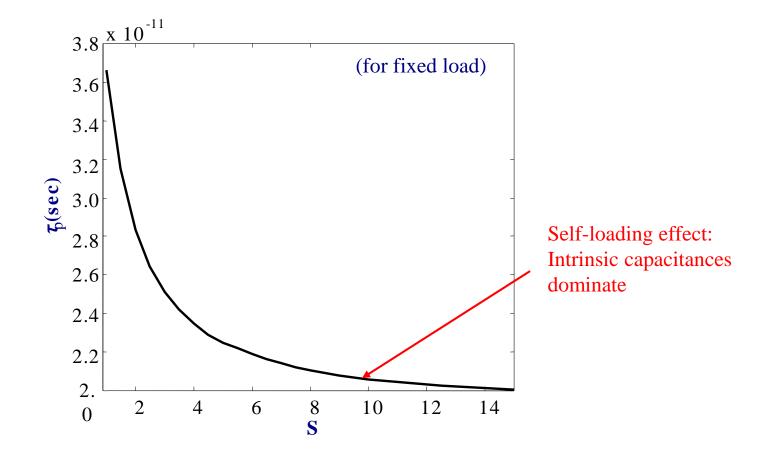

**Self-Loading Effect**

$$C_{load} = \frac{C_{gd,n}(W_n) + C_{gd,p}(W_p) + C_{db,n}(W_n) + C_{db,p}(W_p) + C_{int} + C_g}{= f(W_n, W_p)}$$

- Using the junction capacitance expressions in Chapter 3, we have  $C_{db,n} = (W_n D_{drain} + x_j D_{drain}) C_{j0,n} K_{eq,n} + (W_n + 2D_{drain}) C_{jsw,n} K_{eq,n}$   $C_{dp,n} = (W_p D_{drain} + x_j D_{drain}) C_{j0,p} K_{eq,p} + (W_p + 2D_{drain}) C_{jsw,p} K_{eq,p}$

- Therefore,  $C_{load}$  can be rewritten as

$$C_{load} = \alpha_0 + \alpha_n W_n + \alpha_p W_p$$

where

$$\alpha_0 = D_{drain}(2C_{jsw,n}K_{eq,n} + 2C_{jsw,p}K_{eq,p} + x_jC_{j0,n}K_{eq,n} + x_jC_{j0,p}K_{eq,p}) + C_{int} + C_g$$

$$\alpha_n = K_{eq,n}(C_{j0,n}D_{drain} + C_{jsw,n})$$

$$\alpha_p = K_{eq,p}(C_{j0,p}D_{drain} + C_{jsw,p})$$

#### CMOS Inverter Design Device Sizing (4/5)

• Therefore,  $\tau_{PHL}$  and  $\tau_{PLH}$  are

$$\tau_{PHL} = \left(\frac{\alpha_0 + \alpha_n W_n + \alpha_p W_p}{W_n}\right) \times \left(\frac{L_n}{\mu_n C_{ox} (V_{DD} - V_{T,n})}\right) \times \left[\frac{2V_{T,n}}{V_{DD} - V_{T,n}} + \ln\left(\frac{4(V_{DD} - V_{T,n})}{V_{DD}} - 1\right)\right]$$

$$\tau_{PLH} = \left(\frac{\alpha_0 + \alpha_n W_n + \alpha_p W_p}{W_p}\right) \times \left(\frac{L_p}{\mu_n C_{ox} (V_{DD} - |V_{T,p}|)}\right) \times \left[\frac{2|V_{T,p}|}{V_{DD} - |V_{T,p}|} + \ln\left(\frac{4(V_{DD} - |V_{T,p}|)}{V_{DD}} - 1\right)\right]$$

• The ratio between the channel widths  $W_n$  and  $W_p$  is usually dictated by other design constraints such as noise margins and the logic inversion threshold. Let's this transistor *aspect ratio* be defined as  $R \equiv W_p/W_n$ . Then, the propagation delay can be represented as

$$\tau_{PHL} = \Gamma_n \left( \frac{\alpha_0 + (\alpha_n + R\alpha_p)W_n}{W_n} \right)$$

$$\tau_{PLH} = \Gamma_p \left( \frac{\alpha_0 + (\frac{\alpha_n}{R} + \alpha_p)W_p}{W_p} \right)$$

#### CMOS Inverter Design Device Sizing (5/5)

• As we continue increase the values of  $W_n$  and  $W_p$ , the propagation delay will asymptotically approach a limit value for lager  $W_n$  and  $W_p$ ,

$$\mathcal{T}_{PHL}^{limit} = \Gamma_n(\alpha_n + R\alpha_p)$$

$$\mathcal{T}_{PLH}^{limit} = \Gamma_p \left(\frac{\alpha_n}{R} + \alpha_p\right)$$

• The propagation delay times cannot be reduced beyond the above limits, and the limit is *independent* of the extrinsic capacitances.

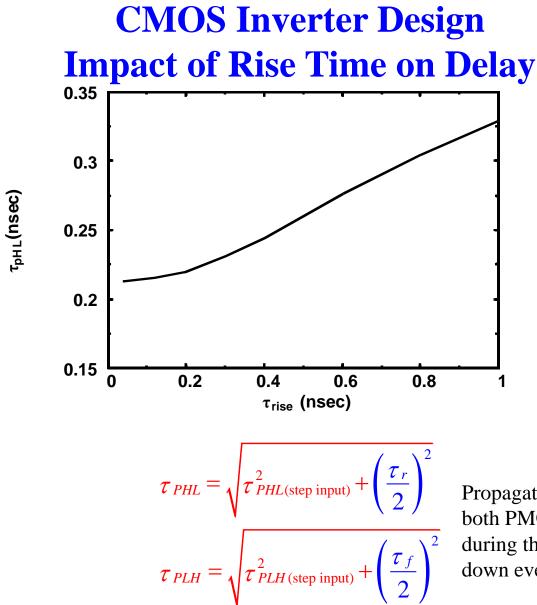

Propagation delay increases since both PMOS and NMOS are on during the charge-up and chargedown events.

#### **CMOS Inverter Design Impact of Channel Velocity Saturation**

• The drain current is *linearly dependent on*  $V_{GS}$

$$I_{sat} = \kappa W_n \left( V_{GS} - V_T \right)$$

Propagation delay only has a weak dependence on the supply voltage  $V_{DD}$

$$\tau_{PHL} \approx \frac{C_{load}V_{50\%}}{I_{sat}} = \frac{C_{load}\left(V_{DD}/2\right)}{\kappa W_n\left(V_{DD}-V_T\right)}$$

### **CMOS Dynamic Analysis Dynamic Power Dissipation** (1/2)

• The dynamic power dissipation can be derived as follows.

$$P_{dyn,avg} = V_{DD} I_{DD,avg}$$

• With  $I_{DD,avg}$  taken over one clock period T. The capacitance current which equals the current from the power supply (assuming  $I_{Dn} = 0$  during charging) is

$$I_D = C_{load} \frac{dV_{out}}{dt}$$

• Rearranging and integrating over one clock period *T*

$$\int_0^T I_D dt = \int_0^{V_{DD}} C_{load} \, dV_{out}$$

• Gives

$$I_{DD,avg} T = C_{load} V_{DD}$$

#### **CMOS Dynamic Analysis Dynamic Power Dissipation** (2/2)

• Solving for *I<sub>DD,avg</sub>* and substituting in *P<sub>avg</sub>*:

$$P_{avg} = \frac{1}{T} C_{load} V_{DD}^2 = C_{load} V_{DD}^2 f$$

- It should be noted here the our simple  $C_{load}$  may underestimate the power dissipated.

- In terms of SPICE simulation, the authors' offer a circuit called power meter.