Alexandria University

Faculty of Engineering

Electrical Engineering Department

Fall Mid-term Exam, November 2016

جامعة الإسكندرية كلية الهندسة قسم الهندسة الكهربية امتحان نصف الفصل الدراسي الأول (نوفمبر ٢٠١٦)

Course Title and Code Number:

Digital Integrated Circuits (EE 431)

Fourth Year (Communications and Electronics)

Time Allowed: 90 Mins

اسم المقرر والرقم الكودي له: الدوائر المتكاملة الرقمية (EE 431) السنة الدراسية الرابعة (اتصالات و الكترونيات) الزمن: ٩٠ دقيقة

## **Answer the following questions:**

(25 marks) (10 marks)

## **Question 1:**

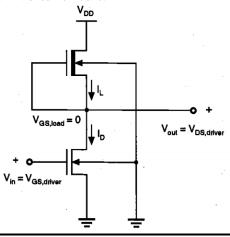

**Derive** and calculate the critical voltages ( $V_{OL}$ ,  $V_{OH}$ ,  $V_{IL}$ ,  $V_{IH}$ ) and find the noise margins of the following depletion-load inverter circuit:

$$V_{DD} = 5 \text{ V}$$

$V_{T0,driver} = 1.0 \text{ V}$

$V_{T0,load} = -3.0 \text{ V}$

$(W/L)_{driver} = 2$ ,  $(W/L)_{load} = 1/3$

$k_{n,driver}' = k_{n,load}' = 25 \text{ }\mu\text{A}/\text{V}^2$

$\gamma = 0.4 \text{ }\text{V}^{1/2}$

$\phi_F = -0.3 \text{ V}$

**Question 2:**

(10 marks)

A CMOS technology has the following parameters:

$$\mu_n C_{ox} = 120 \,\mu\text{A/V}^2$$

$\mu_p C_{ox} = 60 \,\mu\text{A/V}^2$

$L = 0.6 \,\mu\text{m}$  for both nMOS and pMOS devices,

$V_{T0,n} = 0.8 \text{ V}$   $V_{T0,p} = -1.0 \text{ V}$  $W_{min} = 1.2 \text{ } \mu\text{m}$

Design a CMOS inverter by determining the channel widths  $W_n$ , and  $W_p$  of the nMOS and pMOS transistors, to meet the following performance specifications (**Derive** all equations you need):

- $V_{th}=1.5V$  for  $V_{DD}=3V$

- Propagation delay times  $\tau_{PHL} \le 0.2$  ns and  $\tau_{PLH} \le 0.15$  ns.

- A falling delay of 0.35 ns for an output transition from 2 V to 0.5 V.

Assume a combined output load capacitance of 300fF and ideal step input.

Question 3: (5 marks)

Consider a uniform polysilicon line with a length l of  $1000~\mu m$  and a width W of  $4~\mu m$ . Assuming a sheet resistance value of  $30~\Omega/square$ , a parallel plate unit area capacitance of  $0.066~fF/\mu m^2$ , and a fringing field unit length capacitance of  $0.046~fF/\mu m$ . Calculate the propagation delay of the poly interconnect line using the following models:

- a) Lumped RC model.

- b) T model.

- c) Distributed RC ladder with N=5.

- d) Distributed RC ladder with  $N=\infty$ .

Good Luck

Examiner: Dr. Mohammed Morsy