# Part II: 8086/8088 Hardware Specifications and Interfacing

Dr. Mohammed Morsy

### Introduction

### This course covers:

- Assembly language Programming (Intel x86)

- General system design concepts, devices and support chips

- Specifically covers architecture of the Intel microprocessors

- Hardware configuration and control of: Common microprocessor support chips, e.g. Interrupt controller, Popular I/O devices, e.g. UART, parallel IO, timers

### This part covers:

- Intel 8086, 8088 processor hardware specifications

- Memory Interfacing, basic I/O interfacing, Interrupts

### Textbook:

o Barry B. Brey, 'The Intel Microprocessors', Fifth Edition

# Systems Overview

- General Purpose Computing Systems

- Personal Computers, laptops, workstations, mainframes and servers

- Embedded Systems

- It is a system whose principal function is not computational, but which is con-trolled by a computer embedded within it

- Consumer electronics such as Cell phones, pagers, digital cameras, camcorders, PDAs, DVD players, calculators

- Automobiles Transmission control, cruise control, fuel injection, antilock brakes, active suspension

- Cyber-Physical Systems

- o Integrations of computation, networking, and physical processes

### Microprocessors

- The CPU is a unit that fetches and processes a set of general-purpose instructions

- The CPU instruction set includes instructions for data transfer, ALU operations, stack operations, input and output (IO) operations and program control, sequencing and supervising operations

- A microprocessor is a single VLSI chip that has a CPU and may also have other units (e.g. caches, floating point processing arithmetic unit, pipelining and super-scaling units) that are additionally present and result in faster processing of instructions.

- Examples: Intel 8085, Intel x86 processors, Motorola 68HCxxx, Sun Sparc, IBM PowerPC etc.

### Microcontrollers

- A microcontroller is a single chip unit which, though having limited computational capabilities, possesses enhanced input-output capabilities and a number of on-chip functional units

- Particularly suited for use in embedded systems for real-time control applications with on-chip program memory and devices

- Common peripherals include serial communication devices, timers, counters, pulse-width modulators, analog-to-digital and digital-to-analog convertors

- Examples: Motorola 68HC11xx, HC12xx, HC16xx, Intel 8051, 80251, PIC 16F84, PIC18, ARM9, ARM7, Atmel AVR etc.

### Digital Signal Processor

- Essential for systems that require large number of operations on digital signals, which are the digital encoding of analog signals like video and audio

- They carry out common signal processing tasks like signal filtering, transformations or combinations

- Used widely in image processing applications, multimedia, audio, video, HDTV,

- DSP modem and telecommunication processing systems.

- They perform math-intensive operations, including operations like multiplication and division.

- Examples: TI TMS320Cxx, Analog Devices SHARC, Motorola 5600xx, etc.

- Programmable Logic Devices (PLD)/ Field Programmable Gate Arrays (FPGA)

- Contains general purpose logic elements that can be programmed to implement desired functionality, very flexible for implementing custom logic circuits

- PLD usually are smaller and contain programmable gates like AND/OR arrays

- FPGAs provide lot more functionality and can be used to implement complex designs

- FPGAs can have on-chip microprocessors, memory, DSP, communication devices

- Examples: Xilinx Virtex, Spartan series FPGAs, Actel, Altera, Lattice, QuickLogic

- Application Specific Integrated Circuits (ASICs)/ System-on-a-chip (SOCs)

- Custom designed VLSI chips that perform the required function

- o Functionality can be integrated using IP (Intellectual property) cores

- General purpose processors are also available as IP cores and can be integrated on the chip

- Embedded processors are available from ARM, Intel, Texas Instruments and various other vendors

- Only feasible for high volume, relatively high cost systems as initial costs and time-to-market can be significant

# Intel x86 Family Evolution

- In this course we focus on the Intel x86 architecture, associated peripherals and assembly language programming. However, concepts covered apply to other logic families.

- **4**004:

- 4-bit microprocessor

- 4KB main memory

- 45 instructions

- PMOS technology

- 50 KIPS

- **8008:** (1971)

- 8-bit version of 4004

- 16KB main memory

- 48 instructions

- NMOS technology

- 8080: (1973)

- 8-bit microprocessor.

- 64KBmain memory.

- 2 microseconds clock cycle time; 500,000 instructions/sec.

- 10X faster than 8008.

# Intel x86 Family Evolution

- 8085: (1977)

- o 8-bit microprocessor upgraded version of the 8080.

- o 64KB main memory.

- 1.3 microseconds clock cycle time; 769,230 instructions/sec.

- 246 instructions.

- Intel sold 100 million copies of this 8-bit microprocessor.

- 8086: (1978) 8088 (1979)

- o 16-bitmicroprocessor.

- o 1MB main memory.

- o 2.5 MIPS (400 ns).

- 4- or 6-byte instruction cache.

- Other improvements included more registers and additional instructions.

- 80286: (1983)

- 16-bit microprocessor very similar in instruction set to the 8086.

- o 16MB main memory.

- 4.0 MIPS (250 ns/8MHz).

# Intel x86 Family Evolution

- Report the Intel x86 processor family enhancements showing the following:

- Fabrication technology, transistor count, and chip area.

- Operating frequency, bus width, and throughput in MIPS.

- Notable enhancements and breakthroughs

- o Applications and limitations of each generation

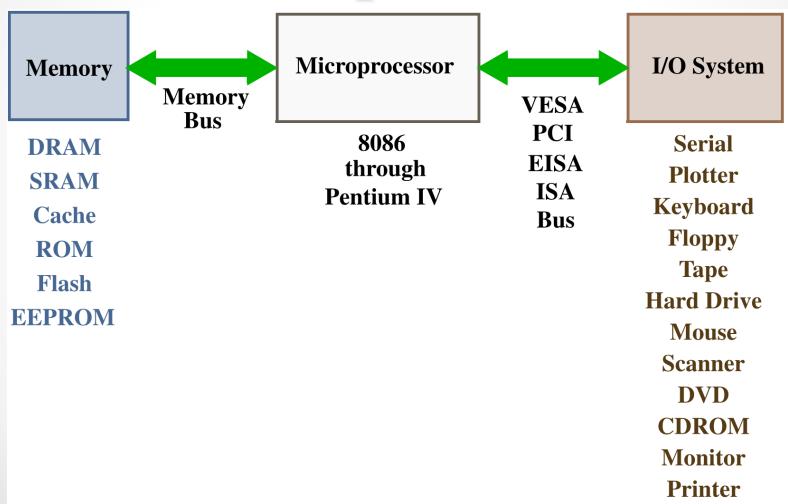

# Processor Basic Components

# Processor Basic Architecture (Von Neumann Bus Architecture)

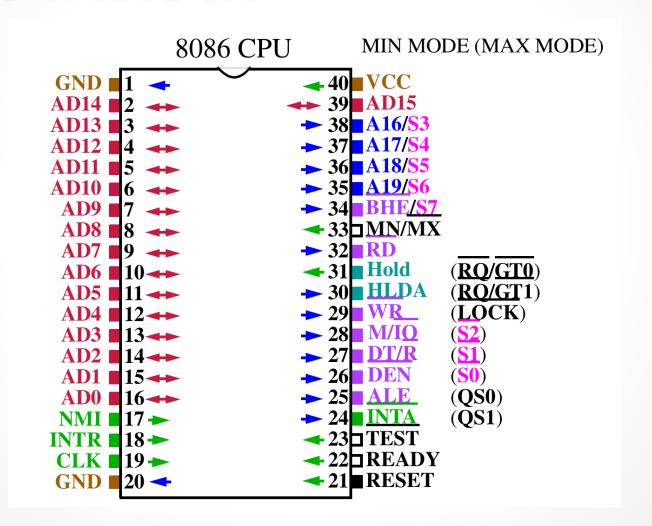

# 8086/88 Device Specifications

- Both are packaged in DIP (Dual In-Line Packages)

- 1. The 8086 has 16-bit data bus  $(AD_0-AD_{15})$ , but the 8088 has 8-bit data bus  $(AD_0-AD_7)$ .

- 2. The 8086 has  $M/\overline{IO}$ , but the 8088 has  $IO/\overline{M}$

- 8086 draws a maximum supply current of 360 mA, 8088 draws a maximum supply current of 340 mA.

- Both microprocessors operates in ambient temperature between 0°C and 70°C.

- Extended temperature-range versions are available

### 8086 Pinout

**OAD15-AD0**

Multiplexed address(ALE=1)/data bus(ALE=0).

○*A19/S6-A16/S3* (multiplexed)

High order 4 bits of the 20-bit address OR status bits S6-S3.

$\bigcirc M/IO$

Indicates if address is a Memory or IO address.

$\bigcirc RD$

When 0, data bus is driven by memory or an I/O device.

$\bigcirc WR$

Microprocessor is driving data bus to memory or an I/O device. When 0, data bus contains valid data.

OALE (Address latch enable)

When 1, address data bus contains a memory or I/O address.

$\bigcirc DT/R$  (Data Transmit/Receive)

Data bus is transmitting/receiving data.

ODEN (Data bus Enable)

Activates external data bus buffers.

$\bigcirc$  S7, S6, S5, S4, S3,  $\overline{S2}$ ,  $\overline{S1}$ ,  $\overline{S0}$

**S7**: Logic 1, S6: Logic 0.

**S5**: Indicates condition of IF flag bits.

*S4-S3*: Indicate which segment is accessed during current bus cycle:

|   | S4 | S3 | Function           |

|---|----|----|--------------------|

| _ | 0  | 0  | Extra segment      |

| _ | 0  | 1  | Stack segment      |

|   | 1  | 0  | Code or no segment |

|   | 1  | 1  | Data segment       |

S2, S1, S0: Indicate function of current bus cycle (decoded by 8288).

| <u>S2</u> | <u>51</u> | <u>50</u> | Function      | <u>S2</u> | <del>S</del> 1 | <del>S</del> 0 | Function     |

|-----------|-----------|-----------|---------------|-----------|----------------|----------------|--------------|

| 0         | 0         | 0         | Interrupt Ack | 1         | 0              | 0              | Opcode Fetch |

| 0         | 0         | 1         | I/O Read      | 1         | 0              | 1              | Memory Read  |

| 0         | 1         | 0         | I/O Write     | 1         | 1              | 0              | Memory Write |

| 0         | 1         | 1         | Halt          | 1         | 1              | 1              | Passive      |

#### **OINTR**

When 1 and IF=1, microprocessor prepares to service interrupt. INTA becomes active after current instruction completes.

#### **OINTA**

Interrupt Acknowledge generated by the microprocessor in response to INTR. Causes the interrupt vector to be put onto the data bus.

#### ONMI

Non-maskable interrupt. Similar to INTR except IF flag bit is not consulted and interrupt is vector 2.

#### O CLK

Clock input must have a duty cycle of 33% (high for 1/3 and low for 2/3s)

#### O VCC/GND

Power supply (5V) and GND (0V)

#### $\bigcirc MN/MX$

Select minimum (5V) or maximum mode (0V) of operation.

#### OBHE

Bus High Enable. Enables the most significant data bus bits  $(D_{15}-D_8)$  during a read or write operation.

#### **OREADY**

Used to insert wait states (controlled by memory and IO for reads/writes) into the microprocessor.

#### **ORESET**

Microprocessor resets if this pin is held high for 4 clock periods.

Instruction execution begins at FFFF0H and IF flag is cleared.

#### **OTEST**

An input that is tested by the WAIT instruction.

Commonly connected to the 8087 coprocessor.

#### **OHOLD**

Requests a direct memory access (DMA). When 1, microprocessor stops and places address, data and control bus in high-impedance state.

### ○*HLDA* (Hold Acknowledge)

Indicates that the microprocessor has entered the hold state.

### $\bigcirc \overline{RO}/\overline{GT1}$ and $\overline{RO}/\overline{GT0}$

Request/grant pins request/grant direct memory accesses (DMA) during maximum mode operation.

#### **OLOCK**

Lock output is used to lock peripherals off the system. Activated by using the LOCK: prefix on any instruction.

### $\bigcirc$ QS1 and QS0

The queue status bits show status of internal instruction queue. Provided for access by the numeric coprocessor (8087).

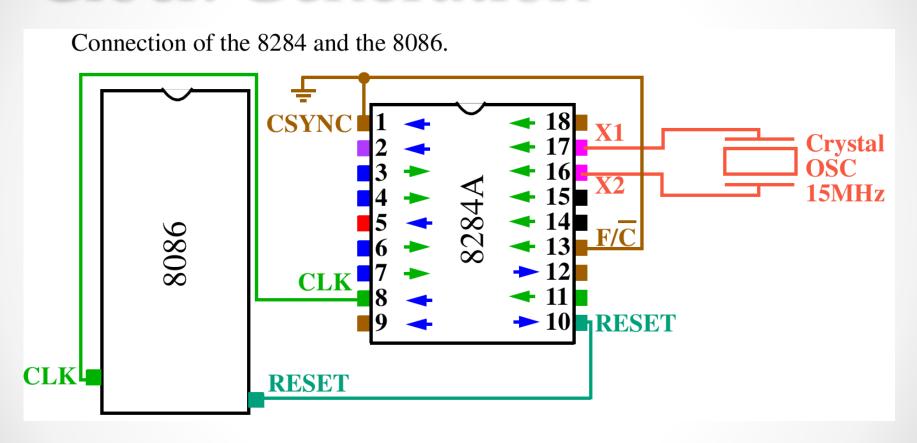

### Clock Generation

- The 8284A is an ancillary component to the 8086/8088

- Clock generation

- RESET synchronization

- READY synchronization

- Peripheral clock signal

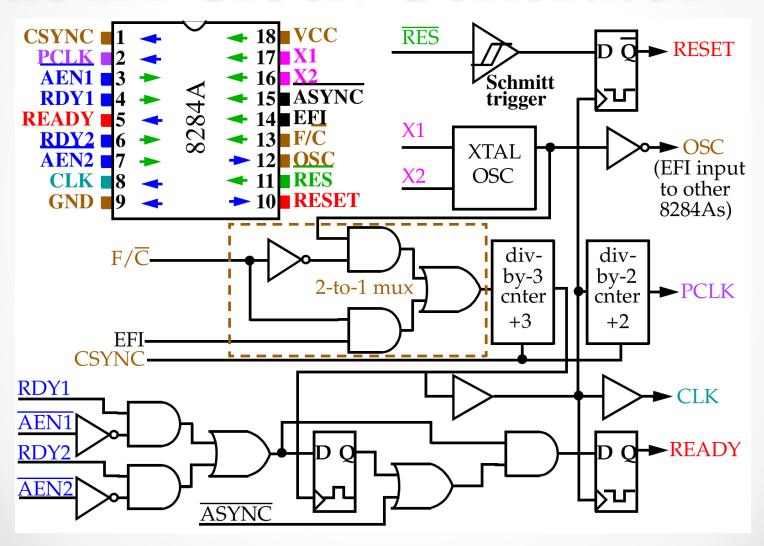

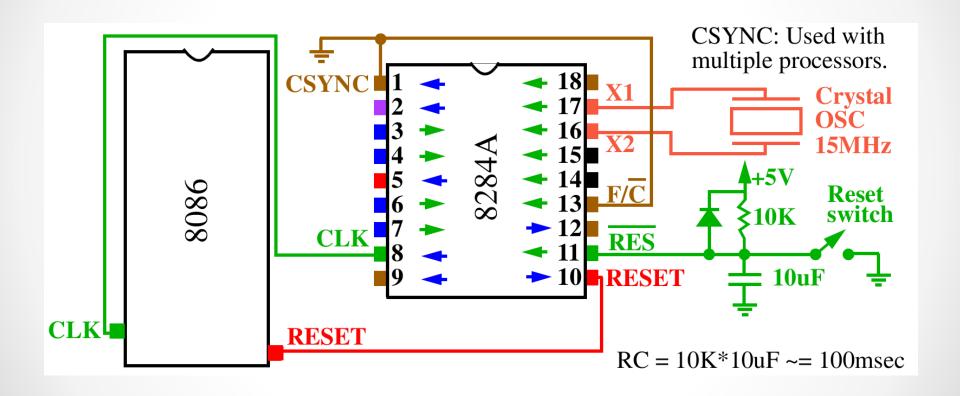

### Clock Generation

Crystal is connected to X1 and X2.

XTAL OSC generates square wave signal at crystal's frequency which feeds:

- An inverting buffer (output OSC) which is used to drive the EFI input of other 8284As.

- 2-to-1 MUX:  $F/\bar{C}$  selects XTAL or EFI external input.

The MUX drives a divide-by-3 counter (15MHz to 5MHz).

### This drives:

- The READY flip-flop (READY synchronization).

- A second divide-by-2 counter (2.5MHz clk for peripheral components).

- The RESET flip-flop.

- CLK which drives the 8086 CLK input.

- RESET: Negative edge-triggered flip-flop applies the RESET signal to the 8086 on the falling edge

- The 8086 samples the RESET pin on the rising edge

- Correct reset timing requires that the RESET input to the microprocessor becomes a logic 1 NO LATER than 4 clocks after power up and stay high for at least 50µs

**2**6

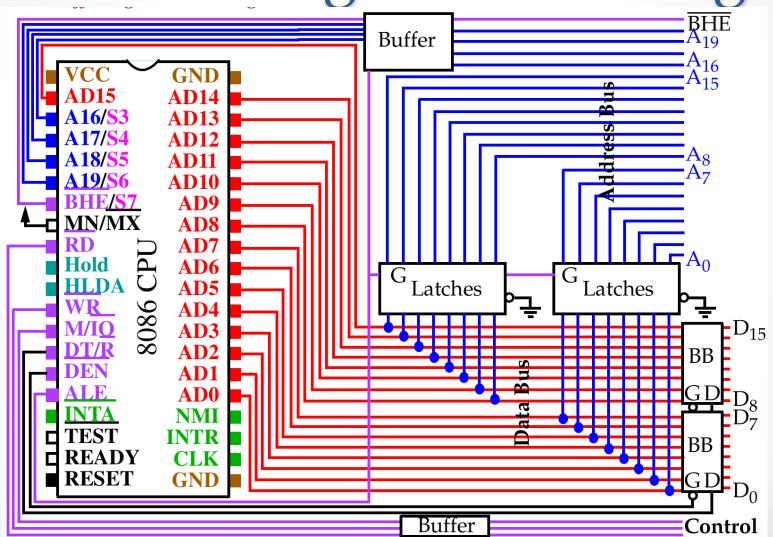

# Bus Buffering and Latching

- For very large systems, the buses are buffered.

WHY?

- The address/data bus are multiplexed to save the number of pins required for the 8086/8088 IC.

- They must be demultiplexed. WHY?

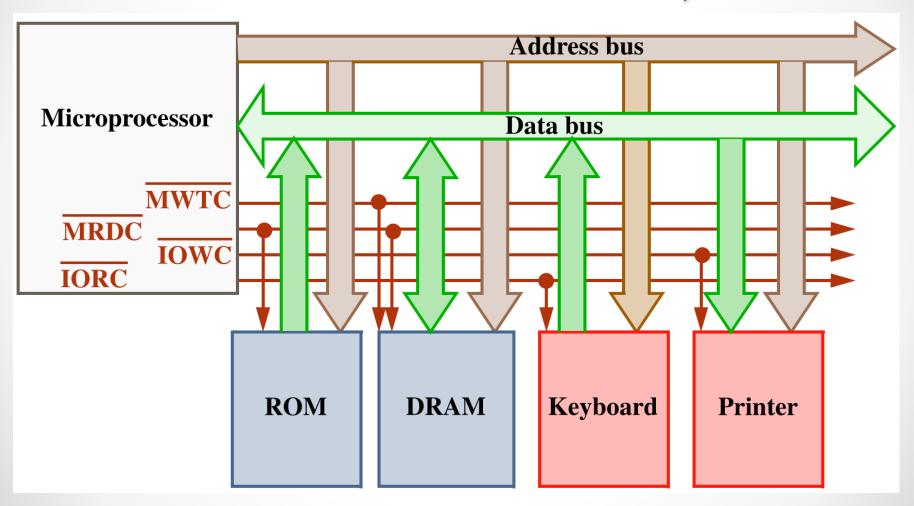

- All computer systems have three buses:

- Address bus

- o Data bus

- o Control bus

- These buses must be present to interface memory and I/O.

# Bus Buffering and Latching

- Computer systems have three buses: Address, Data, and Control

- The Address and Data bus are multiplexed (shared) due to pin limitations on the 8086.

- The ALE pin is used to control a set of latches.

- All signals MUST be buffered

- Buffered Latches for A0-A15

- $\circ$  Control and A16-A19+  $\overline{BHE}$  are buffered separately.

- Data bus buffers must be bidirectional buffers.

- In an 8086 system, the memory is designed with two banks

- High bank contains the higher order 8-bits and low bank the lower order 8-bits

- Data can be transferred as 8 bits from either bank or 16-bits from both

- $\circ$   $\overline{BHE}$  pin selects the high-order memory bank

## Bus Buffering and Latching

# Timing In General

- The 8086/8088 uses the memory and I/O in periods of time called bus cycle.

- Each bus cycle equal to 4 system-clocking periods (T states).

- If the clock is operated at 5 MHz, one bus cycle is completed in 800ns.

- The 8086/8088 reads or writes data at the rate of 1.25 million times a second.

# Timing In General

- During the first clocking period (T<sub>1</sub>):

- The address is placed on the Address/Data bus.

- $\circ$  Control signals (M/ $\overline{IO}$ , ALE and DT/ $\overline{R}$ ) specify memory or I/O, latch the address onto the address bus and set the direction of data transfer on data bus

- During the second clocking period (T<sub>2</sub>):

- o The 8086/8088 issues the  $\overline{RD}$  or  $\overline{WR}$  signal for read or write the data

- $_{\odot}$  The 8086/8088 issues  $\overline{DEN}$  enables the memory or I/O device to receive the data for writes and the 8086/8088 to receive the data for reads

# Timing In General

- During the third clocking period (T<sub>3</sub>):

- This cycle is provided to allow memory to access data.

- READY is sampled at the end of T<sub>2</sub>

- If low, T<sub>3</sub> becomes a wait state

- Otherwise, the data bus is sampled at the end of T<sub>3</sub>

- During the fourth clocking period (T<sub>4</sub>):

- All bus signals are deactivated, in preparation for next bus cycle

- Data is sampled for reading

- Data writes occur for writing

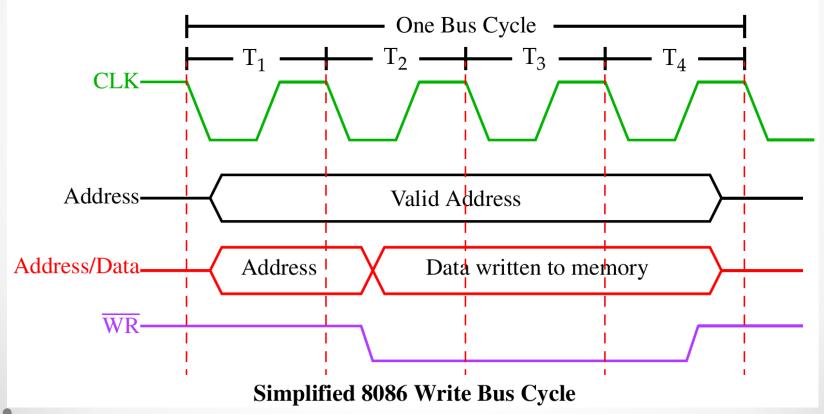

# Bus Timing

#### Writing

- Dump address on address bus.

- Dump data on data bus.

- Issue a write  $(\overline{WR})$  and set M/ $\overline{IO}$  to 1.

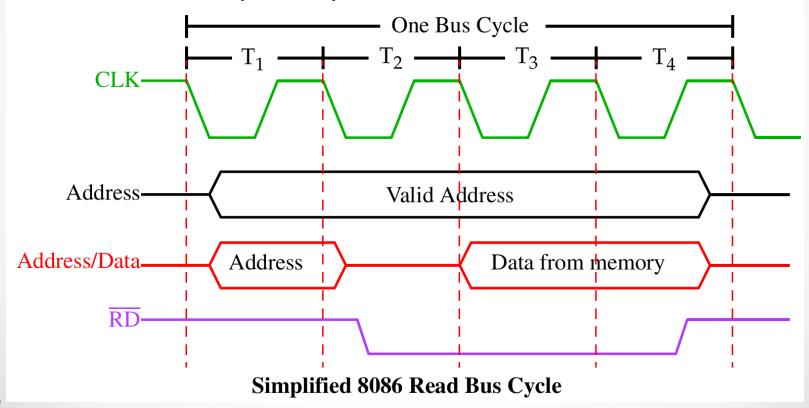

# Bus Timing

#### Reading

- Dump address on address bus.

- Issue a read ( $\overline{RD}$ ) and set M/ $\overline{IO}$  to 1.

- Wait for memory access cycle.

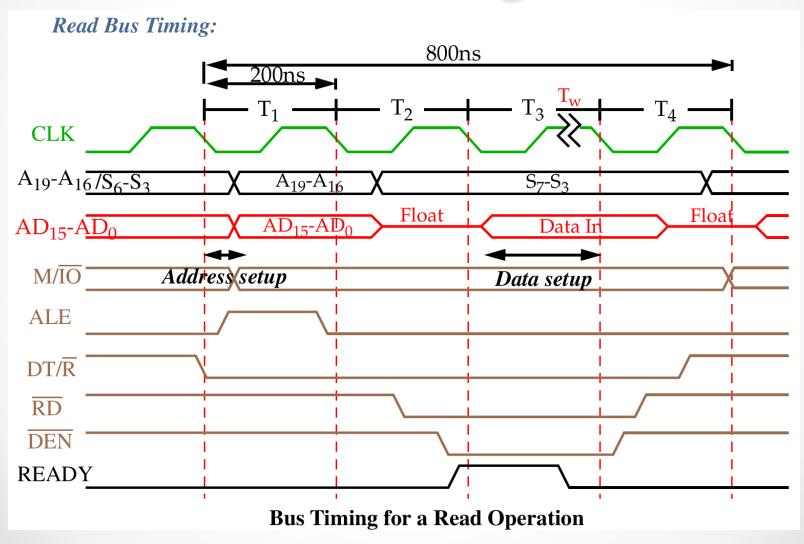

# Read Bus Timing

# Read Bus Timing

### During T<sub>1</sub>:

- The address is placed on the Address/Data bus.

- Control signals M/IO, ALE and DT/R specify memory or I/O, latch the address onto the address bus and set the direction of data transfer on data bus.

### During T<sub>2</sub>:

- 8086 issues the  $\overline{RD}$  or  $\overline{WR}$  signal,  $\overline{DEN}$ , and, for a write, the data.

- DEN enables the memory or I/O device to receive the data for writes and the 8086 to receive the data for reads.

### During T<sub>3</sub>:

- This cycle is provided to allow memory to access data.

- $\blacksquare$  READY is sampled at the end of  $T_2$ .

If low,  $T_3$  becomes a wait state.

Otherwise, the data bus is sampled at the end of  $T_3$ .

### During $T_4$ :

- All bus signals are deactivated, in preparation for next bus cycle.

- Data is sampled for reads, writes occur for writes.

# Bus Timing

- Each BUS CYCLE on the 8086 equals four system clocking periods (T states)

- The clock rate is 5MHz, therefore one Bus Cycle is 800ns and the transfer rate is 1.25MHz

- Memory specifications (memory access time) must match constraints of system timing

- For example, bus timing for a read operation shows almost 600ns are needed to read data

- However, memory must access faster due to setup times, e.g. Address setup and data setup

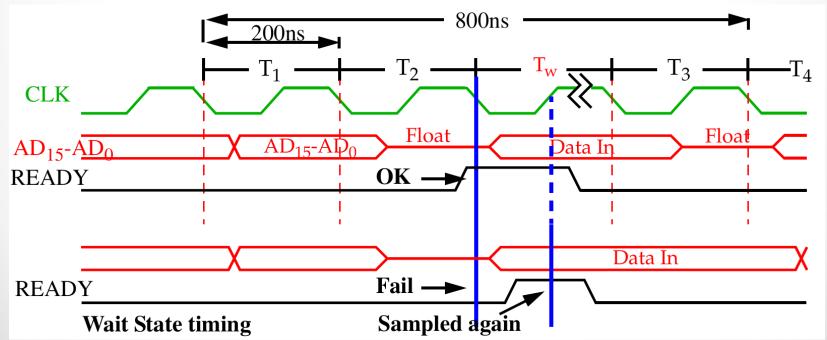

# Bus Timing

- READY: An input to the 8086 that causes wait states for slower memory and I/O components

- A wait state (T<sub>W</sub>) is an extra clock period inserted between T<sub>2</sub> and T<sub>3</sub> to lengthen the bus cycle

# Minimum Mode versus Maximum Mode

- Minimum mode:

- o It is the least expensive way to operate the 8086/8088.

- It costs less because all the control signals are generated inside the microprocessor.

- o It allows the 8085A peripherals to be used.

- Maximum mode:

- It is dropped from the Intel family beginning from 80286.

- All the control signals must be externally generated.

- An external bus controller is used.

- It is used only when the system contains external coprocessor.

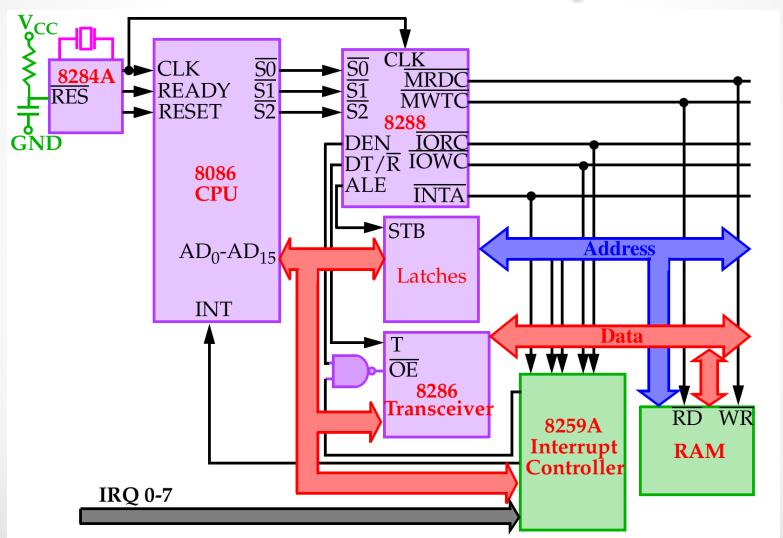

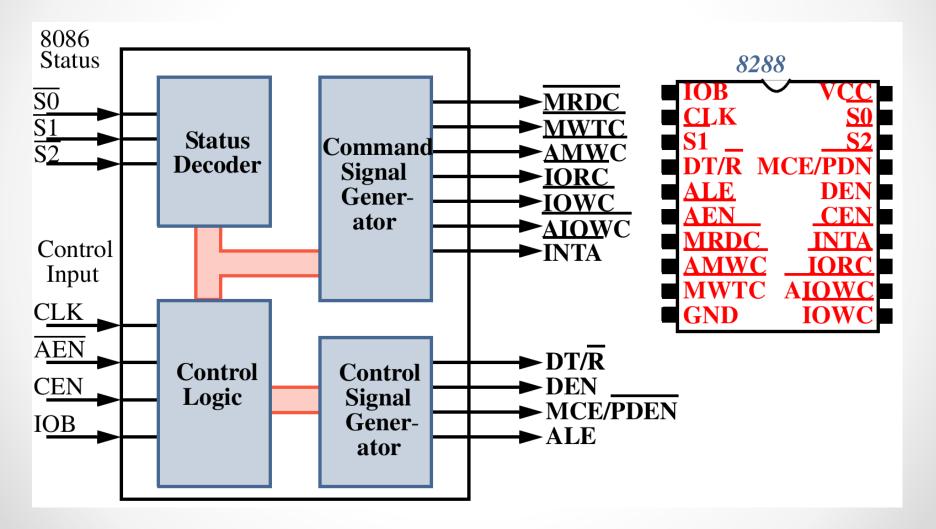

### 8288 Bus Controller

# MAX Mode 8086 System