## Digital IC Design and Architecture

# Sequential Circuits

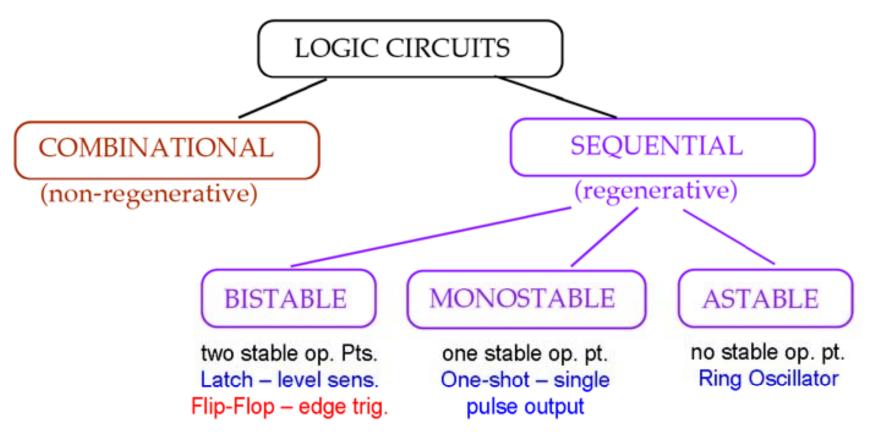

## **Classes of Logic Circuits**

Combinational Circuits: Current Output(s) depend ONLY on CurrentInputs.

Sequential Circuits: Current Output(s) depend on Current Inputs and PAST Output(s).

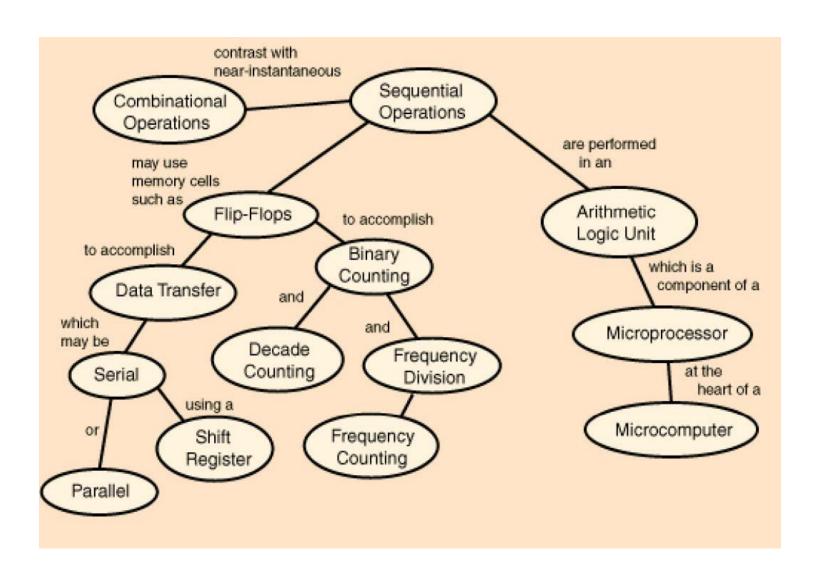

## **Functions Using Sequential Operations**

## Sequential Circuit Construct

V<sub>1</sub> V<sub>2</sub> V<sub>3</sub> COMBINATIONAL LOGIC CIRCUIT

- -> Sequential Circuits: Current Output(s) depend on Current Inputs and PAST inputs (via the feedback of some past State(s) and Output(s) to inputs).

- -> Memory is used to Store Past Values of State(s) and Output(s).

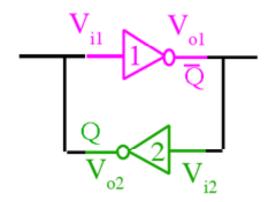

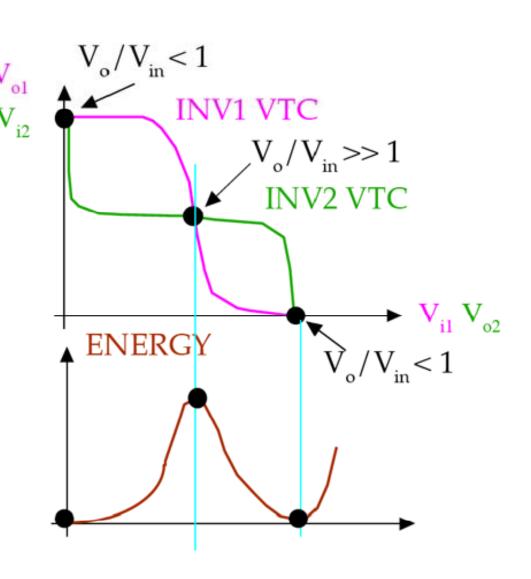

## Bistable Sequential Circuits

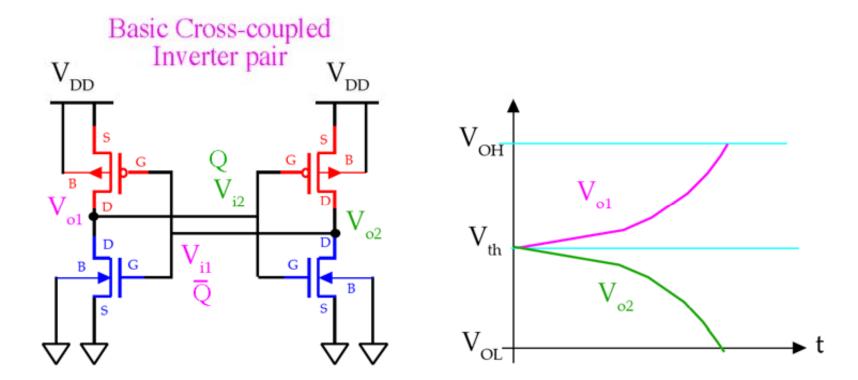

Basic Cross-coupled Inverter pair

BISTABLE BEHAVIOR

6

## Bistable Sequential Circuits - cont.

STATIC: V<sub>DD</sub> is required to maintain stable state.

Basic Bistable Cross-coupled Inverter Pair has no means to apply input(s) to change the circuit's State.

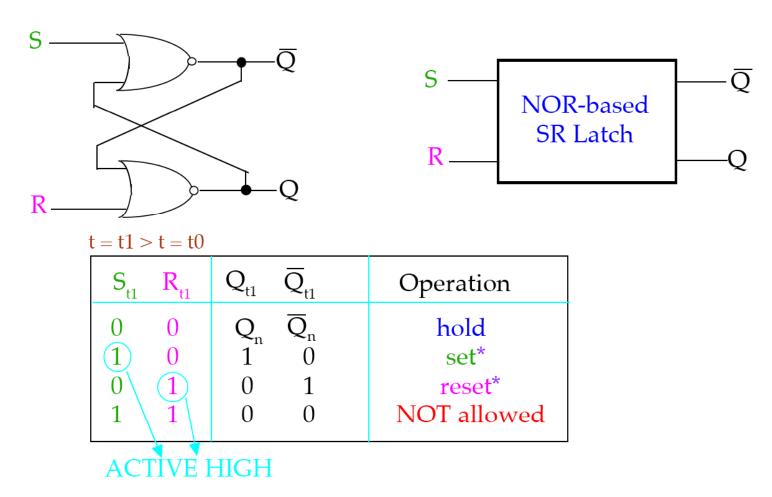

## **Unclocked Latch Circuits**

<sup>\*</sup>Data is written by over powering the feedback loop using S, R inputs.

STATE OF LATCH can be EXTERNALLY SWITCHED between the

## 2 STABLE STATES

SET STATE:

$$S_{t1} = 1, R_{t1} = 0 \Rightarrow Q_{t1} = 1, \overline{Q}_{t1} = 0$$

**RESET STATE:**

$$S_{t1}^{t1} = 0$$

,  $R_{t1}^{t1} = 1 => Q_{t1}^{t1} = 0$ ,  $\overline{Q}_{t1}^{t1} = 1$

HOLD:

$$S_{t1}^{t1} = 0, R_{t1}^{t1} = 0 \Rightarrow Q_{t1}^{t1} = Q_{t0}, \overline{Q}_{t1}^{t1} = \overline{Q}_{t0}$$

$$t-t1 > t-t0$$

(two cross-coupled Inverters)

(M2, MP2 and M3, MP3)

NOT ALLOWED:

$$S = 1$$

,  $R = 1$   $\rightarrow$  state  $Q_{n+1}$ ,  $Q_{n+1}$  is indeterminate

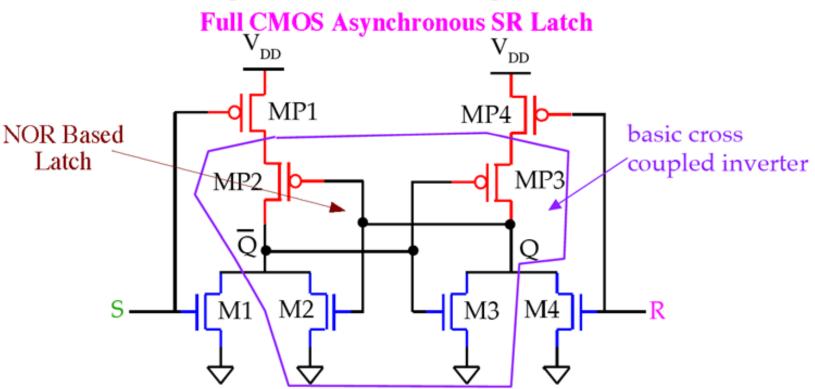

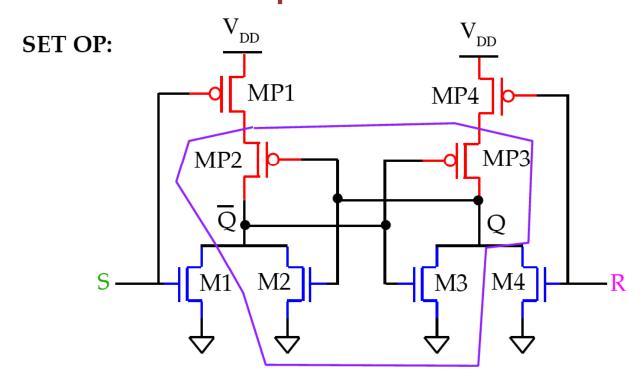

# Unclocked CMOS NOR Based SR Latch Operation

Let at

$$t = t0$$

:  $Q_{t0} = 0$ ,  $\overline{Q}_{t0} = 1$

At

$$t = t1 > t0$$

1.

$$S_{t1} = V_{DD} \Rightarrow M1 \text{ ON, MP1 OFF} \Rightarrow \overline{Q}_{t1} = 0$$

$$2.R_{t1} = 0$$

and  $\overline{Q}_{t1} = 0 => M4$  OFF, M3 OFF, MP3 ON, MP4 ON  $=> Q_{t1} = V_{DD}$

3.

$$Q_{t1} = V_{DD} \implies M2 \text{ ON, } MP2 \text{ OFF} \Longrightarrow \overline{Q}_{t1} = 0$$

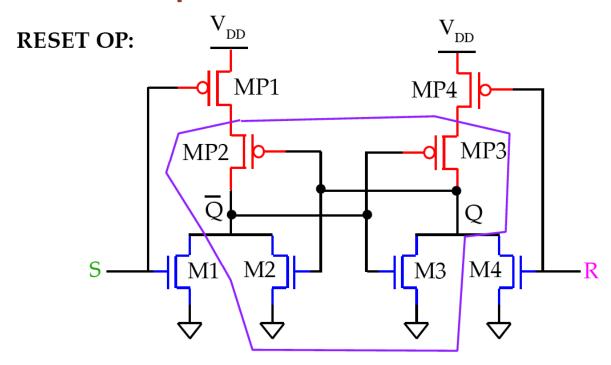

# Unclocked CMOS NOR Based SR Latch Operation - cont.

Let at

$$t = t0$$

:  $Q_{t0} = 1$ ,  $\overline{Q}_{t0} = 0$

At

$$t = t1 > t0$$

1.

$$R_{t1} = 1 \implies M4 \text{ ON, MP4 OFF} \implies Q_{t1} = 0$$

2.

$$S_{t1} = 0$$

and  $Q_{t1} = 0 \Rightarrow M1$  OFF, M2 OFF, MP1 ON, MP2 ON  $\Rightarrow \overline{Q}_{t1} = V_{DD}$

3.

$$\overline{Q}_{t1} = V_{DD} \implies M3 \text{ ON, MP3 OFF} \implies Q_{t1} = 0$$

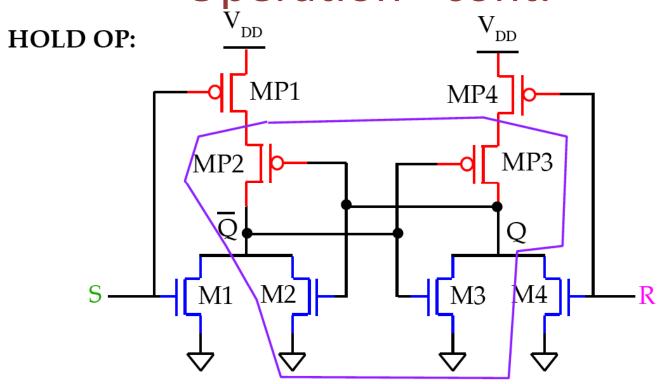

# Unclocked CMOS NOR Based SR Latch Operation - cont.

At t = t1 > t0

1.  $S_{t1} = 0 \implies M1 \text{ OFF, MP1 ON}; R_{t1} = 0 \implies M4 \text{ OFF, MP4 ON}$

$$2a.\ Q_{t1}=Q_{t0}=V_{DD'}\qquad \overline{Q}_{t1}=\overline{Q}_{t0}=0 \Longrightarrow \textbf{M2 ON, MP2 OFF, M3 OFF, MP3 ON}$$

or

$$2b.\ Q_{t1}=Q_{t0}=0,\qquad \overline{Q}_{t1}=\overline{Q}_{t0}=V_{DD}=> \text{M2 OFF, MP2 ON, M3 ON, MP3 OFF}$$

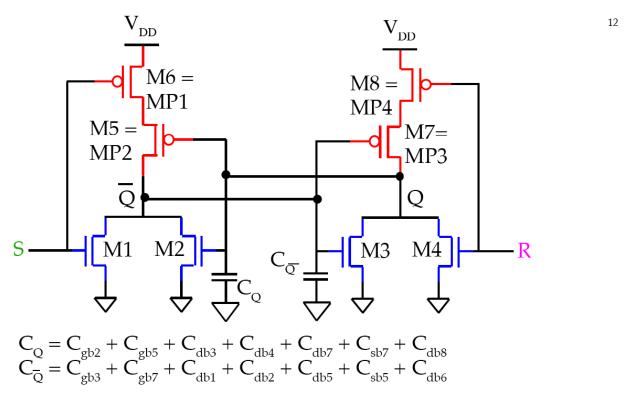

# Unclocked CMOS NOR Based SR Latch Operation - cont.

Estimate time to simultaneously switch  $Q \& \overline{Q}$ : solution of two coupled differential equations.

Conservative Estimate: Assume  $Q \& \overline{Q}$  switch in sequence

$$\tau_{\text{rise,Q}}(\text{SR-latch}) = \tau_{\text{rise,Q}}(\text{NOR}\,2) + \tau_{\text{fall,}\overline{Q}}(\text{NOR}\,2)$$

at  $t = 0$ : S -> 1, R -> 0

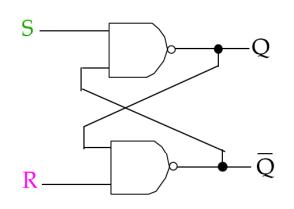

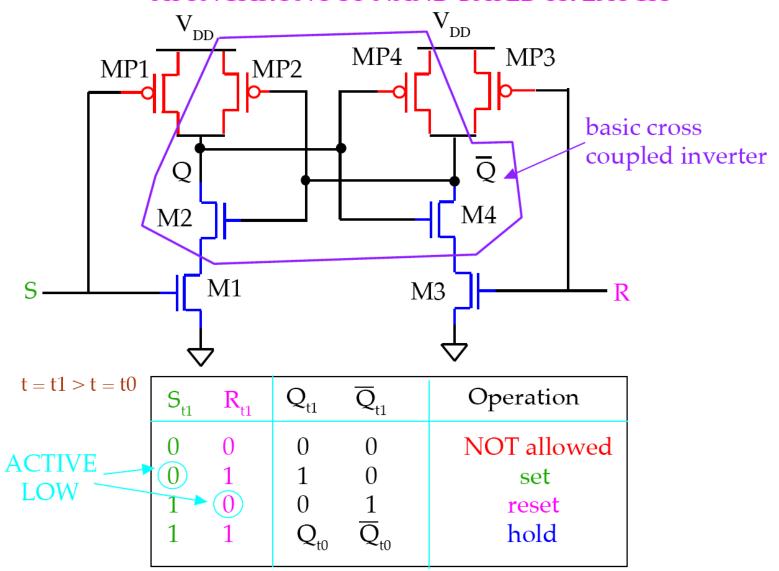

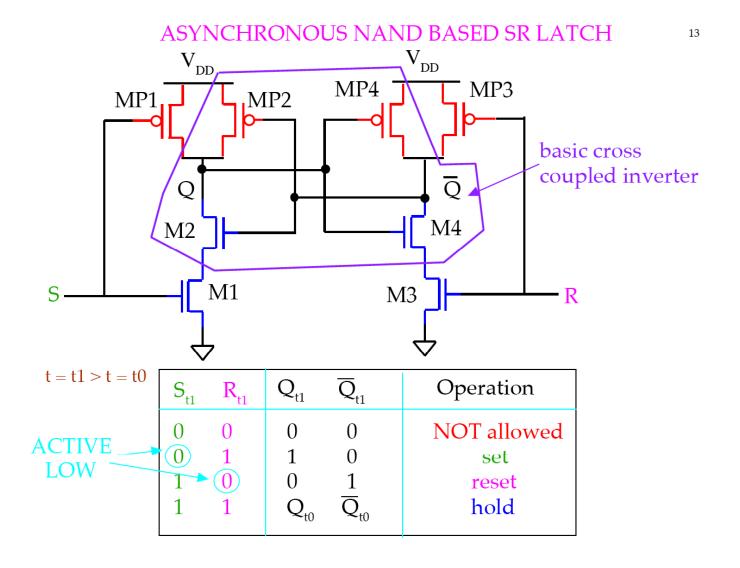

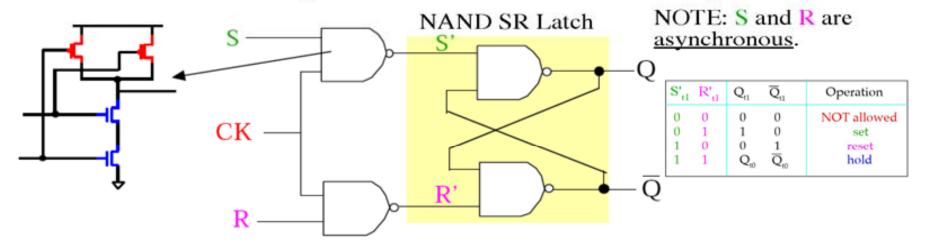

## Unclocked CMOS NAND Based SR Latch Circuit - cont

t=t1>t=t0

| $S_{t1}$ $R_{t1}$                                                                   | $Q_{t1}$ $\overline{Q}_{t1}$                                            | Operation                           |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------|

| $egin{array}{cccc} 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \\ \end{array}$ | $\begin{array}{ccc} 0 & 0 \\ 1 & 0 \\ 0 & \frac{1}{Q}_{t0} \end{array}$ | NOT allowed<br>set<br>reset<br>hold |

**SR-** Latches

- + Simplest form of latch

- Asynchronous

- Not Allowed Input Sequence

#### ASYNCHRONOUS NAND BASED SR LATCH

## Unclocked CMOS NAND Based SR Latch Circuit

#### Clocked CMOS Latch Circuits

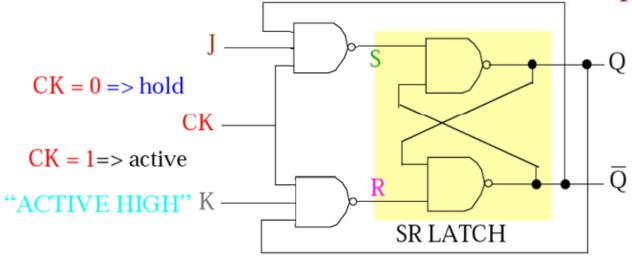

CLOCKED SR LATCH: Synchronization is introduced through clock CK.

When CK = 0, S' = R' = 1 independent of the values of S and  $R \Rightarrow HOLD$

$\begin{array}{lll} \text{HOLD STATE:} & \text{CK = 0, } S = x, & \text{R = x => } Q_{n+1} = Q_n, \overline{Q}_{n+1} = \overline{Q}_n \\ \text{SET STATE:} & \text{CK = 1, } S = 1, & \text{R = 0 => } Q_{n+1} = 1, & \overline{Q}_{n+1} = 0 \\ \text{RESET STATE:} & \text{CK = 1, } S = 0, & \text{R = 1 => } Q_{n+1} = 0, & \overline{Q}_{n+1} = 1 \end{array}$

NOT ALLOWED: CK = 1, S = 1,  $R = 1 \Rightarrow S' = 0$ , R' = 0

"ACTIVE HIGH"

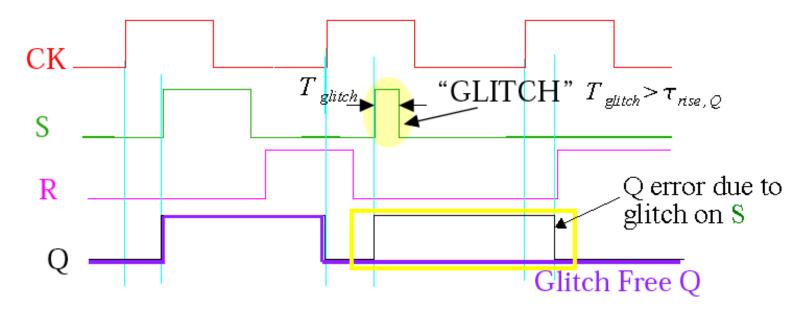

## Clocked CMOS Latch Circuits - cont.

HOLD STATE: CK = 0, S = x,  $R = x = Q_{n+1} = Q_n$ ,  $\overline{Q}_{n+1} = \overline{Q}_n$

SET STATE: CK = 1, S = 1,  $R = 0 = Q_{n+1} = 1$ ,  $\overline{Q}_{n+1} = 0$

**RESET STATE:** CK = 1, S = 0, R = 1 = 0,  $\overline{Q}_{n+1} = 0$ ,  $\overline{Q}_{n+1} = 1$

NOT ALLOWED: CK = 1, S = 1, R = 1

WHEN "GLITCH" ON S (OR R) OCCURS DURING CK = 1, Q IS SET (OR RESET)

LEVEL SENSITIVE: WHEN CK = 1, ANY CHANGES IN S, R WILL EFFECT Q.

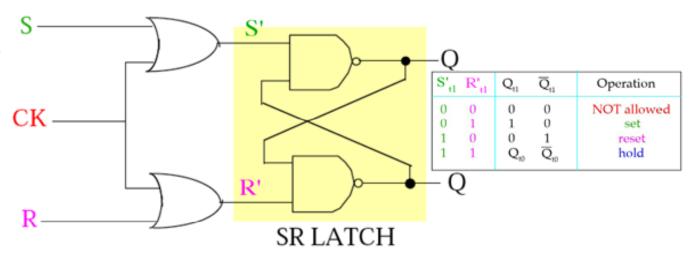

### Clocked CMOS Latch Circuits - cont.

Another Gate Level schematic of a Clocked NAND Based SR Latch

When CK = 1, S' = R' = 1 independent of the values of S and  $R \Rightarrow HOLD$

"ACTIVE LOW"

| CK | S | R | $Q_{n+1}$ $\overline{Q}_{n+1}$                                                   | Operation   |

|----|---|---|----------------------------------------------------------------------------------|-------------|

| 0  | 0 | 0 | $\begin{array}{ccc} 0 & 0 \\ 1 & 0 \\ 0 & 1 \\ Q_n & \overline{Q}_n \end{array}$ | NOT allowed |

| 0  | 0 | 1 |                                                                                  | set         |

| 0  | 1 | 0 |                                                                                  | reset       |

| 1  | x | x |                                                                                  | hold        |

S' = R' = 0

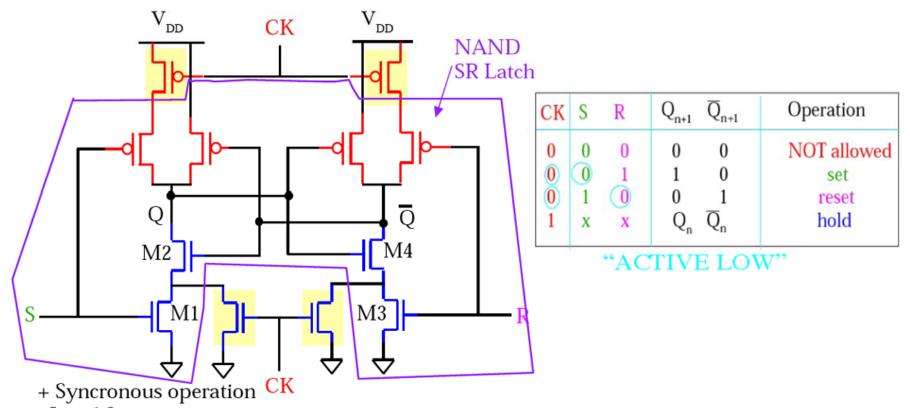

### Clocked CMOS Latch Circuits - cont.

#### CMOS Clocked NAND Based SR Latch or Flip-Flop

- Level Sensitive

- Not Allowed Input Sequence

## CMOS Clocked Latch Circuits - cont.

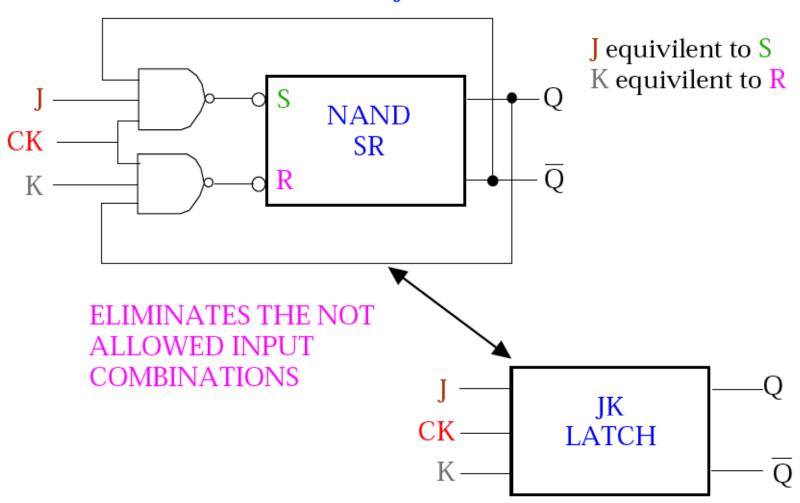

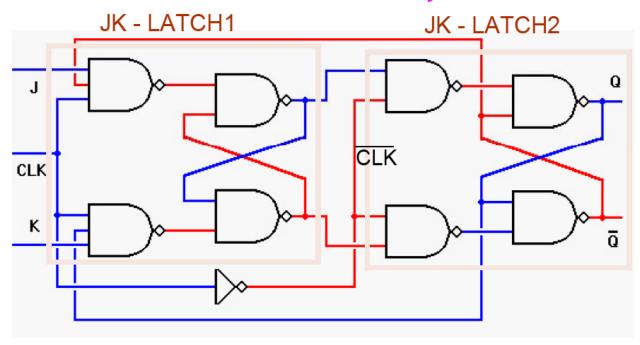

#### NAND BASED CLOCKED JK FLIP-FLOP

## Clocked NAND Based JK Latch Operation

CK = 1

|   | J | K | $Q_n$ | $Q_n$ | S | R | $Q_{n+1}$ | $\overline{Q}_{n+1}$ | Operation        |

|---|---|---|-------|-------|---|---|-----------|----------------------|------------------|

|   | 0 | 0 | 0     | 1     | 1 | 1 | 0         | 1                    | hold             |

|   | 0 | 0 | 1     | 0     | 1 | 1 | 1         | 0                    | hold             |

| İ | 0 | 1 | 0     | 1     | 1 | 1 | 0         | 1                    | reset (hold)     |

|   | 0 | 1 | 1     | 0     | 1 | 0 | 0         | 1                    | reset            |

|   | 1 | 0 | 0     | 1     | 0 | 1 | 1         | 0                    | set              |

|   | 1 | 0 | 1     | 0     | 1 | 1 | 1         | 0                    | set (hold)       |

|   | 1 | 1 | 0     | 1     | 0 | 1 | 1         | 0                    | toggle           |

|   | 1 | 1 | 1     | 0     | 1 | 0 | 0         | 1                    | toggle<br>toggle |

The <u>not-allowed</u> S, R values S = R = 0 do <u>not occur</u> for any values of J, K, CK.

osc  $\longrightarrow$  but the state  $Q_{n+1}$ ,  $Q_{n+1}$  is  $\underbrace{determinate}$

## Clocked NAND Based JK Latch Operation

|        | J | K | $Q_n$ | $\overline{\boldsymbol{Q}}_n$ | S | R | $Q_{n+1}$ | $\overline{Q}_{n+1}$ | Operation        |     |

|--------|---|---|-------|-------------------------------|---|---|-----------|----------------------|------------------|-----|

|        | 0 | 0 | 0     | 1                             | 1 | 1 | 0         | 1                    | hold             |     |

|        | 0 | 0 | 1     | 0                             | 1 | 1 | 1         | 0                    | hold             | l.  |

| CV 1   | 0 | 1 | 0     | 1                             | 1 | 1 | 0         | 1                    | reset            |     |

| CK = 1 | 0 | 1 | 1     | 0                             | 1 | 0 | 0         | 1                    | reset            |     |

|        | 1 | 0 | 0     | 1                             | 0 | 1 | 1         | 0                    | set              |     |

|        | 1 | 0 | 1     | 0                             | 1 | 1 | 1         | 0                    | set              | W-  |

|        | 1 | 1 | 0     | 1                             | 0 | 1 | 1         | 0                    | toggle           | 080 |

|        | 1 | 1 | 1     | 0                             | 1 | 0 | 0         | 1                    | toggle<br>toggle | OSC |

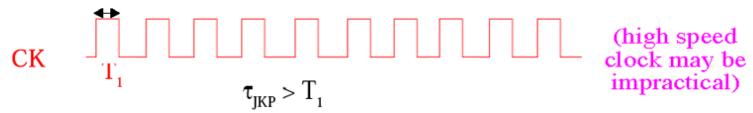

#### TO PREVENT OSICLLATION WHEN J = K = 1:

$\tau_{\text{JKP}} = \text{INPUT-OUTPUT PROP DELAY OF JK LATCH}$ (CK 1 -> 0 BEFORE Q,  $\overline{Q}$  CAN SWITCH 2<sup>nd</sup> TIME)

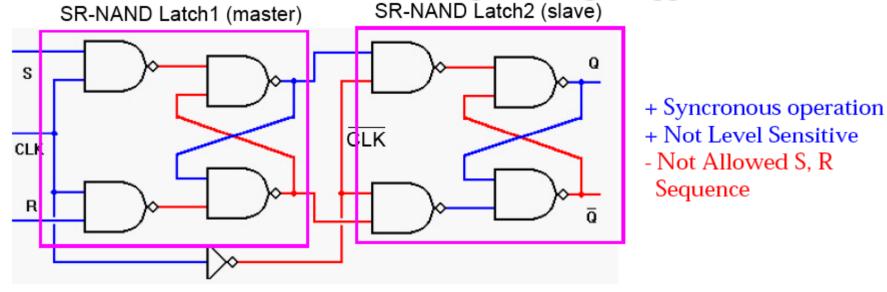

## CLOCKED SR FLIP FLOP: Negative Edge Triggered.

- Start with CLK = 0, the S, R inputs are disconnected from the input Latch1.

- Changes in S, R cannot affect the state of Q, Q.

When CLK = 1, S, R are able to control the state of Latch1.

- Inverted CLK applied to Latch2 prevents the state of Latch1 from effecting Q, Q.

- Any changes to R, S are tracked by Latch1 while CLK = 1, but not reflected at Q,  $\overline{Q}$ .

When CLK = 0, S, R are again isolated from Latch1.

- Inverted CLK allows the current state of Latch1 to reach Latch2.

- Q, Q can only change state when the CLK signal falls from 1 to 0.

- This is the falling (negative) edge of the CLK signal.

### **CLOCKED EDGE TRIGGERED JK FLIP-FLOP**

- + Synchronous Operation

- + No Not-Allowed Inputs

- + Not Level Sensitive

- + No Q,  $\overline{Q}$  Oscillation when J = K = 1

Since the behavior of the JK flip-flop is completely predictable under all conditions, it is the preferred type of flip-flop for most logic circuit designs.

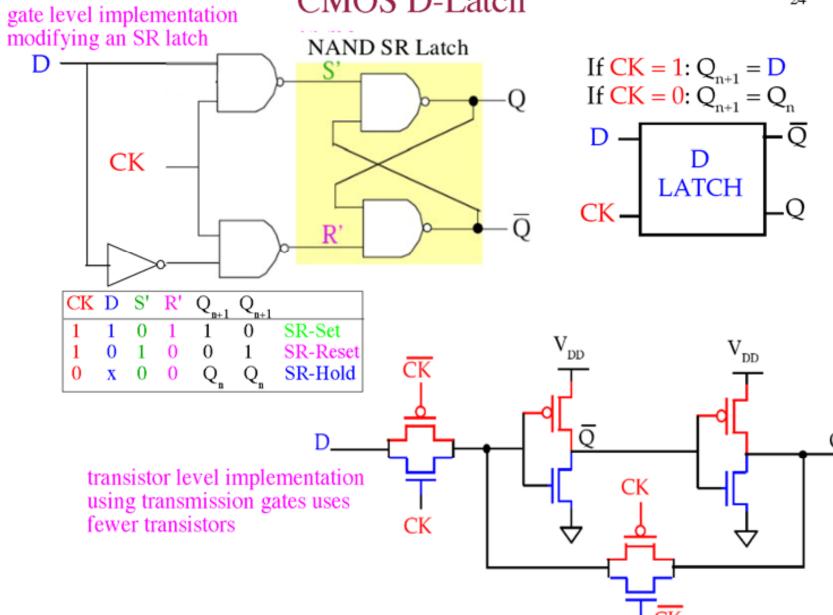

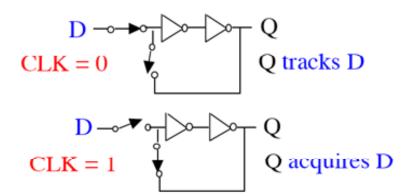

## **CMOS D-Latch**

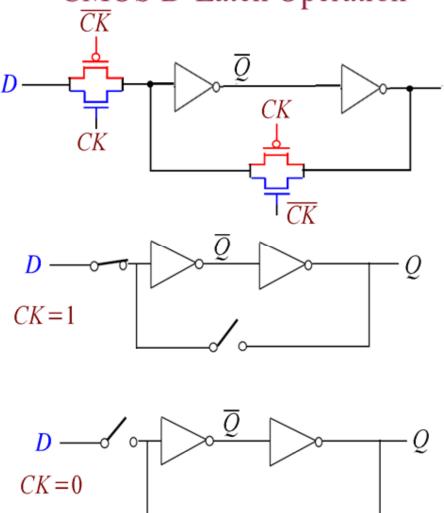

## **CMOS D-Latch Operation**

- + Much simpler then JK Latch.

- + Does not require Edge Triggering for Safe Operation.

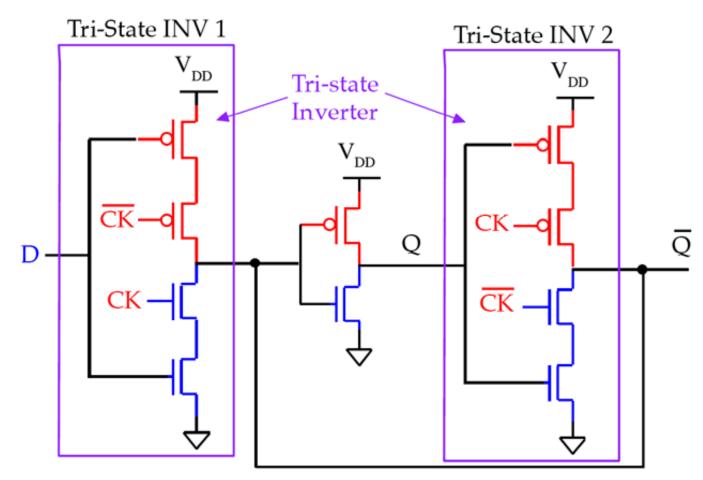

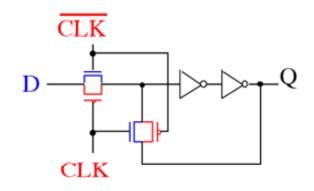

## CMOS D-Latch - cont.

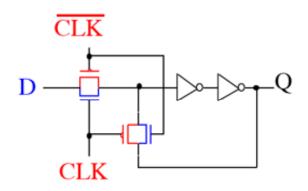

#### alternative implementation using clocked tri-state inverters

CK = 1: Tri-state INV 1 is active, Tri-state INV 2 is Hi-Z and  $Q_n = D_n$  CK = 0: Tri-state INV 1 is Hi-Z, Tri-state INV 2 is active and  $\overline{Q}_n$  are held

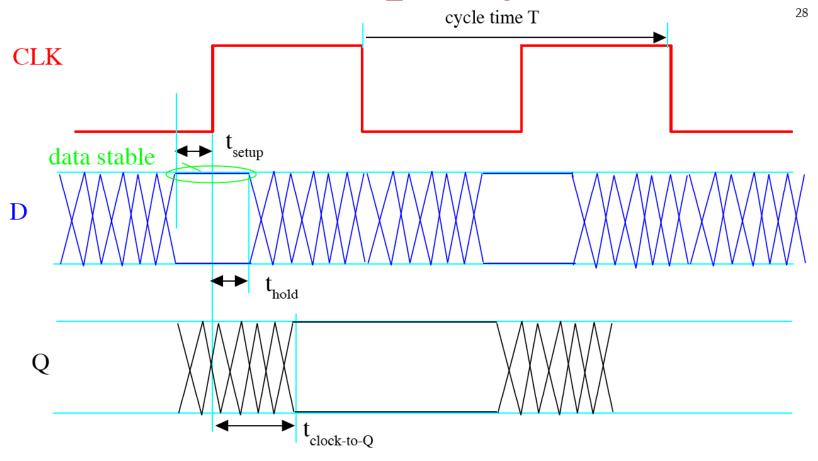

## **D-Latch Timing Requirements**

t<sub>setup</sub> - time before the POS(neg)-CLK edge the D-input has to be stable.

$\boldsymbol{t}_{hold}$  - time after POS(neg)-CLK edge that the D-input has to remain stable.

$t_{\mbox{\tiny clock-to-Q}}$  - Delay from the POS(neg)-CLK edge to new stable value of Q output.

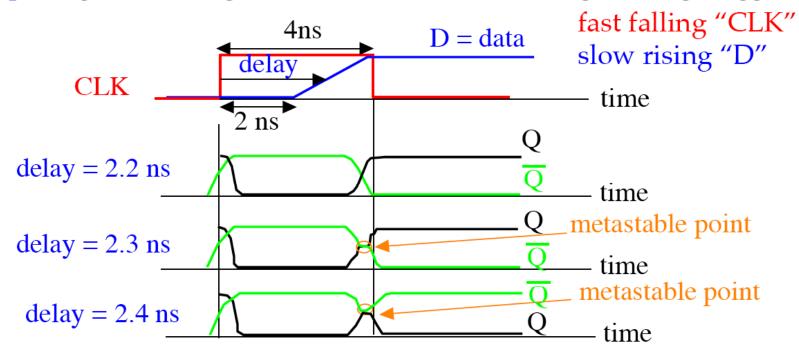

#### METASTABILITY AND SYNCRONIZATION FAILURES

If data and clock do not satisfy the setup & hold time constaints of a register, then syncronization failure may occur. This due to inherent analog nature of storage elements.

METASTABLE STATE - indeterminate state between "1" & "0", i.e. latch is perfectly balanced between making decision for "1" or "0". In practice noise will eventually arbitrarily push latch output to "0" or "1".

Example: register entering metastable state (shown for negative edge trigger case)

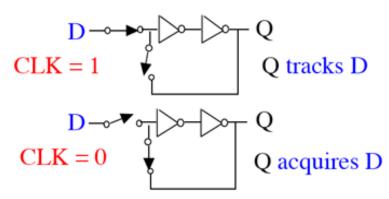

#### Positive D - Latch

#### Negative D - Latch

D Flip-Flop = Positive D-Latch + Negative D-Latch

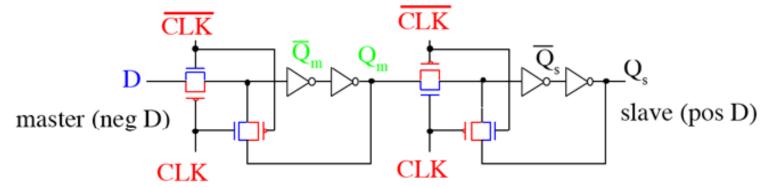

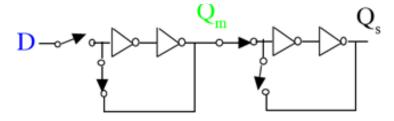

## CMOS D Flip-Flop – Positive Edge Triggered

#### FOR CLK = 1

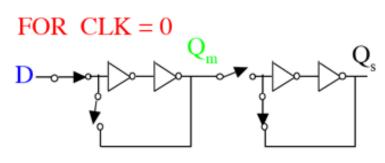

- 1. CLK = 0: master  $Q_m$  tracks input D; slave  $Q_s$  = previous  $D_{n-1}$  sample ( $Q_s$  is transparent to variations in D).

- 2. CLK = 0 -> 1: master stores  $Q_m = D_n$  (new D sample).

- 3. CLK = 1: master passes  $Q_m = D_n$  to slave output  $Q_s(Q_m$  and  $Q_s$  are transparent to variations in D).

- 4. CLK = 1 -> 0: slave locks in new  $D_n$ .

- 5. CLK = 0: master  $Q_m$  begins tracking D.  $(Q_s$  is transparent to variations in D)

- 6. CLK =  $0 \rightarrow 1$ : master stores  $Q_m = D_{n+1}$ .

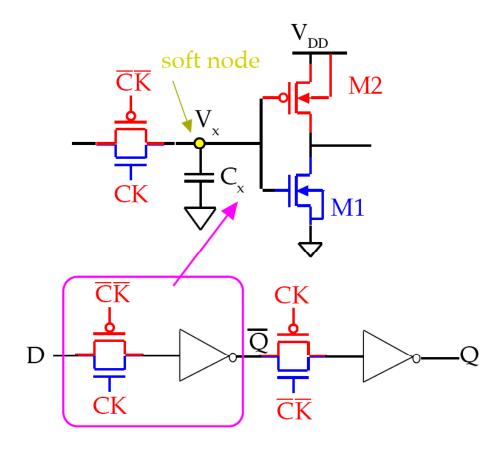

# CMOS Dynamic D Flip-Flop

- 1. NO FEEDBACK REGENERATIVE FEEDBACK LOOP

- 2. STATES STORED ON SOFT NODES