# PART II

---

## The PIC Microcontrollers

Programmable Interrupt Controller

Peripheral Interface Controller

EEC 343

# Lecture\_1

---

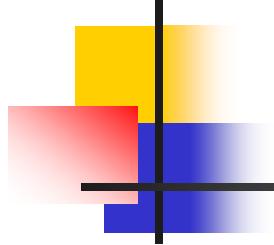

# Microprocessors vs Microcontroller

Fig. 0-1 Microcontroller versus Microprocessor

# Microprocessors vs Microcontrollers

## Feature

### Microcontroller ( $\mu\text{C}$ )

### Microprocessor ( $\mu\text{P}$ )

#### Purpose

Designed for specific embedded system applications

Designed for general-purpose computing applications

#### Architecture

Single-chip computer system with on-board memory, peripherals, and I/O interfaces

CPU with minimal on-board memory, peripherals and I/O interfaces

#### Integration level

Highly integrated

Less integrated

#### System architecture

Single-chip system

CPU + support chips

#### Processing power

Lower power

Higher power

# Microprocessors vs Microcontroller

| Feature                | Microcontroller ( $\mu C$ )                    | Microprocessor ( $\mu P$ )                       |

|------------------------|------------------------------------------------|--------------------------------------------------|

| <b>Instruction set</b> | Fixed instruction set                          | More flexible                                    |

| <b>Clock speed</b>     | Lower clock speed, typically less than 100 MHz | Higher clock speed, typically greater than 1 GHz |

# Types of Microchip PIC µCs

| Family                                                              | ROM [Kbytes] | RAM [bytes] | Pins     | Clock Freq. [MHz] | A/D Inputs | Resolution of A/D Converter | Comparators | 8/16-bit Timers         | Serial Comm.                           | PWM Outputs | Others    |

|---------------------------------------------------------------------|--------------|-------------|----------|-------------------|------------|-----------------------------|-------------|-------------------------|----------------------------------------|-------------|-----------|

| <b>Base-Line 8-bit architecture, 12-bit Instruction Word Length</b> |              |             |          |                   |            |                             |             |                         |                                        |             |           |

| PIC10FXXX                                                           | 0.375 - 0.75 | 16 - 24     | 6 - 8    | 4 - 8             | 0 - 2      | 8                           | 0 - 1       | 1 x 8                   | -                                      | -           | -         |

| PIC12FXXX                                                           | 0.75 - 1.5   | 25 - 38     | 8        | 4 - 8             | 0 - 3      | 8                           | 0 - 1       | 1 x 8                   | -                                      | -           | EEPROM    |

| PIC16FXXX                                                           | 0.75 - 3     | 25 - 134    | 14 - 44  | 20                | 0 - 3      | 8                           | 0 - 2       | 1 x 8                   | -                                      | -           | EEPROM    |

| PIC16HVXXX                                                          | 1.5          | 25          | 18 - 20  | 20                | -          | -                           | -           | 1 x 8                   | -                                      | -           | Vdd = 15V |

| <b>Mid-Range 8-bit architecture, 14-bit Instruction Word Length</b> |              |             |          |                   |            |                             |             |                         |                                        |             |           |

| PIC12FXXX                                                           | 1.75 - 3.5   | 64 - 128    | 8        | 20                | 0 - 4      | 10                          | 1           | 1 - 2 x 8<br>1 x 16     | -                                      | 0 - 1       | EEPROM    |

| PIC12HVXXX                                                          | 1.75         | 64          | 8        | 20                | 0 - 4      | 10                          | 1           | 1 - 2 x 8<br>1 x 16     | -                                      | 0 - 1       | -         |

| PIC16FXXX                                                           | 1.75 - 14    | 64 - 368    | 14 - 64  | 20                | 0 - 13     | 8 or 10                     | 0 - 2       | 1 - 2 x 8<br>1 x 16     | USART I2C<br>SPI                       | 0 - 3       | -         |

| PIC16HVXXX                                                          | 1.75 - 3.5   | 64 - 128    | 14 - 20  | 20                | 0 - 12     | 10                          | 2           | 2 x 8 1 x 16            | USART I2C<br>SPI                       | -           | -         |

| <b>High-End 8-bit architecture, 16-bit Instruction Word Length</b>  |              |             |          |                   |            |                             |             |                         |                                        |             |           |

| PIC18FXXX                                                           | 4 - 128      | 256 - 3936  | 18 - 80  | 32 - 48           | 4 - 16     | 10 or 12                    | 0 - 3       | 0 - 2 x 8<br>2 - 3 x 16 | USB2.0<br>CAN2.0<br>USART I2C<br>SPI   | 0 - 5       | -         |

| PIC18FXXJXX                                                         | 8 - 128      | 1024 - 3936 | 28 - 100 | 40 - 48           | 10 - 16    | 10                          | 2           | 0 - 2 x 8<br>2 - 3 x 16 | USB2.0<br>USART<br>Ethernet I2C<br>SPI | 2 - 5       | -         |

| PIC18FXXKXX                                                         | 8 - 64       | 768 - 3936  | 28 - 44  | 64                | 10 - 13    | 10                          | 2           | 1 x 8 3 x 16            | USART I2C<br>SPI                       | 2           | -         |

# Where we find PIC microcontrollers

- **Automotive systems:** Engine control units, dashboard displays, and body electronics.

- **Consumer electronics:** Remote controls, smart home devices, digital clocks, and appliances.

- **Industrial control:** Motor control, process automation, and programmable logic controller (PLC) systems.

- **Medical devices:** Patient monitoring equipment and portable diagnostic tools.

- **Power tools:** Used for motor control and battery management in cordless drills and other tools.

- **Vending machines:** Managing payment systems and product dispensing mechanisms.

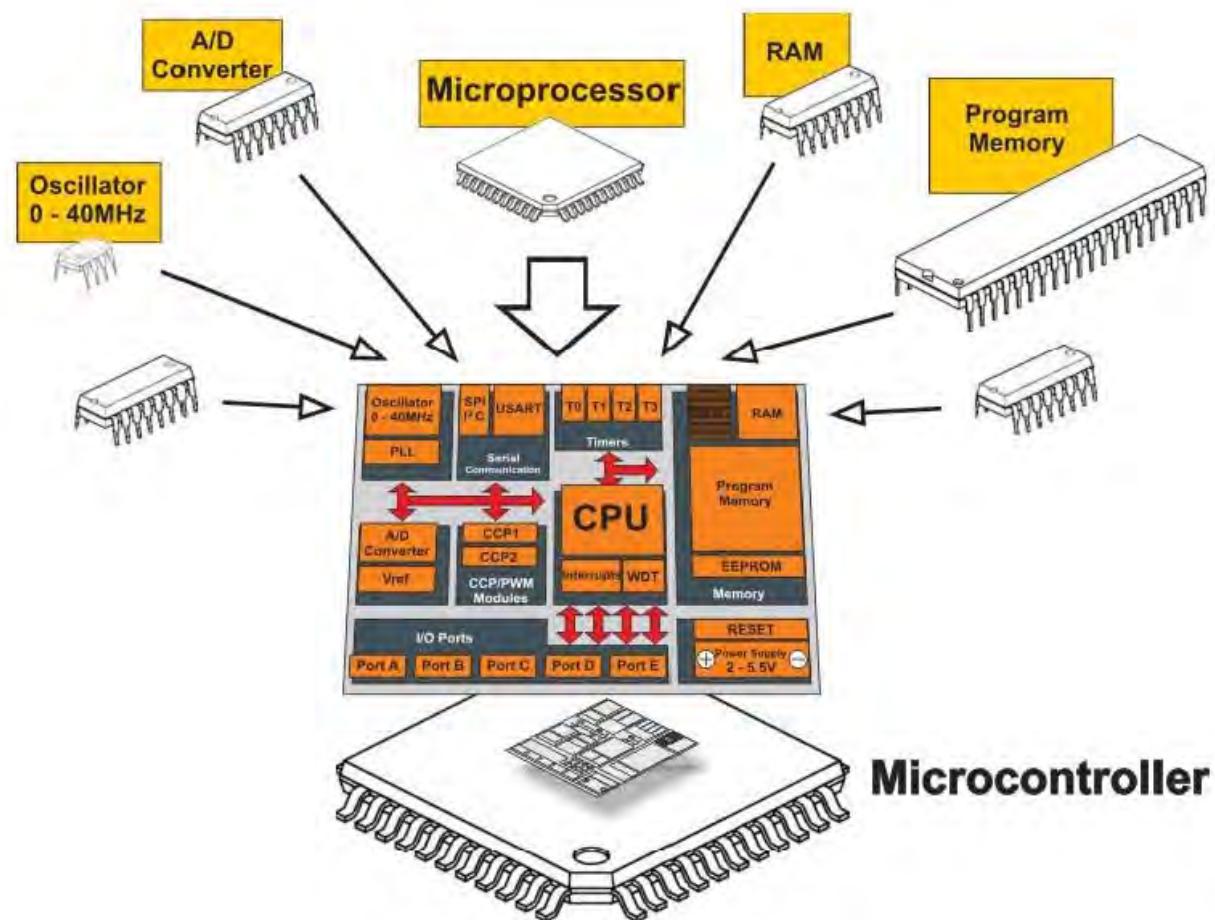

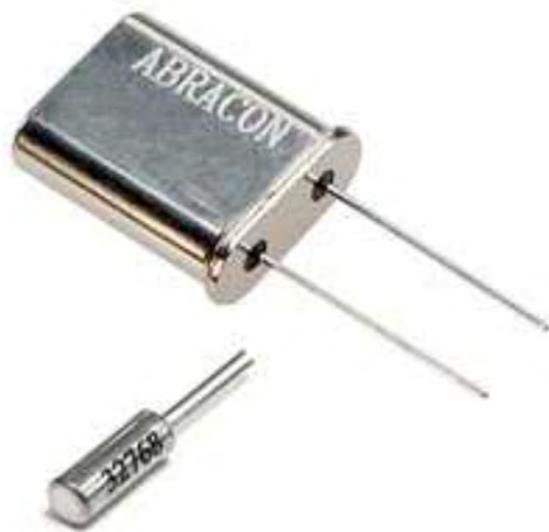

# PICmicro® MCU

## Microcontroller Overview

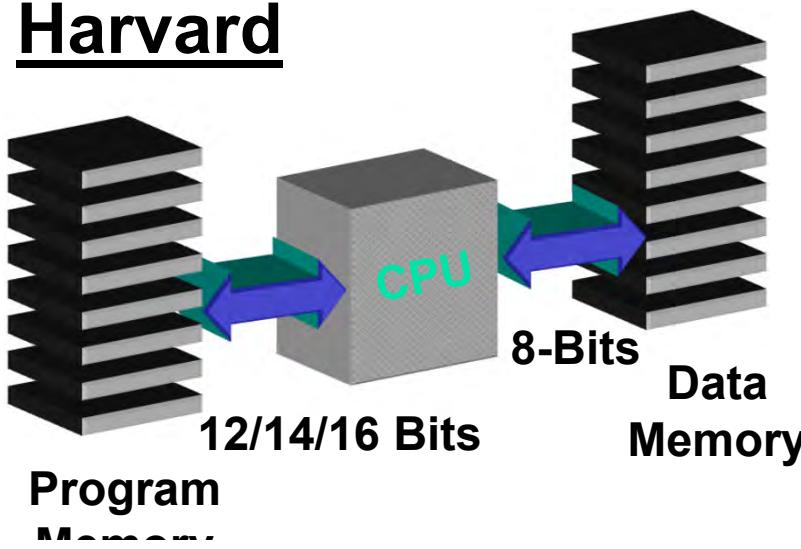

- Microchip uses a Harvard Architecture with separate address & data buses

- Program bus: 12-, 14- & 16-bit wide instructions

- Data bus: 8-bit wide data path

- Package sizes available from Microchip

- 8 pins through 84 pins

Architecture

(x14)

**16F84A**

# PICmicro® MCU Architecture

- RISC Microcontroller Features

- The high performance of the PICmicro® MCU can be attributed to the following:

- Harvard Architecture

- Instruction pipelining

- Register file concept

- Single cycle instructions

- All single word instructions

- Long word instruction

- Reduced instruction set

- Orthogonal instruction set

# PICmicro® MCU Architecture

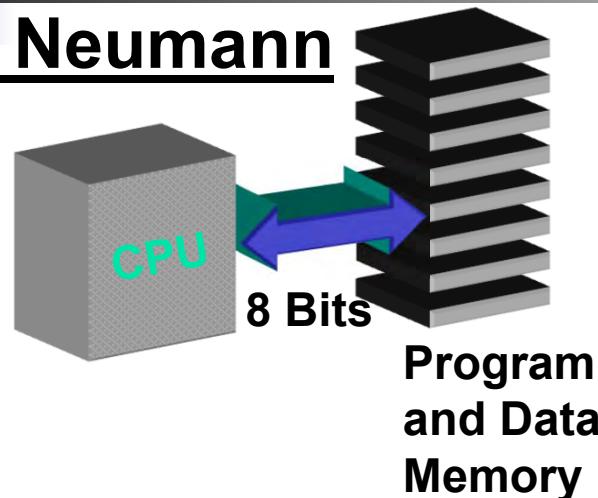

## Harvard Architecture

### Von Neumann

### Harvard

- Fetches instructions and data from one memory

- Limits operating bandwidth

- Two separate memory spaces for instructions and data

- Increases throughput

- Different program and data bus widths are possible

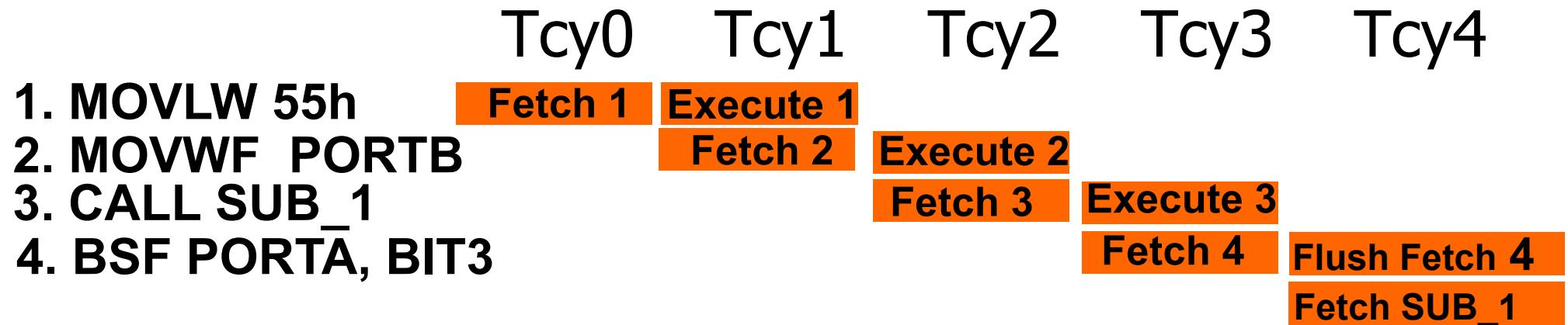

# Pipelining

1. **MOVLW 55h**

2. **MOVWF PORTB**

3. **CALL SUB\_1**

4. **BSF PORTA, BIT3**

# Pipelining

- In most microcontrollers, instructions are fetched and executed **sequentially**

- Allows overlap of fetch and execution

- Makes single cycle execution

- Program branches (e.g. GOTO, CALL or WRITE to PC) takes two cycles

# PICMICRO® MCU Architecture

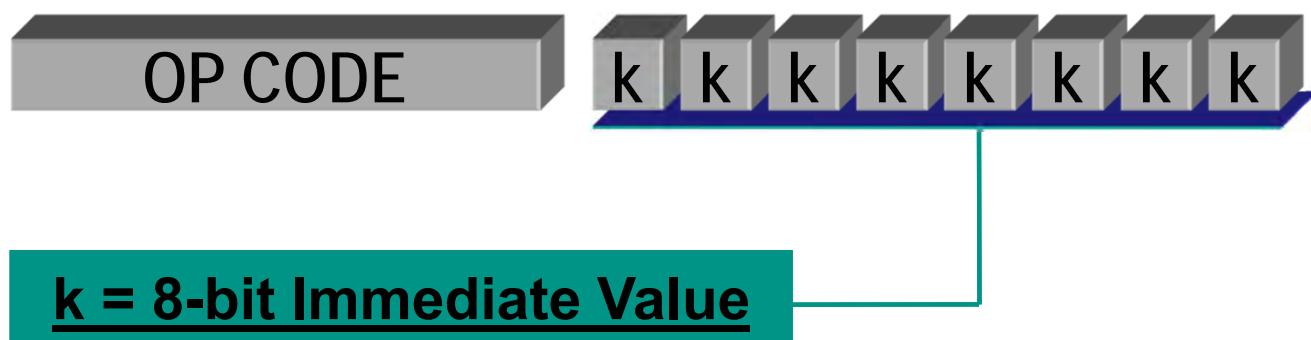

## Long word Instructions

**PICMICRO® MCU**

**movlw #imm<8>**

**1100XX k k k k k k k k**

**MC68HC05**

**ldaa #imm<8>**

**1000 0110**

**k k k k k k k k**

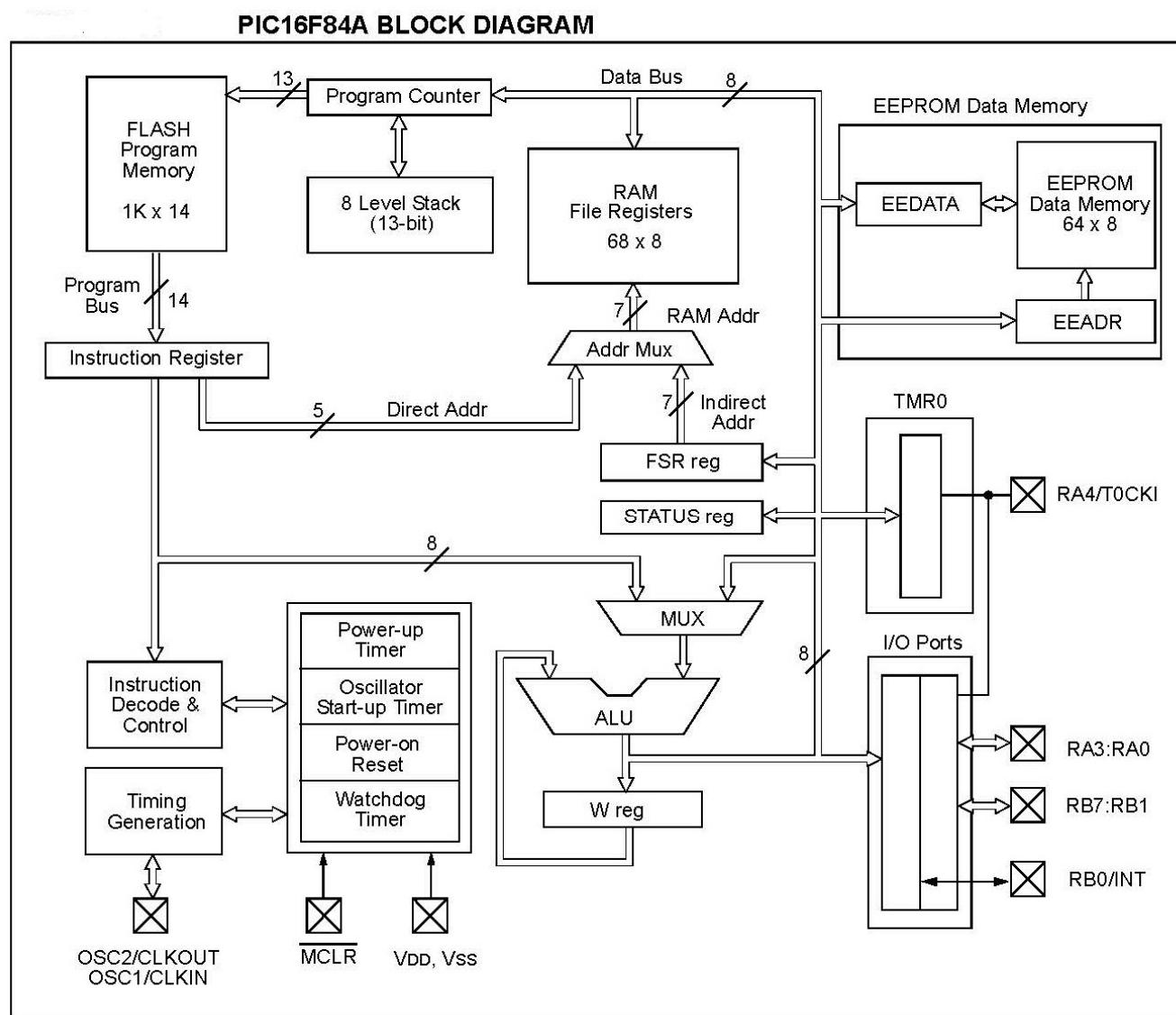

# PICmicro® MCU Architecture

## Block Diagram of PIC16F84A

# Lecture\_2

---

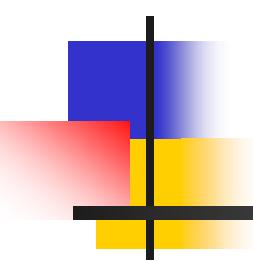

# PICMicro® MCU Architecture Block Diagram

# PICMicro® MCU Architecture

## Flash-Type Microcontrollers

PICMicro® PIC flash microcontroller features

| PIC device number | Total pins | I/O pins | Program ROM words | File RAM bytes | EEPROM bytes | Analogue inputs | Timers 8 bit | Timers 16 bit | Max. clock (MHz) | Internal osc. (MHz) | In-circuit debug | CCP/PWM modules       | Serial comms | Relative cost |

|-------------------|------------|----------|-------------------|----------------|--------------|-----------------|--------------|---------------|------------------|---------------------|------------------|-----------------------|--------------|---------------|

| 12F629            | 8          | 6        | 1k                | 64             | 128          | —               | 1 + 1        | 20            | 4                | ✓                   | —                | —                     | —            | 1.02          |

| 12F675            | 8          | 6        | 1k                | 64             | 128          | 4 x 10-bit      | 1 + 1        | 20            | 4                | ✓                   | —                | —                     | —            | 1.26          |

| 16F627A           | 18         | 16       | 1k                | 224            | 128          | —               | 2 + 1        | 20            | 4                | —                   | —                | —                     | UART         | 1.49          |

| 16F628A           | 18         | 16       | 2k                | 224            | 128          | —               | 2 + 1        | 20            | 4                | —                   | —                | 1                     | UART         | 1.70          |

| 16F630            | 14         | 12       | 1k                | 64             | 128          | —               | 1 + 1        | 20            | 4                | ✓                   | —                | —                     | —            | 1.20          |

| 16F648A           | 18         | 16       | 4k                | 256            | 256          | —               | 2 + 1        | 20            | 4                | —                   | —                | —                     | UART         | 1.83          |

| 16F676            | 14         | 12       | 1k                | 64             | 128          | 8 x 10-bit      | 1 + 1        | 20            | 4                | ✓                   | —                | —                     | UART         | 1.38          |

| 16F72             | 28         | 22       | 2k                | 128            | —            | 4 x 8-bit       | 2 + 1        | 20            | —                | —                   | —                | 1                     | —            | 2.10          |

| 16F73             | 28         | 22       | 4k                | 192            | —            | 5 x 8-bit       | 2 + 1        | 20            | —                | —                   | —                | 2                     | All          | 3.27          |

| 16F74             | 40         | 33       | 4k                | 192            | —            | 8 x 8-bit       | 2 + 1        | 20            | —                | —                   | —                | 2                     | All          | 3.97          |

| 16F76             | 28         | 22       | 8k                | 368            | —            | 5 x 8-bit       | 2 + 1        | 20            | —                | —                   | —                | 2                     | All          | 4.10          |

| 16F77             | 40         | 33       | 8k                | 368            | —            | 8 x 8-bit       | 2 + 1        | 20            | —                | —                   | —                | 2                     | All          | 4.58          |

| 16F818            | 18         | 16       | 1k                | 128            | 128          | 5 x 10-bit      | 2 + 1        | 20            | 8                | ✓                   | 1                | I <sup>2</sup> C, SPI | 1.71         |               |

| 16F819            | 18         | 16       | 2k                | 256            | 256          | 5 x 10-bit      | 2 + 1        | 20            | 8                | ✓                   | 1                | I <sup>2</sup> C, SPI | 1.71         |               |

| 16F84             | 18         | 13       | 1k                | 64             | 64           | —               | 1            | 10            | —                | —                   | —                | —                     | —            | 4.39          |

| 16F84A            | 18         | 13       | 1k                | 64             | 64           | —               | 1            | 20            | —                | —                   | —                | —                     | —            | 3.42          |

| 16F87             | 18         | 16       | 4k                | 398            | 256          | —               | 2 + 1        | 20            | 8                | ✓                   | 1                | All                   | 2.26         |               |

| 16F88             | 18         | 16       | 4k                | 368            | 256          | 7 x 10-bit      | 2 + 1        | 20            | 8                | ✓                   | 1                | All                   | 2.41         |               |

| 16F873A           | 28         | 22       | 4k                | 192            | 128          | 5 x 10-bit      | 2 + 1        | 20            | —                | ✓                   | 2                | All                   | 3.98         |               |

| 16F874A           | 40         | 33       | 4k                | 192            | 128          | 8 x 10-bit      | 2 + 1        | 20            | —                | ✓                   | 2                | All                   | 4.35         |               |

| 16F876A           | 28         | 22       | 8k                | 256            | 368          | 5 x 10-bit      | 2 + 1        | 20            | —                | ✓                   | 2                | All                   | 4.28         |               |

| 16F877A           | 40         | 33       | 8k                | 256            | 368          | 8 x 10-bit      | 2 + 1        | 20            | —                | ✓                   | 2                | All                   | 4.68         |               |

| 18F1220           | 18         | 16       | 2k                | 256            | 256          | 7 x 10-bit      | 1 + 3        | 40            | 8                | ✓                   | 1                | UART                  | 2.78         |               |

| 18F2320           | 28         | 25       | 4k                | 512            | 256          | 10 x 10-bit     | 1 + 3        | 40            | 8                | ✓                   | 1                | All                   | 4.85         |               |

| 18F4320           | 40         | 36       | 4k                | 512            | 256          | 13 x 10-bit     | 1 + 3        | 40            | 8                | ✓                   | 2                | All                   | 5.29         |               |

| 18F6520           | 64         | 52       | 16k               | 2048           | 1024         | 12 x 10-bit     | 1 + 3        | 40            | —                | ✓                   | 5                | All                   | 6.52         |               |

| 18F8621           | 80         | 68       | 32k               | 3840           | 1024         | 16 x 8-bit      | 1 + 3        | 40            | 10               | ✓                   | 14               | I <sup>2</sup> C, SPI | 8.25         |               |

| 18F8720           | 80         | 68       | 64k               | 3840           | 1024         | 16 x 10-bit     | 1 + 3        | 40            | —                | ✓                   | 5                | All                   | 10.90        |               |

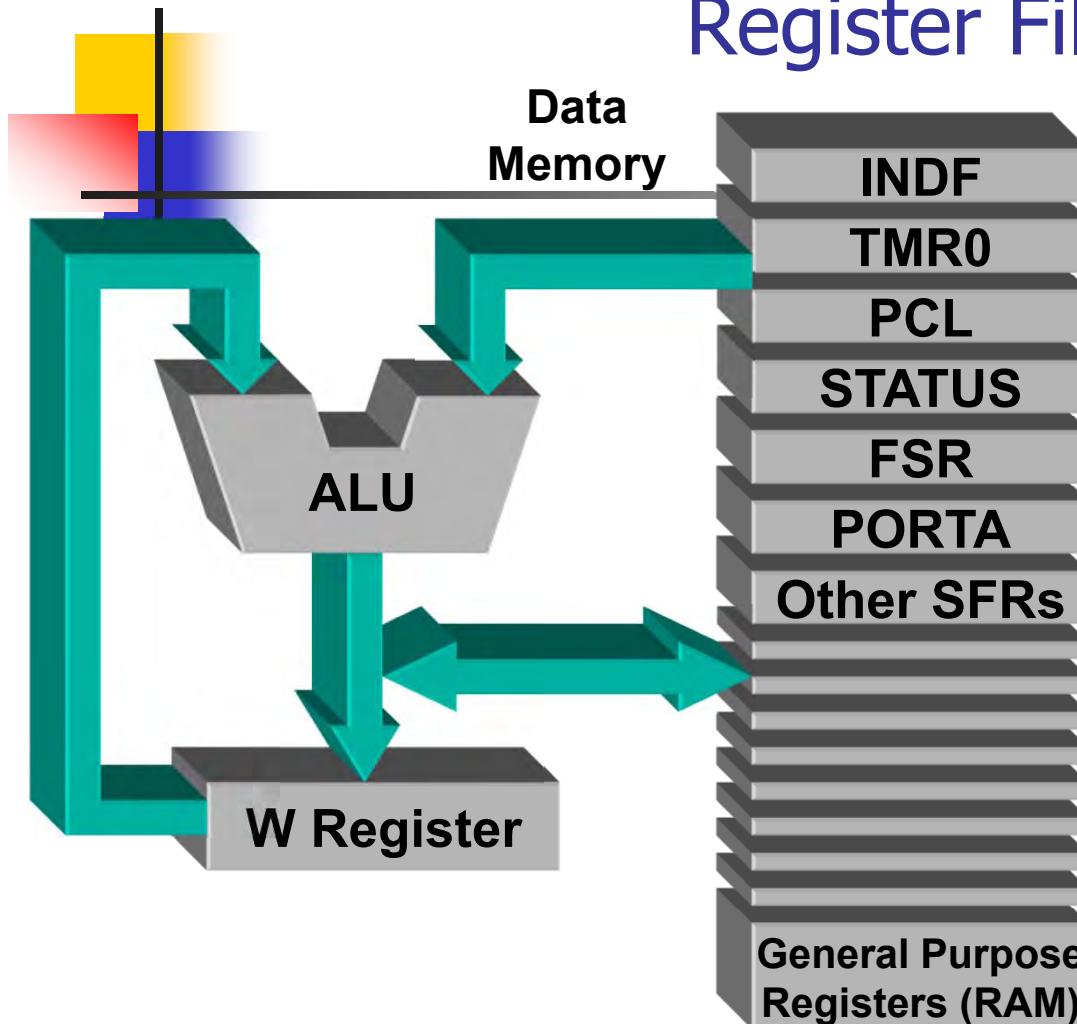

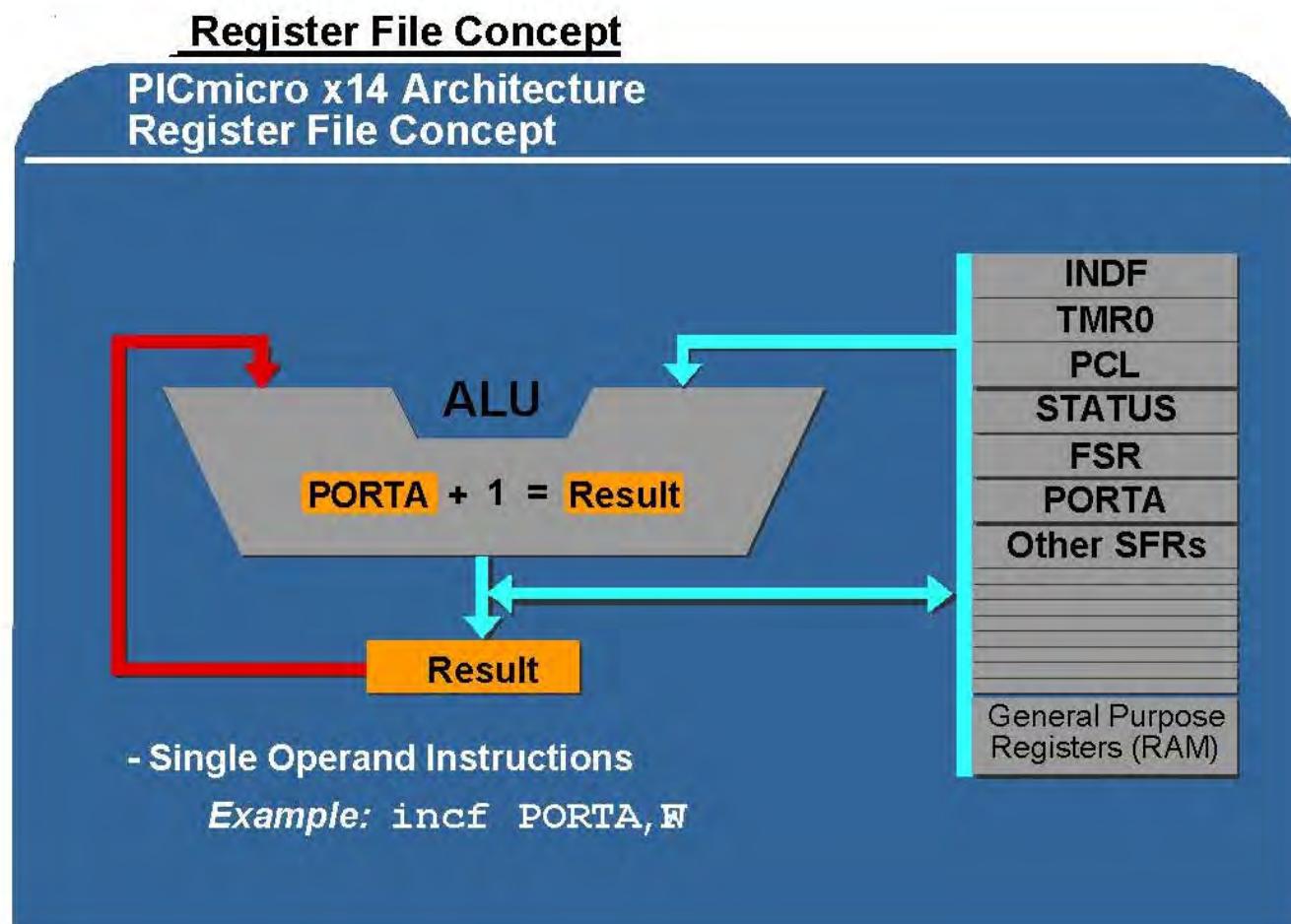

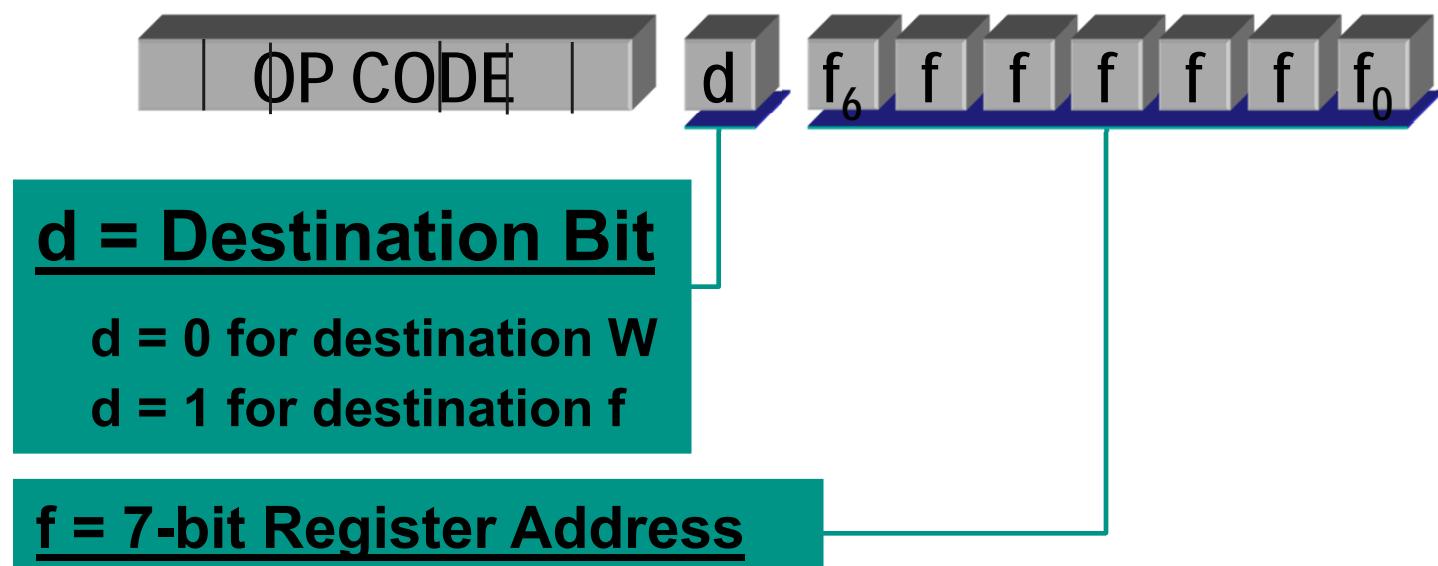

# PICmicro® MCU Architecture

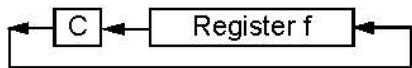

## Register File Concept

- RAM is a bank of general purpose registers

- Peripherals (I/O) are registers

- All instructions operate on any register

- Long word instruction allows direct addressing of registers

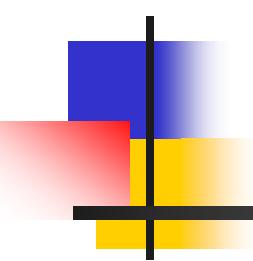

14-bit Instruction Format Example:

# PICmicro® MCU Architecture

## Register File Concept

# PIC 16F84 File Register Set

| REGISTER FILE MAP -<br>PIC16F84A                |                               |                                   |              |  |

|-------------------------------------------------|-------------------------------|-----------------------------------|--------------|--|

| File Address                                    |                               |                                   | File Address |  |

| 00h                                             | Indirect addr. <sup>(1)</sup> | Indirect addr. <sup>(1)</sup>     | 80h          |  |

| 01h                                             | TMRO                          | OPTION_REG                        | 81h          |  |

| 02h                                             | PCL                           | PCL                               | 82h          |  |

| 03h                                             | STATUS                        | STATUS                            | 83h          |  |

| 04h                                             | FSR                           | FSR                               | 84h          |  |

| 05h                                             | PORTA                         | TRISA                             | 85h          |  |

| 06h                                             | PORTB                         | TRISB                             | 86h          |  |

| 07h                                             | —                             | —                                 | 87h          |  |

| 08h                                             | EEDATA                        | EECON1                            | 88h          |  |

| 09h                                             | EEADDR                        | EECON2 <sup>(1)</sup>             | 89h          |  |

| 0Ah                                             | PCLATH                        | PCLATH                            | 8Ah          |  |

| 0Bh                                             | INTCON                        | INTCON                            | 8Bh          |  |

| 0Ch                                             |                               |                                   | 8Ch          |  |

| 68<br>General<br>Purpose<br>Registers<br>(SRAM) |                               | Mapped<br>(accesses)<br>in Bank 0 |              |  |

| 4Fh                                             |                               |                                   | CFh          |  |

| 50h                                             |                               |                                   | D0h          |  |

| 7Fh                                             | Bank 0                        |                                   | FFh          |  |

|                                                 | Bank 1                        |                                   |              |  |

Unimplemented data memory location, read as '0'.

**Note 1:** Not a physical register.

# PIC 16F84 File Register Set

## SPECIAL FUNCTION REGISTER FILE SUMMARY

| Addr          | Name                  | Bit 7                                                                 | Bit 6  | Bit 5 | Bit 4                                                  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on Power-on RESET | Details on page |  |  |  |  |

|---------------|-----------------------|-----------------------------------------------------------------------|--------|-------|--------------------------------------------------------|-------|-------|-------|-----------|-------------------------|-----------------|--|--|--|--|

| <b>Bank 0</b> |                       |                                                                       |        |       |                                                        |       |       |       |           |                         |                 |  |  |  |  |

| 00h           | INDF                  | Uses contents of FSR to address Data Memory (not a physical register) |        |       |                                                        |       |       |       | ----      | ----                    | 11              |  |  |  |  |

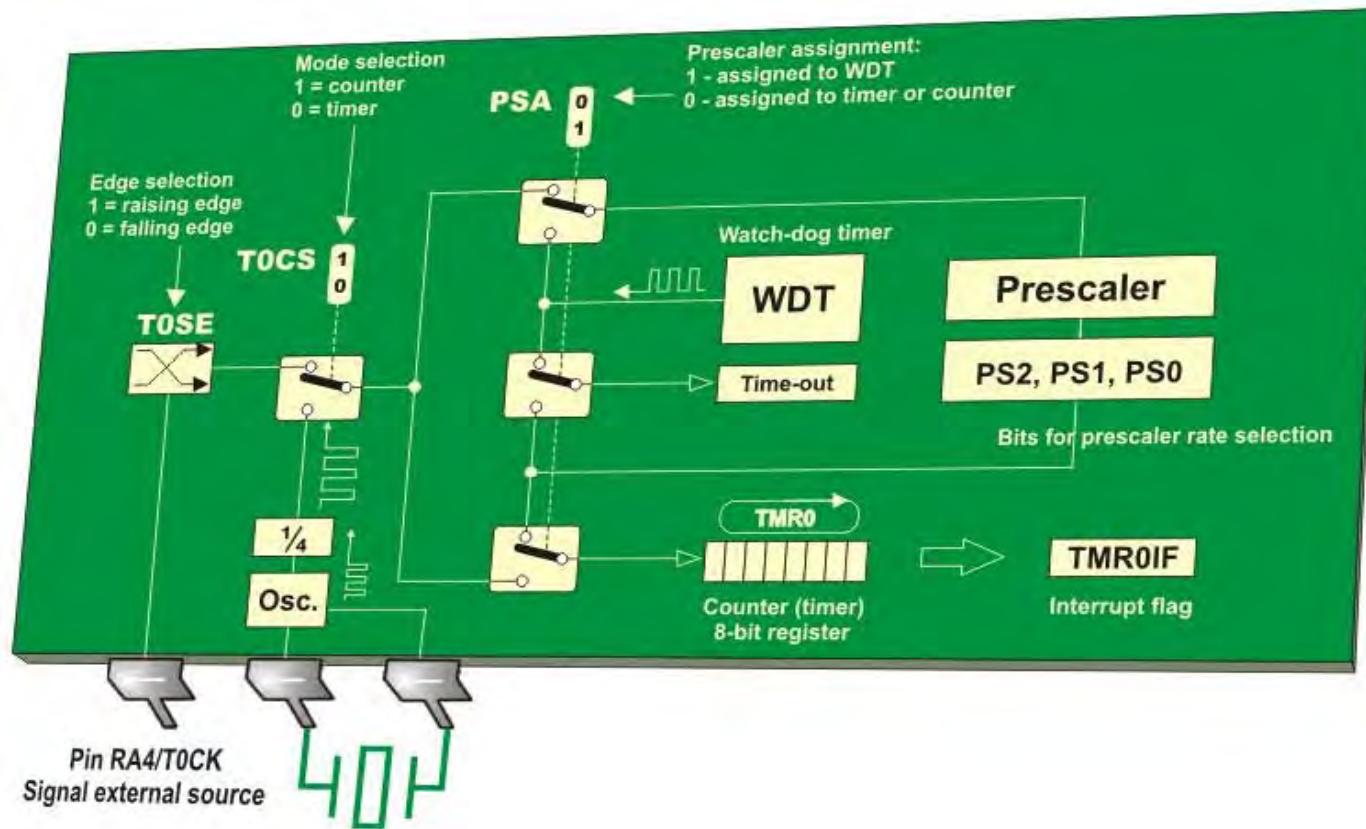

| 01h           | TMR0                  | 8-bit Real-Time Clock/Counter                                         |        |       |                                                        |       |       |       | xxxx xxxx | xxxx xxxx               | 20              |  |  |  |  |

| 02h           | PCL                   | Low Order 8 bits of the Program Counter (PC)                          |        |       |                                                        |       |       |       | 0000 0000 | 0000 0000               | 11              |  |  |  |  |

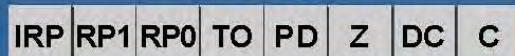

| 03h           | STATUS <sup>(2)</sup> | IRP                                                                   | RP1    | RP0   | TO                                                     | PD    | Z     | DC    | C         | 0001 1xxx               | 8               |  |  |  |  |

| 04h           | FSR                   | Indirect Data Memory Address Pointer 0                                |        |       |                                                        |       |       |       | xxxx xxxx | xxxx xxxx               | 11              |  |  |  |  |

| 05h           | PORTA <sup>(4)</sup>  | —                                                                     | —      | —     | RA4/T0CKI                                              | RA3   | RA2   | RA1   | RA0       | ---x xxxx               | 16              |  |  |  |  |

| 06h           | PORTB <sup>(5)</sup>  | RB7                                                                   | RB6    | RB5   | RB4                                                    | RB3   | RB2   | RB1   | RB0/INT   | xxxx xxxx               | 18              |  |  |  |  |

| 07h           | —                     | Unimplemented location, read as '0'                                   |        |       |                                                        |       |       |       | —         | —                       | —               |  |  |  |  |

| 08h           | EEDATA                | EEPROM Data Register                                                  |        |       |                                                        |       |       |       | xxxx xxxx | xxxx xxxx               | 13,14           |  |  |  |  |

| 09h           | EEADR                 | EEPROM Address Register                                               |        |       |                                                        |       |       |       | xxxx xxxx | xxxx xxxx               | 13,14           |  |  |  |  |

| 0Ah           | PCLATH                | —                                                                     | —      | —     | Write Buffer for upper 5 bits of the PC <sup>(1)</sup> |       |       |       | ---0 0000 | 0000 0000               | 11              |  |  |  |  |

| 0Bh           | INTCON                | GIE                                                                   | EEIE   | TOIE  | INTE                                                   | RBIE  | TOIF  | INTF  | RBIF      | 0000 000x               | 10              |  |  |  |  |

| <b>Bank 1</b> |                       |                                                                       |        |       |                                                        |       |       |       |           |                         |                 |  |  |  |  |

| 80h           | INDF                  | Uses Contents of FSR to address Data Memory (not a physical register) |        |       |                                                        |       |       |       | ----      | ----                    | 11              |  |  |  |  |

| 81h           | OPTION_REG            | RBPU                                                                  | INTEDG | T0CS  | T0SE                                                   | PSA   | PS2   | PS1   | PS0       | 1111 1111               | 9               |  |  |  |  |

| 82h           | PCL                   | Low order 8 bits of Program Counter (PC)                              |        |       |                                                        |       |       |       | 0000 0000 | 0000 0000               | 11              |  |  |  |  |

| 83h           | STATUS <sup>(2)</sup> | IRP                                                                   | RP1    | RP0   | TO                                                     | PD    | Z     | DC    | C         | 0001 1xxx               | 8               |  |  |  |  |

| 84h           | FSR                   | Indirect data memory address pointer 0                                |        |       |                                                        |       |       |       | xxxx xxxx | xxxx xxxx               | 11              |  |  |  |  |

| 85h           | TRISA                 | —                                                                     | —      | —     | PORTA Data Direction Register                          |       |       |       | ---1 1111 | 1111 1111               | 16              |  |  |  |  |

| 86h           | TRISB                 | PORTB Data Direction Register                                         |        |       |                                                        |       |       |       | 1111 1111 | 1111 1111               | 18              |  |  |  |  |

| 87h           | —                     | Unimplemented location, read as '0'                                   |        |       |                                                        |       |       |       | —         | —                       | —               |  |  |  |  |

| 88h           | EECON1                | —                                                                     | —      | —     | EEIF                                                   | WRERR | WREN  | WR    | RD        | ---0 x000               | 13              |  |  |  |  |

| 89h           | EECON2                | EEPROM Control Register 2 (not a physical register)                   |        |       |                                                        |       |       |       | ----      | ----                    | 14              |  |  |  |  |

| 0Ah           | PCLATH                | —                                                                     | —      | —     | Write buffer for upper 5 bits of the PC <sup>(1)</sup> |       |       |       | ---0 0000 | 0000 0000               | 11              |  |  |  |  |

| 0Bh           | INTCON                | GIE                                                                   | EEIE   | TOIE  | INTE                                                   | RBIE  | TOIF  | INTF  | RBIF      | 0000 000x               | 10              |  |  |  |  |

Legend: x = unknown, u = unchanged. - = unimplemented, read as '0', q = value depends on condition

**Note 1:** The upper byte of the program counter is not directly accessible. PCLATH is a slave register for PC<12:8>. The contents of PCLATH can be transferred to the upper byte of the program counter, but the contents of PC<12:8> are never transferred to PCLATH.

**2:** The TO and PD status bits in the STATUS register are not affected by a MCLR Reset.

**3:** Other (non power-up) RESETS include: external RESET through MCLR and the Watchdog Timer Reset.

**4:** On any device RESET, these pins are configured as inputs.

**5:** This is the value that will be in the port output latch.

# PICmicro® MCU Architecture

## Data Memory: Immediate Addressing

### Immediate Addressing

**PICmicro x14 Architecture**

**Program Memory: Immediate Addressing**

**8-bit constant (literal) value included in instruction word**

**Used by literal instructions such as movlw, addlw, retlw etc**

**retlw k**

Return from

subroutine with

the literal k<8>

in the W register

**14 bit instruction for Literal Instructions**

# PICmicro® MCU Architecture

## Data Memory: Direct Addressing

### Data Memory: Direct Addressing

#### PICmicro x14 Architecture Data Memory: Direct Addressing

7-bit direct address from the instruction

2-bits from the STATUS register

*Example Instruction: movf PORTB,W*

#### Status Register

14 bit instruction

2 bits

from

Status

Register

7-bits from instruction word

Effective 9-bit Register Address:  $2^9 = 512$  address locations

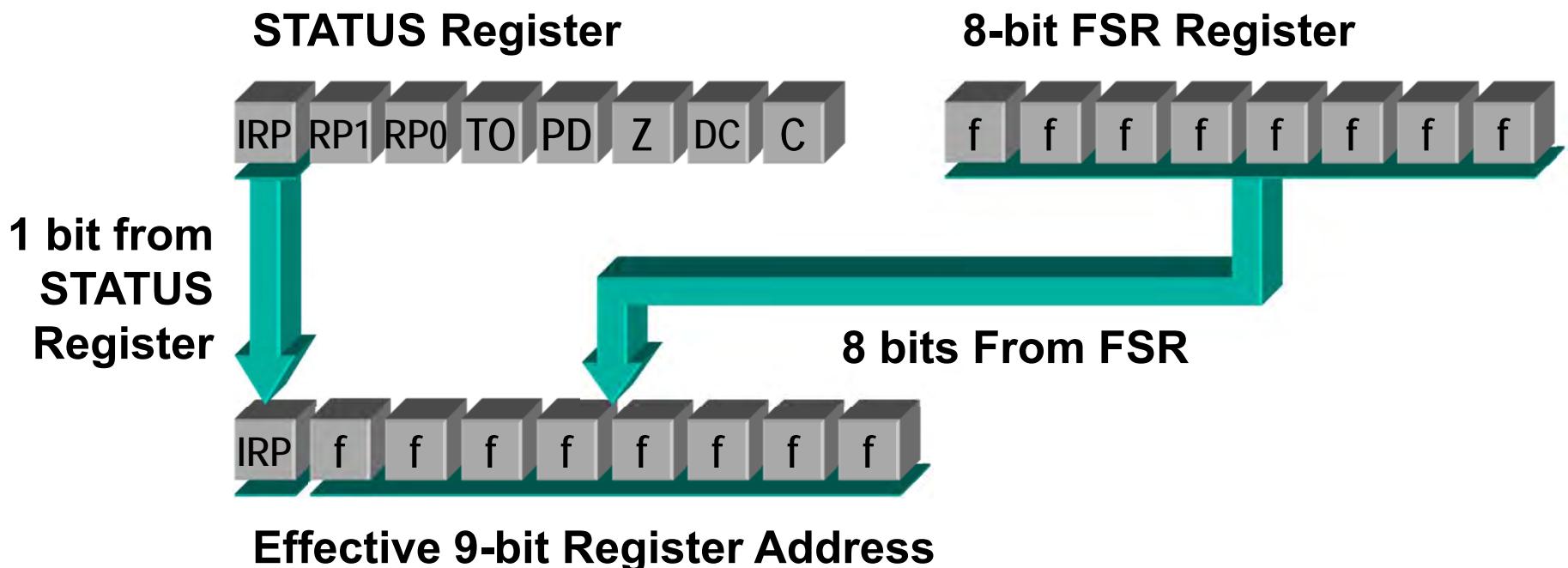

# PICmicro® MCU Architecture

## Data Memory: Indirect Addressing

- 8-bit indirect address from the FSR (File Select Register)

- 1-bit from STATUS register

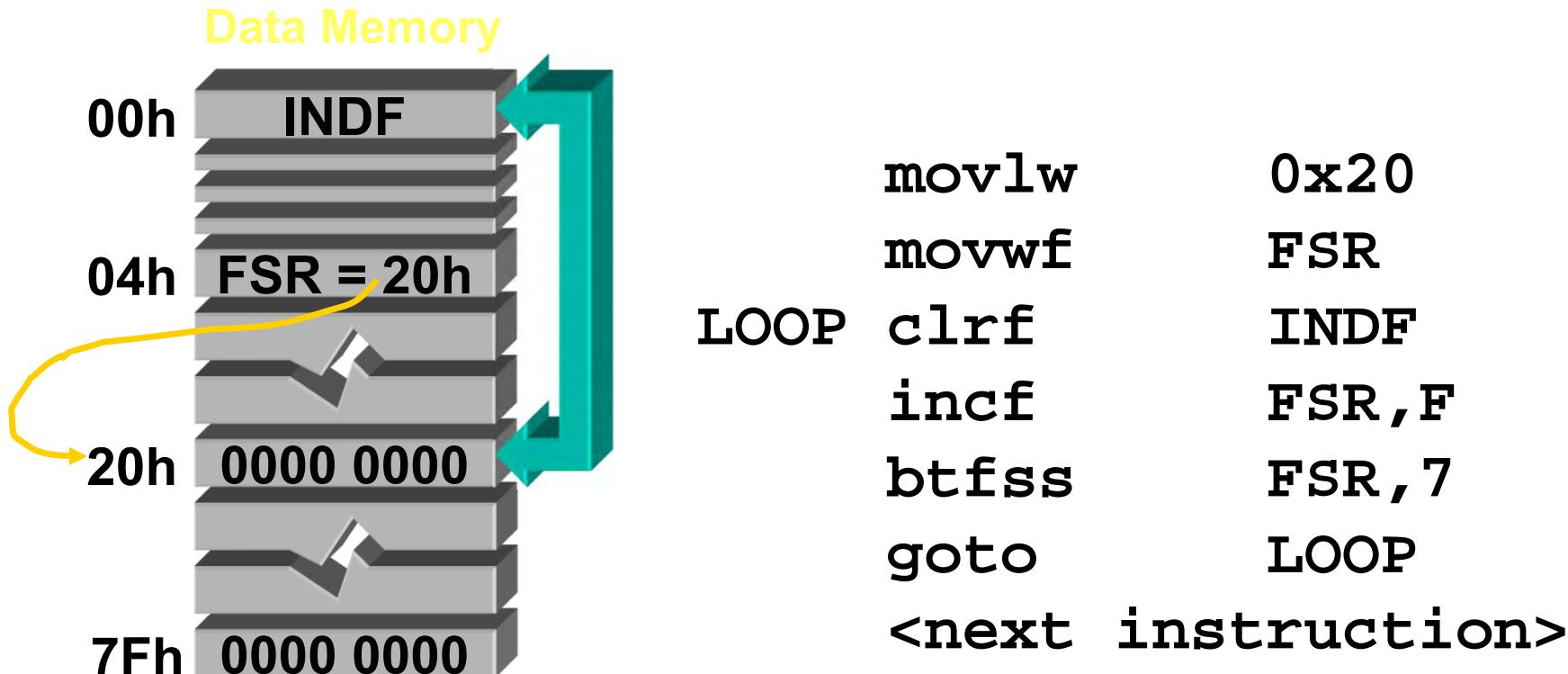

# PICMICRO® MCU Architecture

## Data Memory: Indirect Addressing

□ Clear all RAM locations from 0x20 to 0x7F

- Indirect address is loaded into FSR

- Every time INDF is used as operand, register pointed to by FSR is actually used

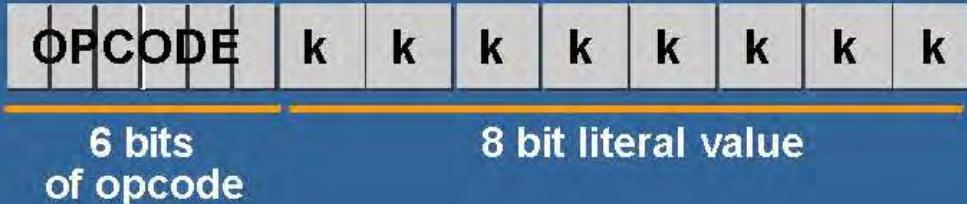

# PICMicro® MCU Architecture

## Data Memory: Immediate Addressing

- 8-bit constant (literal) value included in instruction word

- Used by literal instructions such as movlw, addlw, retlw, etc.

### 14-bit Instruction for Literal Instructions

# PICmicro® MCU Architecture

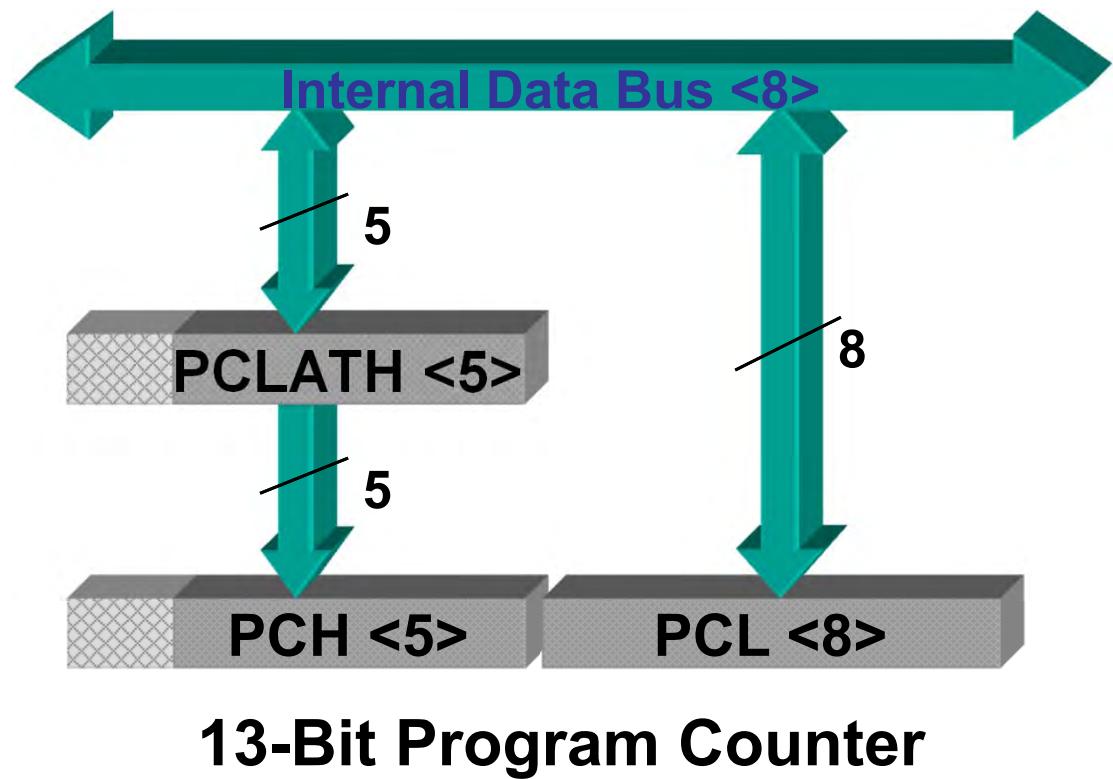

## Data Memory: PC Absolute Addressing

- Used by control instructions CALL and GOTO to modify the PC (Program Counter)

- A constant value may also be written directly to the PC (next slide)

### 14-bit Instruction for CALL and GOTO

This is for 2K addressing

# PICmicro® MCU Architecture

## Data Memory: PC Relative Addressing

- PC Relative Addressing:

- Used to perform a computed goto by adding an offset directly to the 13-bit Program Counter (8K addressing)

- To write to PC - Applies when PC is the destination of an operation's result

# PICmicro® MCU Architecture

## Data Memory: PC Relative Addressing

- First write high byte to PCLATH

- Next write low byte to PCL--this loads the entire 13-bit value to PC

- To read the PC

- Read low byte from PCL

- PCLATH is *NOT* loaded with value from PCH

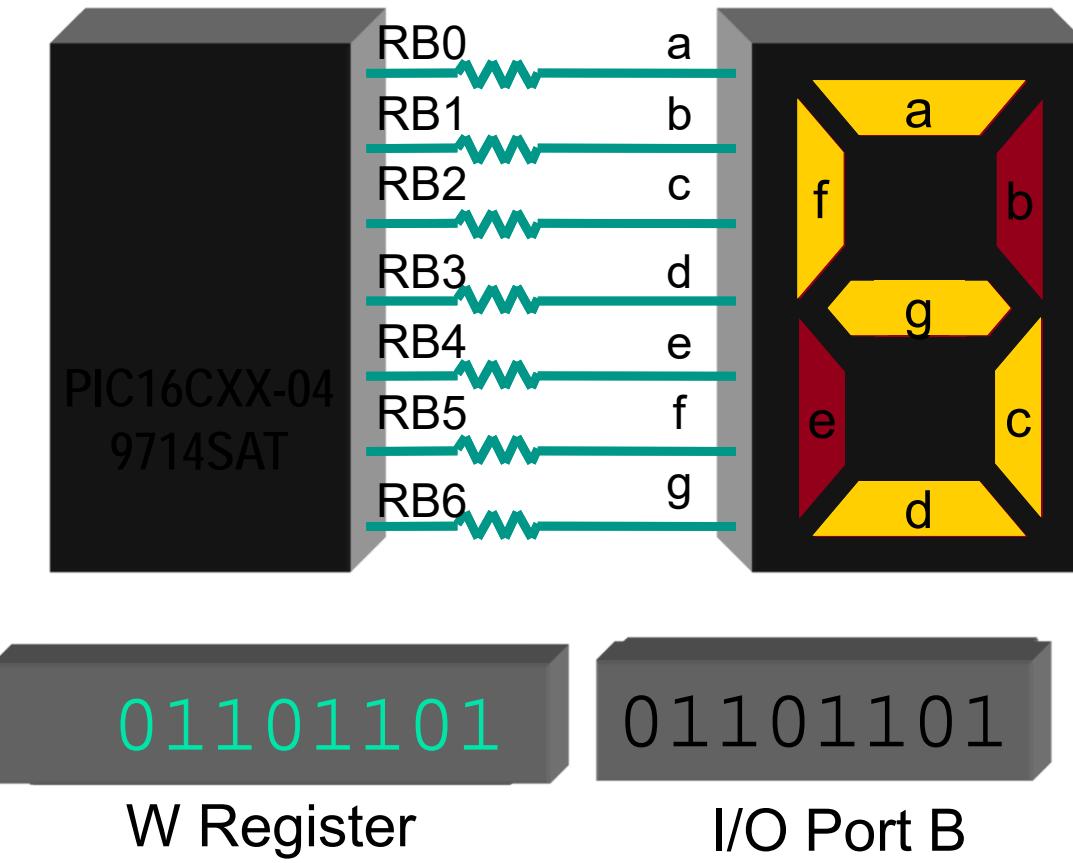

# PICmicro® MCU Architecture

## Data Memory: PC Relative Addressing

```

org 0x10

ctrl PCLATH

movf DisplayValue,W

call SevenSegmentDecode

movwf PORTB

goto Continue

SevenSegmentDecode

addwf PCL,F

retlw B'00111111' ;decode 0

retlw B'00000110' ;decode 1

retlw B'01011011' ;decode 2

retlw B'01001111' ;decode 3

retlw B'01100110' ;decode 4

retlw B'01101101' ;decode 5

retlw B'01111101' ;decode 6

retlw B'00000111' ;decode 7

retlw B'01111111' ;decode 8

retlw B'01101111' ;decode 9

Continue

```

## Look-up Table Example

# Lecture\_3

---

# Instruction Set (x14)

# PICmicro® MCU Instruction Set

## PICmicro® x14 Instruction Set

- 12-bit core → 33 instructions

- 14-bit core → 35 instructions

- 16-bit enhanced core → 77 instructions

- Easy to learn

- High compaction

- Very powerful single-word instructions

- All single- cycle except program branches

- Upward compatibility of instructions

# PICmicro® MCU Instruction Set Summary

| Byte-Oriented Operations |     |                              | Bit-Oriented Operations               |     |                             |

|--------------------------|-----|------------------------------|---------------------------------------|-----|-----------------------------|

| <b>NOP</b>               | -   | No Operation                 | <b>BCF</b>                            | f,b | Bit clear f                 |

| <b>MOVWF</b>             | f   | Move W to f                  | <b>BSF</b>                            | f,b | Bit set f                   |

| <b>MOVF</b>              | f,d | Move f                       | <b>BTFSC</b>                          | f,b | Bit test f, skip if clear   |

| <b>CLRW</b>              | -   | Clear W                      | <b>BTFSS</b>                          | f,b | Bit test f, skip if set     |

| <b>CLRF</b>              | f   | Clear f                      | <b>Literal and Control Operations</b> |     |                             |

| <b>INCF</b>              | f,d | Increment f                  | <b>SLEEP</b>                          | -   | Go into standby mode        |

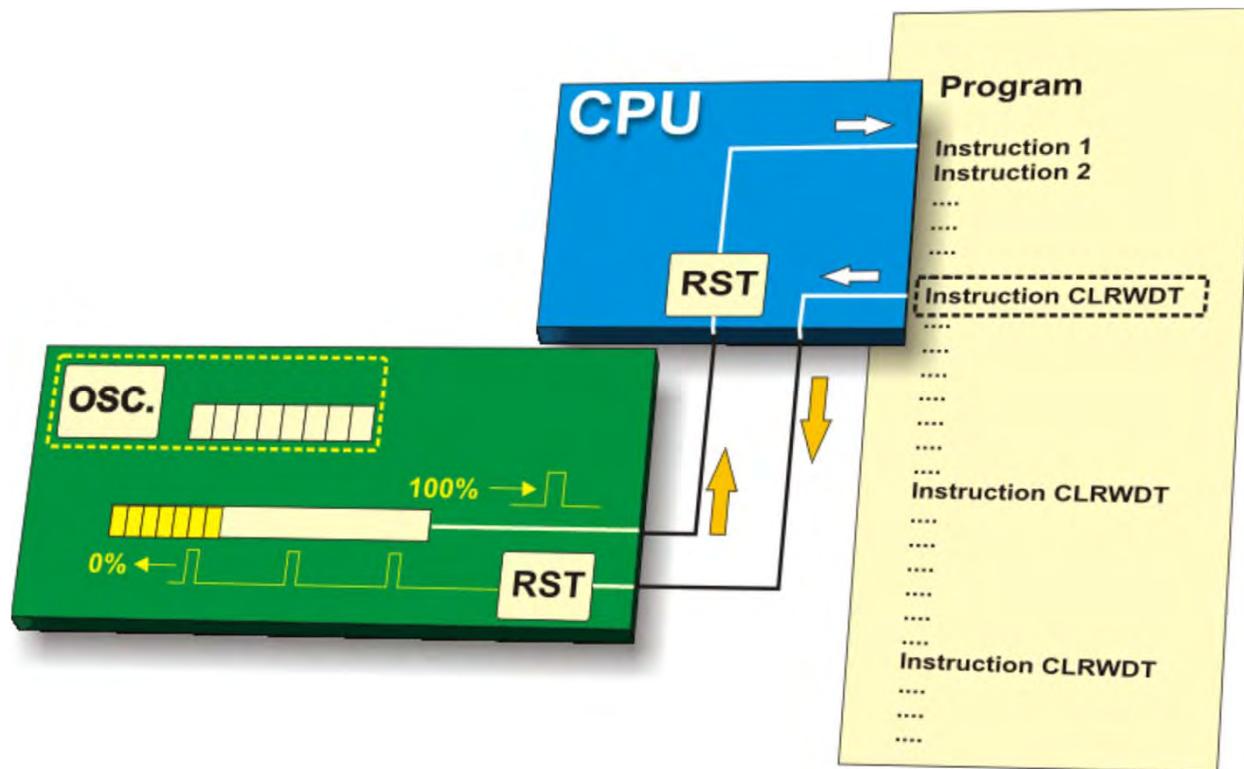

| <b>DECFSZ</b>            | f,d | Decrement f                  | <b>CLRWDT</b>                         | -   | Clear watchdog timer        |

| <b>ADDWF</b>             | f,d | Add W and f                  | <b>RETLW</b>                          | k   | Return, place literal in W  |

| <b>SUBWF</b>             | f,d | Subtract W from f            | <b>RETFIE</b>                         | -   | Return from interrupt       |

| <b>ANDWF</b>             | f,d | AND W and f                  | <b>RETURN</b>                         | -   | Return from subroutine      |

| <b>IORWF</b>             | f,d | Inclusive OR W and f         | <b>CALL</b>                           | k   | Call subroutine             |

| <b>XORWF</b>             | f,d | Exclusive OR W and f         | <b>GOTO</b>                           | k   | Go to address (k is 9bit)   |

| <b>COMF</b>              | f,d | Complement f                 | <b>MOVLW</b>                          | k   | Move literal to W           |

| <b>RRF</b>               | f,d | Rotate right f through carry | <b>IORLW</b>                          | k   | Inclusive OR literal with W |

| <b>RLF</b>               | f,d | Rotate left f through carry  | <b>ADDLW</b>                          | k   | Add literal with W          |

| <b>INCFSZ</b>            | f,d | Increment f, skip if zero    | <b>SUBLW</b>                          | k   | Subtract W from literal     |

| <b>DECFSZ</b>            | f,d | Decrement f, skip if zero    | <b>ANDLW</b>                          | k   | AND literal with W          |

| <b>SWAPF</b>             | f,d | Swap nibbles of f            | <b>XORLW</b>                          | k   | Exclusive OR literal with W |

f = File Register, k = literal value (8 bit), b = bit address <0,7>, d = destination (0=W, 1=f)

# PICmicro® MCU Instruction Set

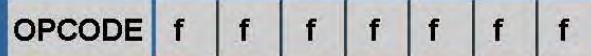

## Byte-Oriented Operations

### Byte-Oriented Operations

|        |     |

|--------|-----|

| NOP    | -   |

| MOVWF  | f   |

| CLRW   | -   |

| CLRF   | f   |

| SUBWF  | f,d |

| DECFSZ | f,d |

| IORWF  | f,d |

| ANDWF  | f,d |

| XORWF  | f,d |

| ADDWF  | f,d |

| MOVF   | f,d |

| COMF   | f,d |

| INCF   | f,d |

| DECFSZ | f,d |

| RRF    | f,d |

| RLF    | f,d |

| SWAPF  | f,d |

| INCFSZ | f,d |

### 14-bit Instruction for Byte Oriented Operations

**Example:**

**ADDWF REG, W**

**ADDWF f, d**

# PICmicro® MCU Instruction Set

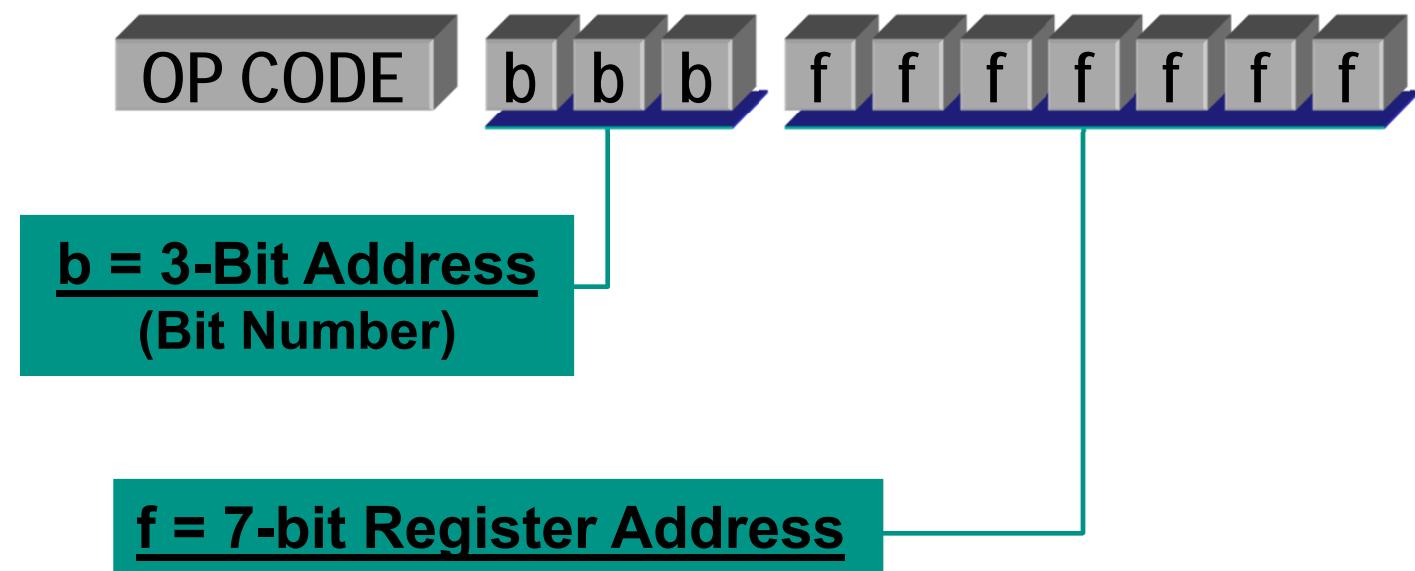

## Bit-Oriented Operations

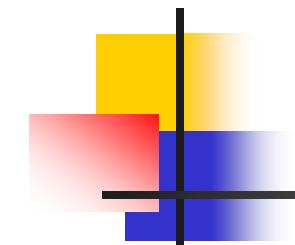

### Bit-Oriented Operations

BCF f,b

BSF f,b

BTFSC f,b

BTFSS f,b

### 14-bit Instruction for Bit Oriented Operations

Example:

**BTFSC**      **STATUS, C**

*BTFSC*      *f, b*

# PICmicro® MCU Instruction Set

## Literal and Control Operations

### Literal and Control Operations

|        |   |

|--------|---|

| SLEEP  | - |

| CLRWDT | - |

| RETLW  | k |

| RETFIE | - |

| RETURN | - |

| CALL   | k |

| GOTO   | k |

| MOVLW  | k |

| IORLW  | k |

| ADDLW  | k |

| SUBLW  | k |

| ANDLW  | k |

| XORLW  | k |

### 14-bit Instruction for Literal Operations

Example:

**MOVLW 0x2F**

*MOVLW k*

# 14-Bit Core Instruction Set Examples

| <b>ADDLW</b>     | <b>Add Literal and W</b>                                                                                          |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | <code>[label] ADDLW k</code>                                                                                      |

| Operands:        | $0 \leq k \leq 255$                                                                                               |

| Operation:       | $(W) + k \rightarrow (W)$                                                                                         |

| Status Affected: | C, DC, Z                                                                                                          |

| Description:     | The contents of the W register are added to the eight-bit literal 'k' and the result is placed in the W register. |

| <b>ADDWF</b>     | <b>Add W and f</b>                                                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | <code>[label] ADDWF f,d</code>                                                                                                                                     |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                               |

| Operation:       | $(W) + (f) \rightarrow (\text{destination})$                                                                                                                       |

| Status Affected: | C, DC, Z                                                                                                                                                           |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| <b>ANDLW</b>     | <b>AND Literal with W</b>                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Syntax:          | <code>[label] ANDLW k</code>                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                           |

| Operation:       | $(W) .AND. (k) \rightarrow (W)$                                                                               |

| Status Affected: | Z                                                                                                             |

| Description:     | The contents of W register are AND'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| <b>ANDWF</b>     | <b>AND W with f</b>                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | <code>[label] ANDWF f,d</code>                                                                                                                     |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                               |

| Operation:       | $(W) .AND. (f) \rightarrow (\text{destination})$                                                                                                   |

| Status Affected: | Z                                                                                                                                                  |

| Description:     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

# 14-Bit Core Instruction Set Examples

## **BCF** Bit Clear f

|                  |                                          |

|------------------|------------------------------------------|

| Syntax:          | [label] BCF f,b                          |

| Operands:        | $0 \leq f \leq 127$<br>$0 \leq b \leq 7$ |

| Operation:       | $0 \rightarrow (f<b>)$                   |

| Status Affected: | None                                     |

| Description:     | Bit 'b' in register 'f' is cleared.      |

## **BSF** Bit Set f

|                  |                                          |

|------------------|------------------------------------------|

| Syntax:          | [label] BSF f,b                          |

| Operands:        | $0 \leq f \leq 127$<br>$0 \leq b \leq 7$ |

| Operation:       | $1 \rightarrow (f<b>)$                   |

| Status Affected: | None                                     |

| Description:     | Bit 'b' in register 'f' is set.          |

## **BTFS** Bit Test f, Skip if Set

|                  |                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFS f,b                                                                                                                                                                                        |

| Operands:        | $0 \leq f \leq 127$<br>$0 \leq b < 7$                                                                                                                                                                   |

| Operation:       | skip if $(f<b>) = 1$                                                                                                                                                                                    |

| Status Affected: | None                                                                                                                                                                                                    |

| Description:     | If bit 'b' in register 'f' is '0', the next instruction is executed.<br>If bit 'b' is '1', then the next instruction is discarded and a <b>NOP</b> is executed instead, making this a 2TCY instruction. |

## **BTFC** Bit Test, Skip if Clear

|                  |                                                                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFC f,b                                                                                                                                                                                                    |

| Operands:        | $0 \leq f \leq 127$<br>$0 \leq b \leq 7$                                                                                                                                                                            |

| Operation:       | skip if $(f<b>) = 0$                                                                                                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b' in register 'f' is '0', the next instruction is discarded, and a <b>NOP</b> is executed instead, making this a 2TCY instruction. |

# 14-Bit Core Instruction Set Examples

| CLRWDT           | Clear Watchdog Timer                                                                                                                                          | CALL             | Call Subroutine                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRWDT                                                                                                                                       | Syntax:          | [ <i>label</i> ] CALL <i>k</i>                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                          | Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                    |

| Operation:       | $00h \rightarrow \text{WDT}$<br>$0 \rightarrow \text{WDT prescaler}$ ,<br>$1 \rightarrow \overline{\text{TO}}$<br>$1 \rightarrow \overline{\text{PD}}$        | Operation:       | $(\text{PC})+1 \rightarrow \text{TOS}$ ,<br>$k \rightarrow \text{PC}<10:0>$ ,<br>$(\text{PCLATH}<4:3>) \rightarrow \text{PC}<12:11>$                                                                                                    |

| Status Affected: | $\overline{\text{TO}}$ , $\overline{\text{PD}}$                                                                                                               | Status Affected: | None                                                                                                                                                                                                                                    |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set. | Description:     | Call Subroutine. First, return address ( $\text{PC}+1$ ) is pushed onto the stack. The eleven-bit immediate address is loaded into PC bits $<10:0>$ . The upper bits of the PC are loaded from PCLATH. CALL is a two-cycle instruction. |

| COMF             | Complement f                                                                                                                                                  | CLRF             | Clear f                                                                                                                                                                                                                                 |

| Syntax:          | [ <i>label</i> ] COMF <i>f,d</i>                                                                                                                              | Syntax:          | [ <i>label</i> ] CLRF <i>f</i>                                                                                                                                                                                                          |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                          | Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                                                     |

| Operation:       | $(\bar{f}) \rightarrow (\text{destination})$                                                                                                                  | Operation:       | $00h \rightarrow (f)$<br>$1 \rightarrow Z$                                                                                                                                                                                              |

| Status Affected: | <i>Z</i>                                                                                                                                                      | Status Affected: | <i>Z</i>                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'.                | Description:     | The contents of register 'f' are cleared and the Z bit is set.                                                                                                                                                                          |

# 14-Bit Core Instruction Set Examples

| DECF             | Decrement f                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | <code>[/label] DECF f,d</code>                                                                                                       |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                 |

| Operation:       | $(f) - 1 \rightarrow (\text{destination})$                                                                                           |

| Status Affected: | Z                                                                                                                                    |

| Description:     | Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| CLRW             | Clear W                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | <code>[ /label ] CLRW</code>                                                                                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                                                                                               |

| Operation:       | $00h \rightarrow (W)$<br>$1 \rightarrow Z$                                                                                                                                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                  |

| Description:     | W register is cleared. Zero bit (Z) is set.                                                                                                                                                                                                                                                        |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                             |

| Syntax:          | <code>[ /label ] DECFSZ f,d</code>                                                                                                                                                                                                                                                                 |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                               |

| Operation:       | $(f) - 1 \rightarrow (\text{destination})$ ;<br>skip if result = 0                                                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead, making it a 2TCY instruction. |

# 14-Bit Core Instruction Set Examples

|                  |                                                                                                                                                                                                                                                                                                  |                  |                                                                                                                                                                                   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>INCFSZ</b>    | <b>Increment f, Skip if 0</b>                                                                                                                                                                                                                                                                    | <b>GOTO</b>      | <b>Unconditional Branch</b>                                                                                                                                                       |

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                      | Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                           |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                             | Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |

| Operation:       | $(f) + 1 \rightarrow (\text{destination})$ ,<br>skip if result = 0                                                                                                                                                                                                                               | Operation:       | $k \rightarrow \text{PC} <10:0>$<br>$\text{PCLATH} <4:3> \rightarrow \text{PC} <12:11>$                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                             | Status Affected: | None                                                                                                                                                                              |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.<br>If the result is 1, the next instruction is executed. If the result is 0, a NOP is executed instead, making it a 2TCY instruction. | Description:     | GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction. |

| <b>IORLW</b>     | <b>Inclusive OR Literal with W</b>                                                                                                                                                                                                                                                               | <b>INCF</b>      | <b>Increment f</b>                                                                                                                                                                |

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                                                                                                                                                                                         | Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                                                                                              | Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                                              |

| Operation:       | $(W) .OR. k \rightarrow (W)$                                                                                                                                                                                                                                                                     | Operation:       | $(f) + 1 \rightarrow (\text{destination})$                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                | Status Affected: | Z                                                                                                                                                                                 |

| Description:     | The contents of the W register are OR'ed with the eight-bit literal 'k'. The result is placed in the W register.                                                                                                                                                                                 | Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.                        |

# 14-Bit Core Instruction Set Examples

| IORWF            | Inclusive OR W with f                                                                                                                                       | MOVF             | Move f                                                                                                                                                                                                                                                    |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label] IORWF f,d                                                                                                                                          | Syntax:          | [ label] MOVF f,d                                                                                                                                                                                                                                         |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                        | Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                                                                                                                      |

| Operation:       | $(W) .OR. (f) \rightarrow (\text{destination})$                                                                                                             | Operation:       | $(f) \rightarrow (\text{destination})$                                                                                                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                           | Status Affected: | Z                                                                                                                                                                                                                                                         |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. | Description:     | The contents of register f are moved to a destination dependant upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register, since status flag Z is affected. |

| RETFIE           | Return from Interrupt                                                                                                                                       | MOVLW            | Move Literal to W                                                                                                                                                                                                                                         |

| Syntax:          | [ label] RETFIE                                                                                                                                             | Syntax:          | [ label] MOVLW k                                                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                        | Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                                                       |

| Operation:       | $\text{TOS} \rightarrow \text{PC},$<br>$1 \rightarrow \text{GIE}$                                                                                           | Operation:       | $k \rightarrow (W)$                                                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                        | Status Affected: | None                                                                                                                                                                                                                                                      |

| Description:     |                                                                                                                                                             | Description:     | The eight-bit literal 'k' is loaded into W register. The don't cares will assemble as 0's.                                                                                                                                                                |

# 14-Bit Core Instruction Set Examples

## RETLW      Return with Literal in W

|                  |                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW <i>k</i>                                                                                                                                         |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                     |

| Operation:       | $k \rightarrow (W)$ ;<br>$TOS \rightarrow PC$                                                                                                                           |

| Status Affected: | None                                                                                                                                                                    |

| Description:     | The W register is loaded with the eight-bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction. |

## MOVWF

## Move W to f

|                  |                                                     |

|------------------|-----------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF <i>f</i>                     |

| Operands:        | $0 \leq f \leq 127$                                 |

| Operation:       | $(W) \rightarrow (f)$                               |

| Status Affected: | None                                                |

| Description:     | Move data from W register to register ' <i>f</i> '. |

## RETURN      Return from Subroutine

|                  |                                                                                                                                                |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETURN                                                                                                                        |

| Operands:        | None                                                                                                                                           |

| Operation:       | $TOS \rightarrow PC$                                                                                                                           |

| Status Affected: | None                                                                                                                                           |

| Description:     | Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a two-cycle instruction. |

## NOP

## No Operation

|                  |                      |

|------------------|----------------------|

| Syntax:          | [ <i>label</i> ] NOP |

| Operands:        | None                 |

| Operation:       | No operation         |

| Status Affected: | None                 |

| Description:     | No operation.        |

# 14-Bit Core Instruction Set Examples

| RLF              | Rotate Left f through Carry                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label] RLF f,d                                                                                                                                                                                  |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                                                              |

| Operation:       | See description below                                                                                                                                                                             |

| Status Affected: | C                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is stored back in register 'f'. |

|                  |                                                                                                                |

| SUBWF            | Subtract W from f                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label] SUBWF f,d                                                                                                                                                          |

| Operands:        | $0 \leq f \leq 127$<br>$d \in [0,1]$                                                                                                                                        |

| Operation:       | $(f) - (W) \rightarrow (\text{destination})$                                                                                                                                |

| Status Affected: | C, DC, Z                                                                                                                                                                    |

| Description:     | Subtract (2's complement method) W register from register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| SUBLW            | Subtract W from Literal                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label] SUBLW k                                                                                                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                                                                                           |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register.                                                                       |

| RRF              | Rotate Right f through Carry                                                                                                                                                                       |

| Syntax:          | [ label] RRF f,d                                                                                                                                                                                   |