Faculty of Engineering

Electrical Engineering Department

Communications and Electronics Program

# Logic Circuit Design Class Notes EE242

**SPRING 2015**

#### LOGIC CIRCUIT DESIGN EE242

Term: SPRING 2015

Instructor: Dr. M. El-Banna, Room: EE-Building 4<sup>th</sup> floor

Classes : Group1 SUN 10:10 – 11:40

Group2 SUN 2:00 – 03:30

Topics to be covered:

Chapter 1: Implementation of Logic Functions

Chapter 2: Design of Combinational Circuits

Chapter 3: Sequential Circuits

Chapter 4: Design of Synchronous Sequential Circuits

Chapter 5: Introduction to Counters, Registers, and HDL language

Text Book: Fundamental Logic Design, Thomson, Charles Roth

Further Reading: Contemporary Digital Design, Johnson and Karim

#### **Grading Policy:**

Midterm 30

LAB 30

Final 90

#### ILOs of the Logic Circuit Design EE242

- 1. Comprehend and use the main blocks of combinational circuits, MUXs, ROMs, PLAs, PALs, Decoders and Encoders

- 2. Design combinational circuits using different blocks.

- 3. Carry out a project using the NI- LabVIEW software package to design and test combinational circuits, if time allows.

- 4. Differentiate between combinational and sequential circuits

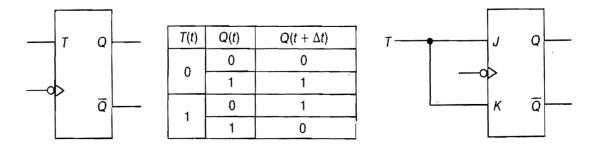

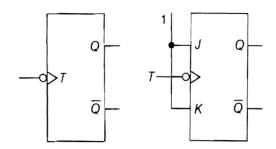

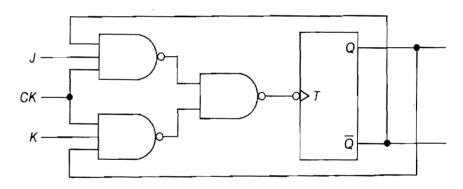

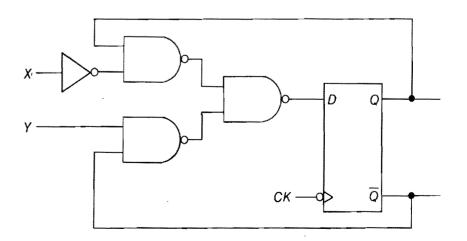

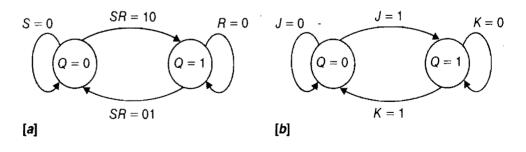

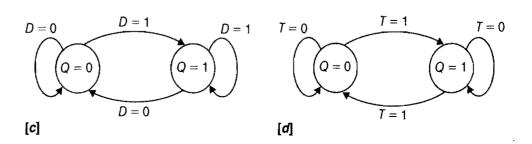

- 5. Review all types of Flip Flops used in sequential circuits and represent their functions by state diagrams.

- 6. Convert verbally stated design problems into state diagrams and hence state tables.

- 7. Differentiate between Mealy and Moore finite state machines.

- 8. Follow up the design procedure of sequential circuits starting from implication tables through partition tables, state transition tables, excitations maps and eventually the hardware implementation.

- 9. Use the Verilog/VHDL language to design come known logic circuits, combinational and/or sequential

- 10. Comprehend and design synchronous and asynchronous counters

#### CHAPTER FOUR

# Implementation of Logic Functions\_\_\_\_\_

#### 4.1 Introduction

The design mechanism of combinational logic circuits is usually a multi-step process. The realization, and the subsequent minimization, of the logic function is not the end of the design. We are already familiar with the various schemes for coming up with the reduced logic function either in the SOP or in the POS format. These forms can be translated easily into either a familiar AND-OR or OR-AND pattern of logic circuits. However, we have also seen in the last chapter that digital ICs have several practical limitations that may affect the implementation of circuits. These include the fan-in and fan-out limitations and the fact that ICs are more frequently available in the NAND and NOR form than in the AND and OR form. NAND and NOR gates are easier to realize with electronic components and are, therefore, the basic ingredients used in all of the logic families. Consequently, it is important for the designer to be familiar with the techniques for translating the reduced function so that either NAND gates or NOR gates may be used.

Combinational circuits may be realized using a standardized combinational unit called a multiplexer (MUX). In the MUX some of the input variables are used as input selectors for the unit and the remaining variables are entered as data inputs. Two other devices, read-only memories (ROMs) and programmable logic arrays (PLAs), are also frequently used to implement combinational networks. This chapter will explore the possibilities of using only one type of gate or one of the modules—MUX, ROM, PAL, or PLA—for the realization of combinational circuits. Such exploration is extremely useful because most designers usually choose to use only one type of basic gate unless there is a particular reason for doing otherwise. After studying this chapter, you should be able to:

O Design combinational circuits using only NAND gates;

- O Design combinational circuits using only NOR gates;

- O Design combinational circuits using single- or multilevel multiplexers (MUXs);

- O Design combinational circuits using read-only memories (ROMs);

- O Design combinational circuits using programmable logic arrays (PLAs);

- O Construct a complex circuit using the outputs of a known functional unit.

### 4.2 Universal Logic Elements

In practice many logic circuits are built using only NAND and NOR gates because the basic gates in some of the logic families such as TTL and CMOS are NAND and NOR, respectively. NAND and NOR gates are considered universal logic elements since they both can be easily manipulated to obtain all possible logic functions. This simplification follows directly from Boolean theorems that we have discussed in the earlier chapters.

A close inspection of the truth table of these two functions, as described in Section 1.7, reveals that the NAND and NOR operators are duals of each other. Recall also from Chapter 1 that the dual of a Boolean expression is obtained by replacing every OR with AND, AND with OR, 0 with 1, and 1 with 0. Six of these dual properties are listed as follows:

| NAND                                                      | NOR                                                |

|-----------------------------------------------------------|----------------------------------------------------|

| $\overline{1. \ a \cdot 0} = 1$                           | $\overline{a+1}=0$                                 |

| $2. \ \overline{a \cdot 1} = \overline{a}$                | $\overline{a+0}=\bar{a}$                           |

| $3. \ \overline{a \cdot a} = \bar{a}$                     | $\overline{a+a}=\bar{a}$                           |

| $4. \ \overline{a \cdot b} = \overline{a} + \overline{b}$ | $\overline{a+b} = \overline{a} \cdot \overline{b}$ |

| $5. \ \overline{a \cdot b} = a + b$                       | $\overline{a+\bar{b}}=a\cdot b$                    |

| $6. \ \overline{a \cdot b} = a \cdot b$                   | $\overline{a+b}=a+b$                               |

|                                                           |                                                    |

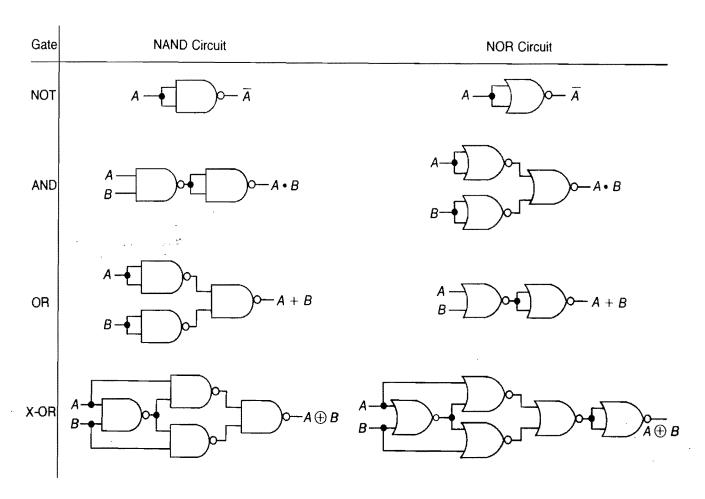

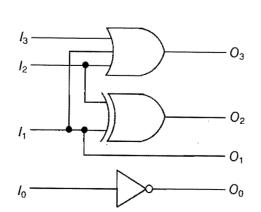

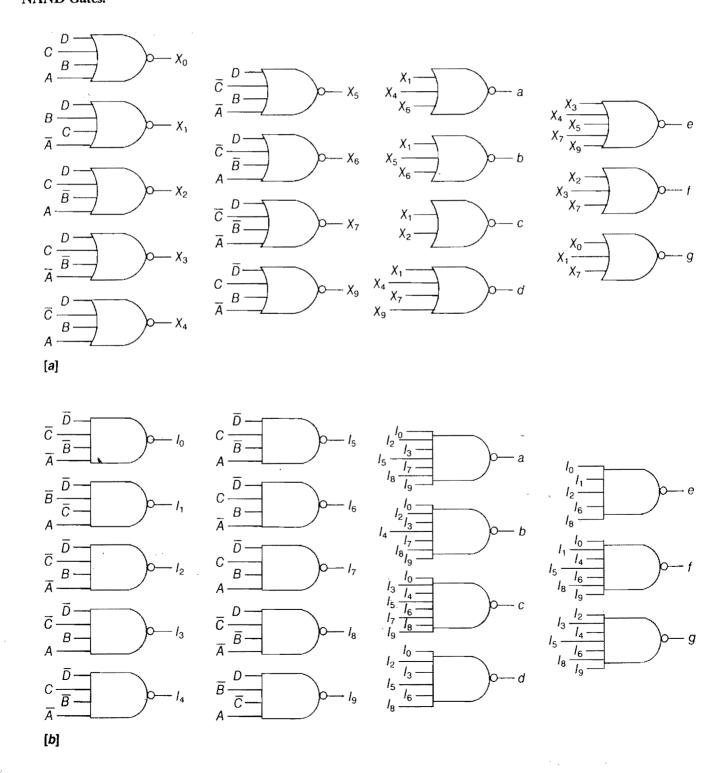

All of the logic functions may be generated using these properties of NAND and NOR logic. The corresponding NAND and NOR logic circuits for various functions are shown in Figure 4.1.

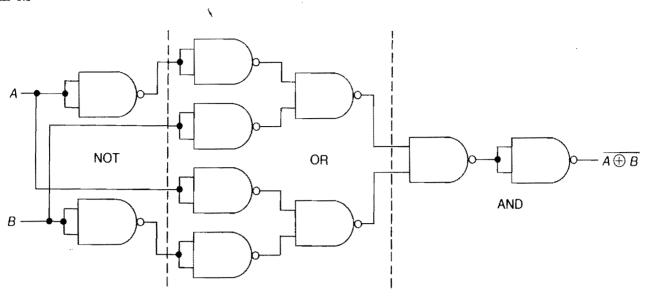

The circuits of Figure 4.1 show how NAND and NOR gates may be cascaded to form each of the logic functions NOT, AND, OR, and X-OR. Since either NANDs or NORs may be used to implement all of the logic operations, designers may prefer to use only NANDs or only NORs in order to decrease the inventory of spare parts. One of the methods by which to realize this is the brute force

FIGURE 4.1 Logic Functions Using NANDs and NORs.

scheme, where each of the logic operations of the Boolean function is replaced by the corresponding NAND/NOR circuit. Note, however, that restricting the number of inputs to the gates will not cause any major problem if proper use of the involution and DeMorgan's laws are made.

#### EXAMPLE 4.1

公本書を行っていたないと

#### **SOLUTION**

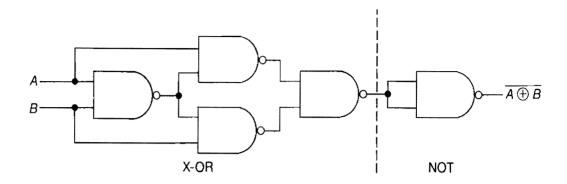

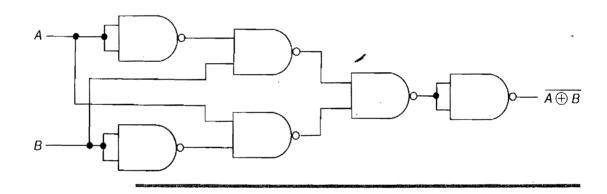

Implement  $\overline{A \oplus B}$  using only NAND gates.

There are two different ways to implement this function: (a) using NAND equivalents of an X-OR gate and of a NOT gate, and (b) using the NAND equivalents of either the SOP or the POS terms.

- a. The first possibility results in the circuit of Figure 4.2.

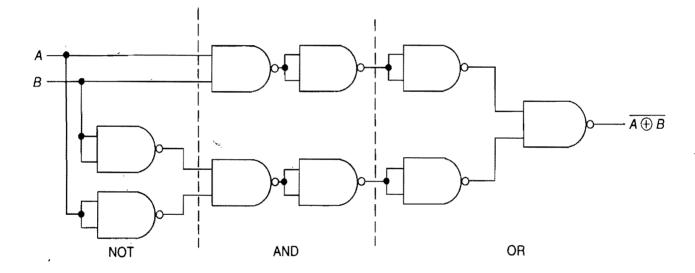

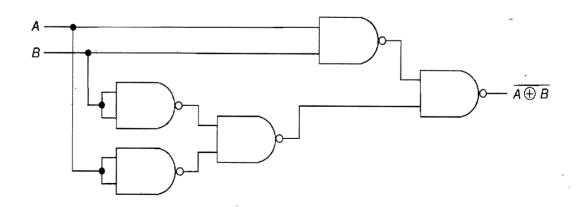

- b. Otherwise,  $\overline{A \oplus B}$  can be expressed in the SOP form as  $AB + \overline{AB}$ . Consequently, the circuit appears as in Figure 4.3. The circuit of Figure 4.3 can be reduced further since  $X = \overline{X}$ . Therefore, the circuit reduces to that of Figure 4.4. Note also that the function could be expressed in the POS form. Consequently,  $\overline{A \oplus B} = (A + \overline{B})(\overline{A} + B)$ , which leads to another variation of an X-NOR circuit as shown in Figure 4.5. The circuit of Figure 4.5

#### FIGURE 4.2

#### FIGURE 4.3

#### FIGURE 4.4

may be reduced further by making use of the law of involution. The resulting circuit is shown in Figure 4.6.

The first and the third forms, as shown in Figures 4.2 and 4.4, require five NAND gates each, and the fifth, as shown in Figure 4.6, requires a total of six NAND gates.

#### FIGURE 4.5

#### FIGURE 4.6

# 4.3 Function Implementation Using NANDs

It is quite easy to realize any SOP function using two levels of NAND gates. This method makes use of the fact that complementing a function twice returns the function to its original form. This result is achieved in two steps:

- 1. The function is complemented by complementing the ANDed terms and replacing the OR signs with AND signs.

- 2. The original function is then recovered by complementing the complement function.

It is not necessary to perform this operation each time a NAND realization is required. SOP forms always assume the same two-level NAND form.

The output of a NAND gate is also equivalent to the ORed output of the complements of the input. This statement follows directly from DeMorgan's theorem. Consequently, we are led to the follow-

ing set of rules for obtaining the output function of a multi-level NAND circuit:

- Rule 1. Consider the gate from which the output signal is derived as the first level, the preceding gate as the second level, and so on.

- Rule 2. In odd-numbered levels the NAND gates perform OR operations. All ungated input variables entering the odd-level NAND gates will appear complemented in the final expression.

- Rule 3. In even-numbered levels the NAND gates perform AND operations. All input variables entering the even-level NAND gates will appear uncomplemented in the final expression.

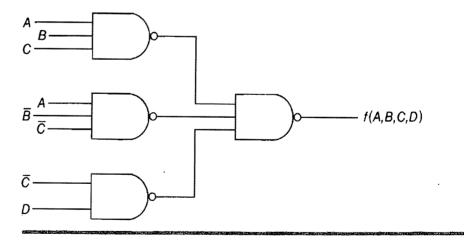

#### EXAMPLE 4.2

#### Using only NAND gates, implement the function given by

$$f(A,B,C,D) = ABC + A\overline{B}\overline{C} + \overline{C}D$$

#### **SOLUTION**

$$f = ABC + A\overline{B}\overline{C} + \overline{C}D$$

which yields

$$f = \overline{ABC} \cdot \overline{A\overline{B}\overline{C}} \cdot \overline{\overline{C}D}$$

The final circuit, therefore, is obtained as shown in Figure 4.7. The circuit requires three three-input NAND gates and one two-input NAND gate provided B and C inputs are also available in the complemented form.

#### FIGURE 4.7

# 4.4 Function Implementation Using NORs

The implementation of an SOP function using only NOR gates is possible only if the function is first converted to the equivalent POS form. The process includes the following steps:

1. Plot the function on a K-map and obtain the complemented function by grouping all zeros.

- 2. Expand each of the ANDed terms by using DeMorgan's theorem.

- 3. Complement the whole Boolean expression.

NOR realizations of SOP functions always have the same two-level structure. Steps 1 through 3 should be followed until the designer is confident of the result.

DeMorgan's theorem may be used to interpret the NOR operation as well. The output of the NOR gate is equivalent to the ANDed output of the complements of the inputs. Rules for the interpretation of multi-level NOR circuits are listed as follows:

Rule 1. Consider the gate from which the output signal is derived as the first level, the preceding gate as the second level, and so on.

Rule 2. In odd-numbered levels the NOR gates perform AND operations. All ungated input variables entering the odd-level NOR gates will appear complemented in the final expression.

Rule 3. In even-numbered levels the NOR gates perform OR operations. Input variables entering the even-level NOR gates will appear uncomplemented in the final Boolean expression.

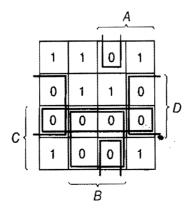

#### EXAMPLE 4.3

Using only NOR gates, implement the function given by

$$f(A,B,C,D) = \sum m(0,2,4,5,8,10,13)$$

#### **SOLUTION**

The minterms are plotted in a four-variable K-map and the corresponding zeros are grouped as shown in Figure 4.8. This gives

$$\overline{f} = CD + BC + \overline{B}D + AB\overline{D}

= \overline{C} + \overline{D} + \overline{B} + \overline{C} + \overline{B} + \overline{D} + \overline{A} + \overline{B} + D$$

Therefore,

$$f = \overline{\overline{C} + \overline{D}} + \overline{\overline{B} + \overline{C}} + \overline{B} + \overline{D} + \overline{A} + \overline{B} + D$$

#### FIGURE 4.8

The equivalent NOR circuit, therefore, may be obtained as shown in Figure 4.9. It requires three two-input NOR gates, one three-input NOR gate,

and one four-input NOR gate provided the inputs are also available in the complemented form.

#### FIGURE 4.9

#### EXAMPLE 4.4

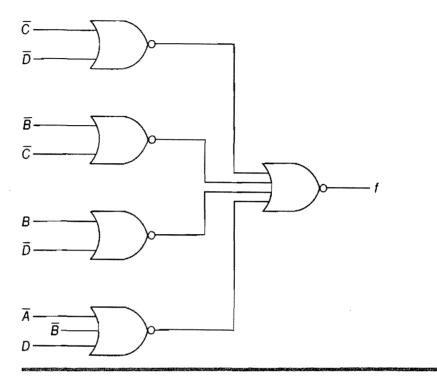

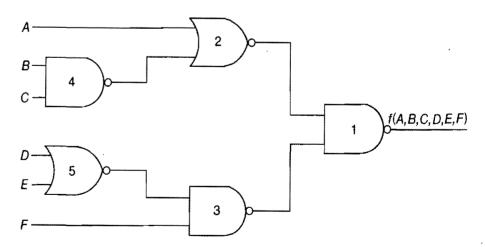

Write the output expression for the multi-level circuit shown in Figure 4.10.

#### **SOLUTION**

#### FIGURE 4.10

This is a three-level circuit. Therefore, the involved operations may be summarized as follows:

- a. Gate 1 performs the OR operation;

- **b.** Gate 2 performs the OR operation, and A must appear uncomplemented;

- **c.** Gate 3 performs the AND operation, and *F* must appear uncomplemented;

- **d.** Gate 4 performs the OR operation, and both B and C must appear complemented;

- e. Gate 5 performs the AND operation, and both D and E must appear complemented.

Therefore,

$$f(A,B,C,D) = [(\overline{D} \cdot \overline{E}) \cdot F] + [A + (\overline{B} + \overline{C})] = \overline{D}\overline{E}F + A + \overline{B} + \overline{C}$$

Function output expressions may also be determined by starting at the inputs and making repeated use of DeMorgan's theorem. This latter technique is best when there is a mix of NOR and NAND gates in the circuit.

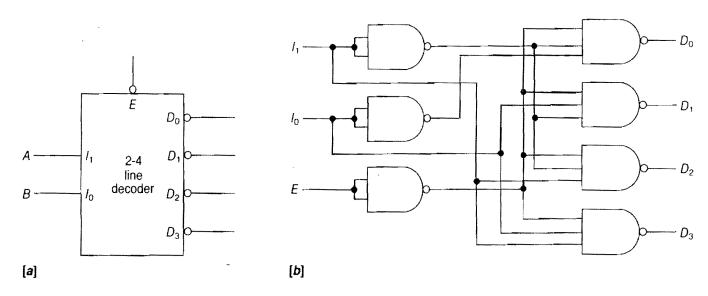

# 4.5 Function Implementation Using MUXs

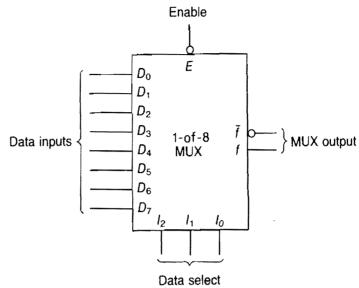

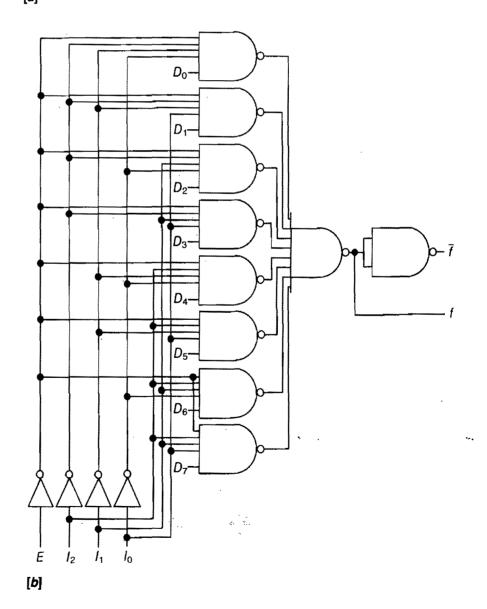

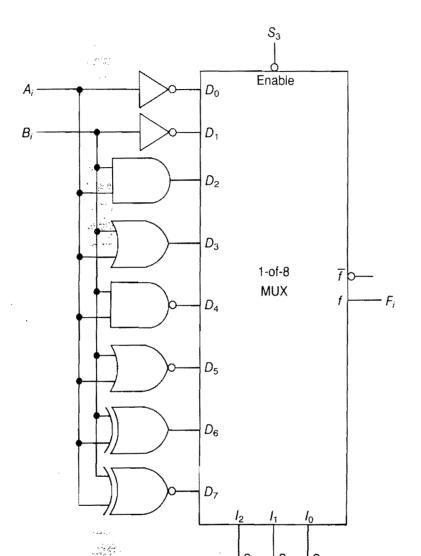

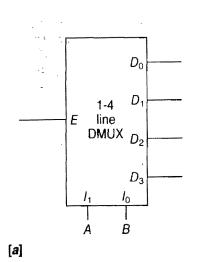

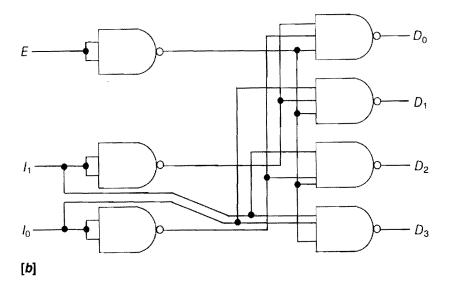

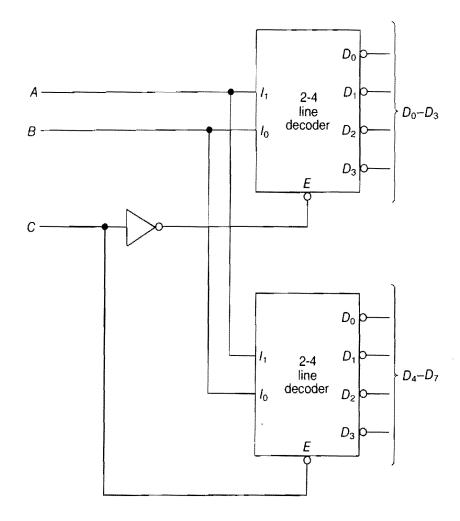

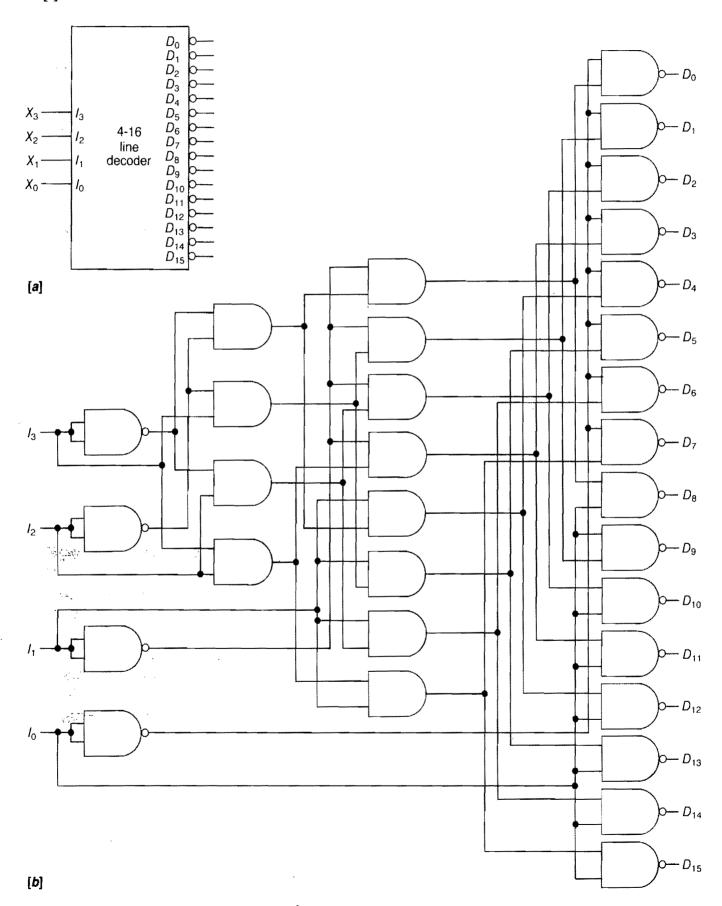

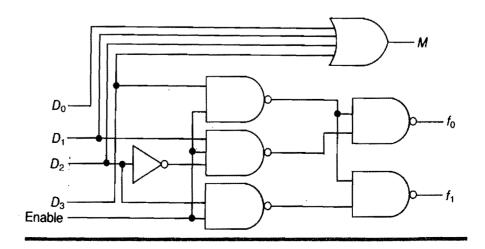

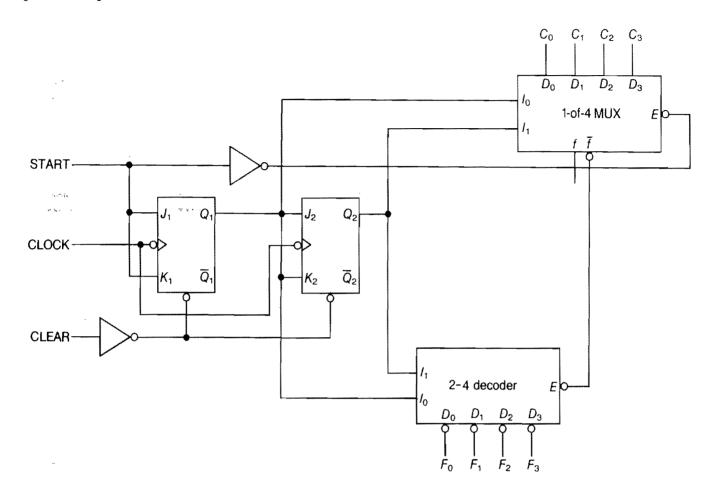

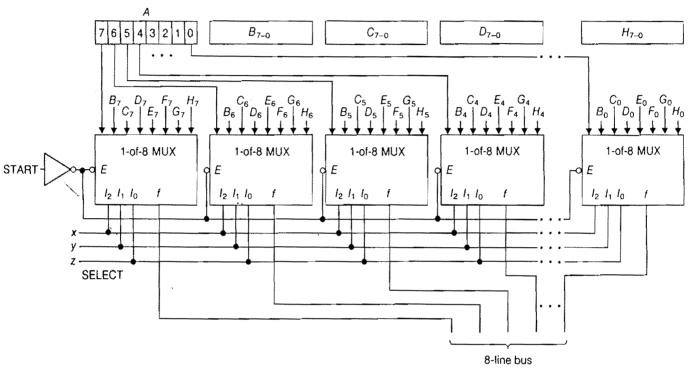

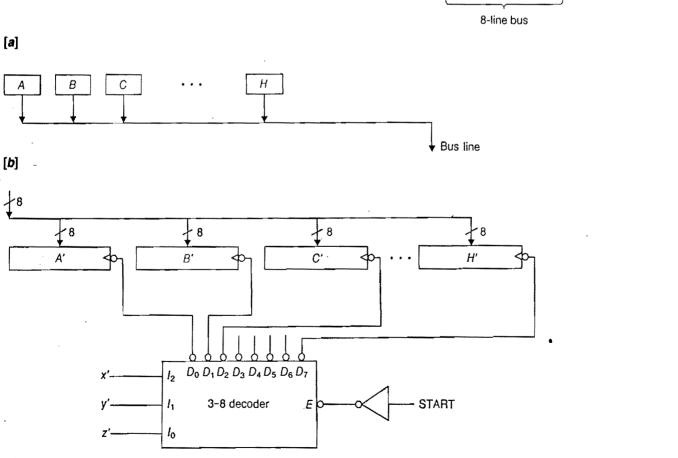

A multiplexer (MUX), known also as a data selector, is a combinational network that has up to  $2^n$  data inputs, n control inputs, and an output line. Commercial MUXs are limited to values of n of 1 through 4. An additional input is available that allows cascading of multiplexers to obtain higher-order devices. The MUX allows the selection of one of the  $2^n$  data inputs as the device output. This selection is made by the control lines. A block diagram of a MUX with eight data input lines,  $D_0$ ,  $D_1$ ,  $D_2$ ,  $D_3$ ,  $D_4$ ,  $D_5$ ,  $D_6$ , and  $D_7$ , is shown in Figure 4.11[a]. Most MUXs are provided with at least two additional lines: f for the complemented output and E for enabling the device. The internal circuit configuration of the corresponding MUX is shown in Figure 4.11[b]. For every  $2^n$  inputs the MUX has exactly n control lines. By applying appropriate signals to the control lines, any one of the data lines may be selected. For example, when  $I_2I_1I_0$ = 011, the  $D_3$  input is routed to the output provided E = 0. Note that whenever E = 1, the MUX is completely disabled; that is, regardless of the control variables or the data inputs, the output is 0. The enable input allows several of these devices to be cascaded together.

A MUX with  $2^n$  input lines and n selection lines (such a device is also referred to as a 1-of- $2^n$  MUX) may be wired to realize any Boolean function of n + 1 variables. This fact will be illustrated by implementing the function  $f(A,B,C,D) = \sum m(0,2,4,5,6,8,10,13)$  using a 1-of-8 MUX. A 1-of-8 MUX has three control inputs where all but any one of the input variables may be entered. For example, we may consider A, B, and C inputs as the three control inputs,  $I_2$ ,  $I_1$ , and  $I_0$ , respectively. The technique, therefore, consists of determining the function output in terms of the fourth input, D, for every possible combination of the control inputs. The values so obtained are then entered at the respective data inputs of the MUX. The truth table for the said function may then be reorganized as shown

FIGURE 4.11 Eight-Input MUX: [a] Block Diagram and [b] Circuit.

[a]

in Figure 4.12. The entries under the f(D) column are determined by comparing the entries of the column D with that of the column f. For any combination of A, B, and C, the following are true:

- 1. If f = 1 irrespective of D, then f(D) = 1.

- 2. If f = 0 irrespective of D, then f(D) = 0.

- 3. If f = x when D = x, then f(D) = D.

- 4. If  $f = \bar{x}$  when D = x, then  $f(D) = \bar{D}$ .

FIGURE 4.12 Truth Table for  $f(A,B,C,D) = \sum m(0,2,4,5,6,8,10,13)$ .

| Α | В | C | D | f | f (D)    |     |     |

|---|---|---|---|---|----------|-----|-----|

| 0 | 0 | 0 | 0 | 1 | 7        | 0   | D   |

|   |   |   | 1 | 0 | D        | 1   | ,   |

| 0 | 0 | 1 | 0 | 1 | D        | 0   | 0   |

|   | _ |   | 1 | 0 | U        | ó   |     |

| 0 | 1 | 0 | 0 | 1 | 1        | ١   | D D |

|   |   |   | 1 | 1 | ı        | 0   | 12  |

| 0 | 1 | 1 | 0 | 1 | D        | 1   | D   |

|   |   |   | 1 | 0 | <i>D</i> | 6   | ,   |

| 1 | 0 | 0 | 0 | 1 | Đ        | 0   | 0   |

|   |   |   | 1 | 0 | U        | 0   |     |

| 1 | 0 | 1 | 0 | 1 | D        | 0   | Q   |

|   |   |   | 1 | 0 | U        | 0   | ,   |

| 1 | 1 | 0 | 0 | 0 | D        | 1.1 | 1   |

|   |   |   | 1 | 1 |          | ]   | 1   |

| 1 | 1 | 1 | 0 | 0 | 0        | 4   | ı   |

|   |   |   | 1 | 0 |          | 1   | 1   |

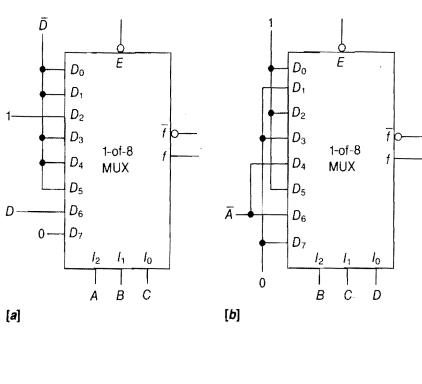

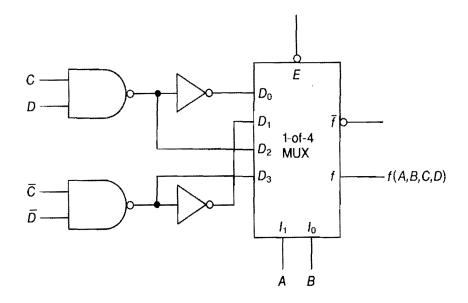

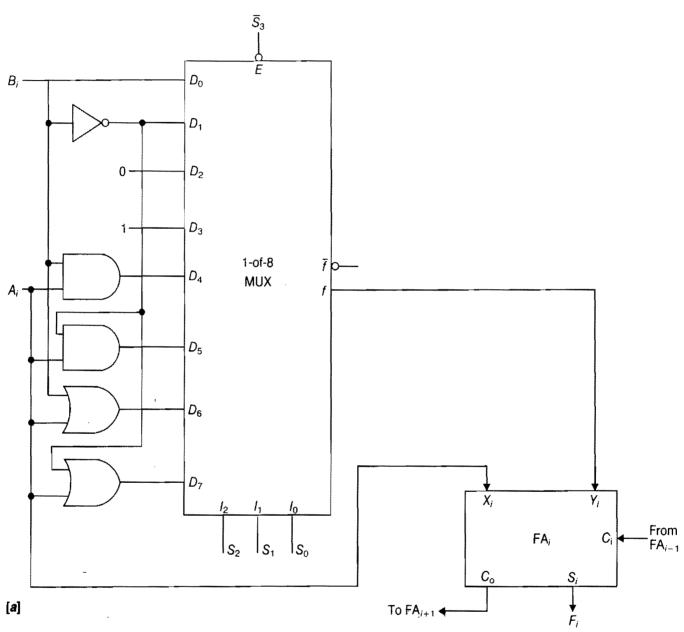

The function, therefore, is implemented as shown in Figure 4.13[a]. The eight values of f(D) are fed respectively into data inputs  $D_0$  through  $D_7$ . Consequently, for any combination of the three control inputs, f(D) would actually appear at the MUX output. The implementations of the same function for the other three combinations of the control inputs—B, C, and D; A, C, and D; and A, B, and D—can also be obtained in like manner. The corresponding MUX configurations are shown in Figures 4.13[b-d]. The designer might even change the order of the control inputs, resulting in a total of 24 different circuit configurations. In addition, if one of the control variables is available only in complemented form, the variable may be used without inverting and the inputs rearranged accordingly (see Problem 3b).

It is quite obvious that the use of MUXs provides the designer with numerous choices. Consequently, it is necessary to consider each of the solutions to determine which is the optimum. In Figure

FIGURE 4.13 MUX Implementation of f(A,B,C,D)=  $\sum m(0,2,4-6,8,10,13)$ : [a]  $I_2I_1I_0$ = ABC, [b]  $I_2I_1I_0$  = BCD, [c]  $I_2I_1I_0$ = ACD, and [d]  $I_2I_1I_0$  = ABD.

4.13[a],  $\overline{D}$  is seen to be tied to five of the data inputs. The gate that provides  $\overline{D}$  must then have a fan-out of at least five. If we limit ourselves to the four choices of Figure 4.13, it is apparent that Figure 4.13[d] provides the most preferable circuit, because the C variable needs to be fed directly to only two of the data inputs. Example 4.5 illustrates the mechanism of obtaining a multi-level multiplexer circuit.

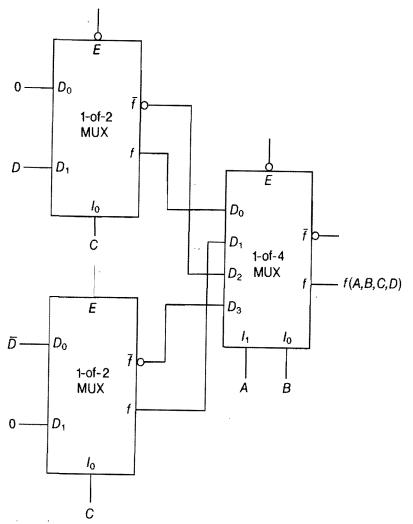

#### EXAMPLE 4.5

Implement the function

$$f(A,B,C,D_1) = \sum m(3,4,8-10,13-15)$$

a. by using a 1-of-4 MUX and a few assorted gates,

b. by using 1-of-2 and 1-of-4 MUXs in two levels.

#### FIGURE 4.14

#### **SOLUTION**

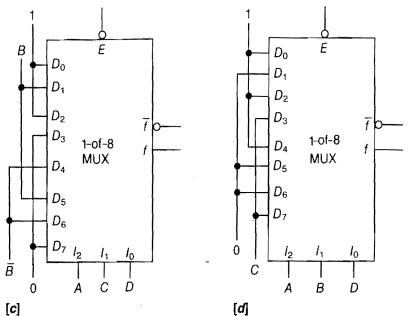

a. The function may be expressed in the SOP form and then regrouped as

$$\begin{split} f(A,B,C,D) &= \overline{A}\overline{B}CD + \overline{A}B\overline{C}\overline{D} + A\overline{B}\overline{C}\overline{D} + A\overline{B}\overline{C}D + A\overline{B}C\overline{D} \\ &+ AB\overline{C}D + ABC\overline{D} + ABCD \\ &= \overline{A}\overline{B}(CD) + \overline{A}B(\overline{C}\overline{D}) + A\overline{B}(\overline{C}\overline{D} + \overline{C}D + C\overline{D}) \\ &+ AB(\overline{C}D + C\overline{D} + CD) \\ &= \overline{A}\overline{B}(CD) + \overline{A}B(\overline{C}\overline{D}) + A\overline{B}(\overline{C} + \overline{D}) + AB(C + D) \end{split}$$

Accordingly, the resultant circuit is obtained as shown in Figure 4.14.

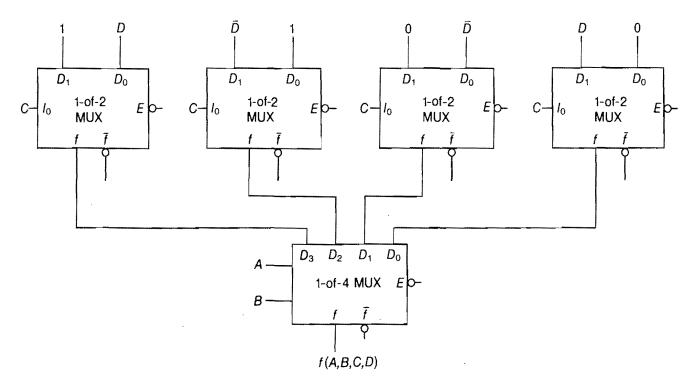

b. Also,

$$f(A,B,C,D) = \overline{AB}[\overline{C}(0) + C(D)] + \overline{AB}[\overline{C}(\overline{D}) + C(0)] + A\overline{B}[\overline{C}(1) + C(\overline{D})] + AB[\overline{C}(D) + C(1)]$$

This implies that a two-level MUX circuit would be able to generate this function. The first level of a 1-of-2 MUX essentially eliminates the need for discrete gates. The resultant circuit is obtained as shown in Figure 4.15. However it can be shown that

$$\overline{C}(0) + C(\overline{D}) = \overline{C}(1) + C(\overline{D})$$

and

$$\overline{C(\overline{D}) + C(0)} = \overline{C}(D) + C(1)$$

Note also that the MUXs usually are provided with an additional output for providing the complemented result. Consequently, two of the first-level 1-of-2 MUXs may be removed. The resulting reduced multi-level MUX circuit is obtained as shown in Figure 4.16.

#### **FIGURE 4.15**

#### **FIGURE 4.16**

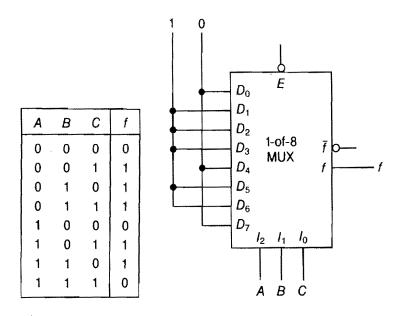

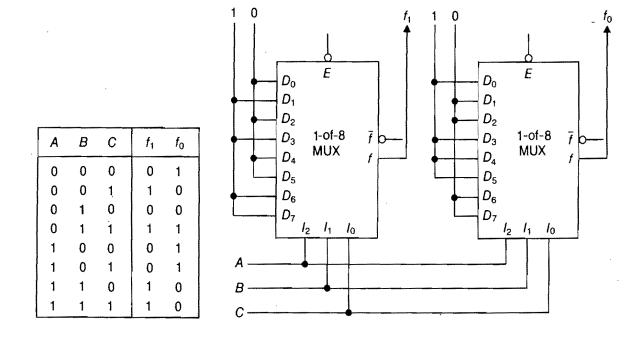

MUXs can also be applied in a more brute force manner. This technique involves 1-of- $2^n$  MUXs for functions of n variables, while Example 4.5 used 1-of- $2^{n-1}$  MUXs to implement a function. The function values from a function's truth table are transformed directly to the inputs of the MUX. The n variables are treated as control inputs to the MUX. Figure 4.17 shows the truth table for a three-variable function and the corresponding 1-of-8 MUX implementation. For two functions of the same variables, two MUXs may be used as shown in Figure 4.18.

FIGURE 4.17 Realization of  $f(A,B,C) = \sum m(1-3,5,6)$  Using 1-of-8 MUX.

FIGURE 4.18 Realization of  $f_1(A,B,C) = \sum m(1,3,6,7)$  and  $f_0(A,B,C) = \sum m(0,3-5)$  Using Two 1-of-8 MUXs.

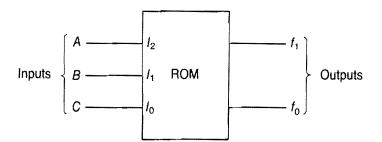

The technique just discussed is not as efficient as the one before in terms of MUX size, but it is certainly easy to implement and is a good way to introduce another device that may be used to implement combinational logic functions. If we put the circuit implementation of Figure 4.18 in a box, we could show the circuit symbolically as illustrated in Figure 4.19. Such a representation is called a black-box representation since the user is not required to know about the details of the internal logic. Not knowing what is in the box in Figure 4.19, we might explain the circuit action by simply saying that ABC forms an address, and  $f_1$  and  $f_0$  are what is stored there. This is precisely the explanation of the operation of a device with which we can implement multiple functions of a set of variables. This device is called a read-only memory (ROM). It can be considered as a set of storage cells with every cell having a value for each of the multiple functions. These ROMs can be programmed (1s and 0s applied to the inputs of each of the function's MUX inputs) by the manufacturer or by the designer if he or she has available blank ROM chips and an appropriate programmer. The information stored in the ROM remains there permanently. The ROM equivalent of the logic of Figure 4.18 is shown by the block diagram of Figure 4.19. When power is applied,  $f_1$  and  $f_0$  have the same values as before power was removed.

FIGURE 4.19 Black-Box Representation of the Circuit of Figure 4.18.

ROMs come in many sizes. The sizes are determined by the number of storage cells (corresponding to the number of MUX inputs) and the number of bits stored in each cell (the number of functions that can be implemented). In Figures 4.17 and 4.18 there are three variables that allow addressing  $2^3$  storage cells in our MUX-implemented ROM. In general, n variables would require  $2^n$  storage cells and correspond to n address lines. Each storage cell would have one bit (1 or 0) for each function of the n variables.

Commercially available ROMs come in many sizes. They may be listed as  $2K \times 1$  or  $2K \times 8$ , meaning 2048 storage locations one bit wide in the first case and 2048 storage locations eight bits wide in the second case. The first would allow implementing a function of up to 11 variables, the second up to eight functions of 11 variables. The designer selects a ROM of adequate size to implement the desired function.

The following section discusses ROMs in more detail. For most function generation applications, ROMs can be visualized as a set of MUXs—one for each function of the input variables (addresses).

#### EXAMPLE 4.6

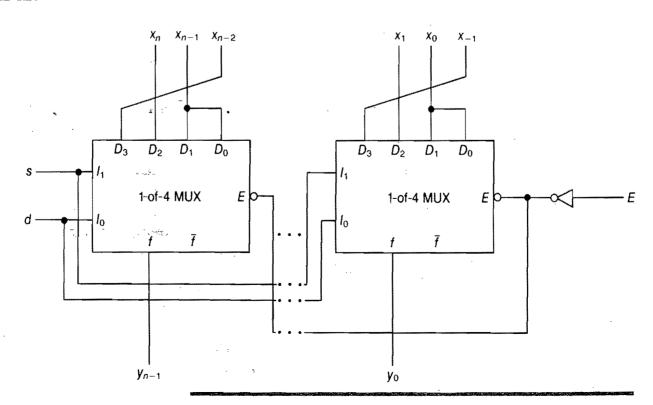

# Obtain a multi-bit shifter (see Example 2.4 for definition) that has an (n + 2)-bit input, x, an n-bit output, y, and three control inputs: s, d, and E. You may use only MUXs for the design.

#### **SOLUTION**

The characteristics of the shifter could be summarized as follows:

$$y_i = \begin{cases} x_{i-1} & \text{if } d = 1, s = 1, \text{ and } E = 1 \text{ (left-shift)} \\ x_{i+1} & \text{if } d = 0, s = 1, \text{ and } E = 1 \text{ (right-shift)} \\ x_i & \text{if } s = 0 \text{ and } E = 1 \text{ (no-shift)} \\ 0 & \text{if } E = 0 \end{cases}$$

where  $0 \le i \le n - 1$ .

A 1-of 4 MUX could be used corresponding to each bit of y. The variables s and d can be fed as its selectors, and E as the enable input. The inputs  $x_i$ ,  $x_{i-1}$ , and  $x_{i+1}$  could be introduced at the MUX data inputs, and they could be suitably selected as the shifter output. The multi-bit shifter is obtained accordingly as shown in Figure 4.20. Whenever E=0, the MUXs are disabled and the output becomes zero.

#### FIGURE 4.20

## 4.6 Function Implementation Using ROMs

A read-only memory (ROM), as the name implies, is intended to hold fixed information that can only be read, not altered. The primary use of the ROM is to provide a means for storing binary information. The storing is done during the fabrication of the ROM and may not be altered without undergoing a significantly involved process. The same is true for a combinational network that has been designed, fabricated, tested, and encapsulated with only the inputs and the outputs available. The ROM has become an important part of many digital systems because of the ease with which complex functions such as code conversion, program storage, and character generation can be implemented. The chip count of circuits, for which the access time of the ROM is not a restriction, may be greatly reduced by using ROMs.

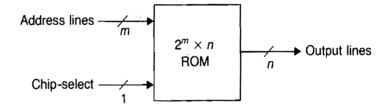

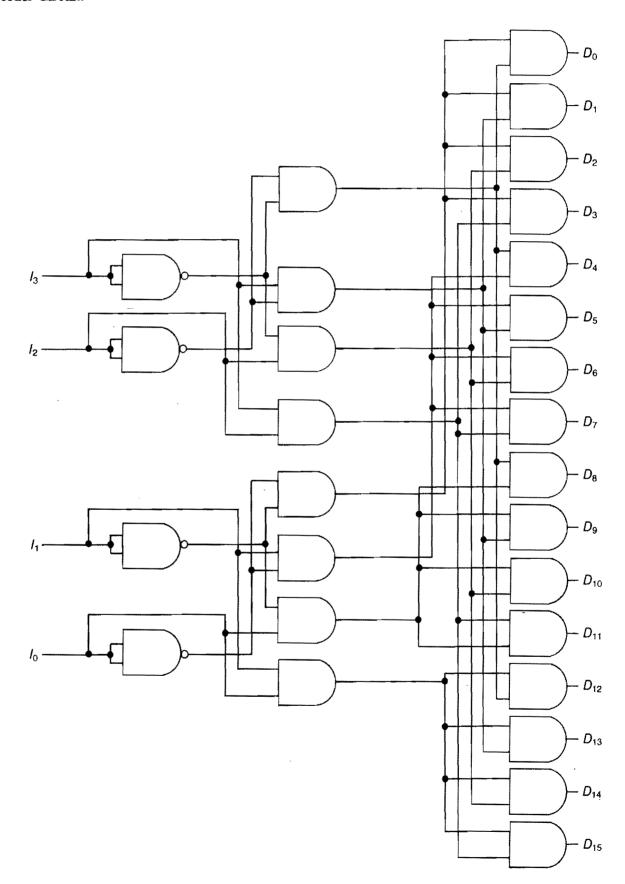

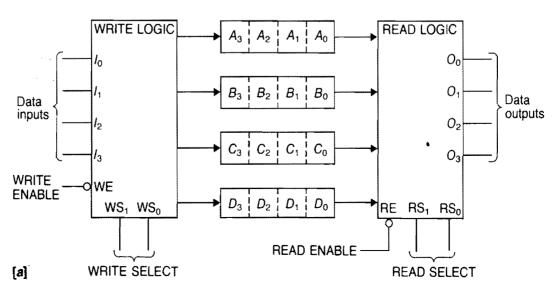

A  $2^m \times n$  ROM is an array of memory cells organized into  $2^m$  words of n bits each, as shown by the block diagram of Figure 4.21. Such a ROM is accessed by means of m address lines and the stored information is retrieved via a total of n data-out lines, one for each bit of the word. The ROM corresponds to a combinational network with n outputs, where each of the outputs is associated with up to  $2^m$  different minterms. A ROM may be provided with one or more chip-select lines to permit cascading smaller ROMs to form a ROM with more words (allowing implementation of functions of more variables).

FIGURE 4.21 Block Diagram of a ROM.

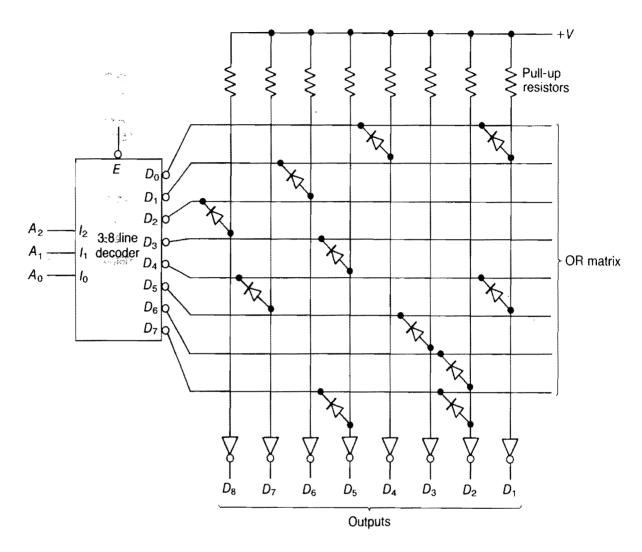

As indicated in the previous section, a ROM is a combinational circuit. A ROM can be implemented by using only diodes, bipolar transistors, or MOS transistors. Although the diode matrix ROM no longer represents the current ROM technology, it serves as a simple model to show the basic concept. Figure 4.22 shows a simple diode ROM, where the row and column lines are interconnected via diodes placed at the respective intersections. The absence or presence of a diode indicates that the corresponding row and column intersection is programmed with a 1 or a 0. If the output is buffered with inverters, the converse is true. The output for the *t*th address depends on the ORing diodes connected to that line. For example, if  $A_2A_1A_0 = 100$ , the output will be  $D_8D_7 \dots D_1 = 01000001$ . For  $A_2A_1A_0 = 100$  input, a low is produced on the decoder output numbered 4. This low and the pull-up resistor forward biases each of the diodes connected to this row and pulls down

FIGURE 4.22  $8 \times 8$  Diode ROM.

the corresponding column outputs to a low. In the absence of a diode, a high is maintained at the output due to the pull-up resistors. The capacity of a ROM usually is quoted as the number of possible intersections in the matrix, for example,  $8 \times 8 = 64$  bits = (1/16)K bits in this case. A total of 1024 intersections is usually referred to as 1K bits. Examples 4.7 and 4.8 illustrate the use of diode ROMs in combinational problems.

#### EXAMPLE 4.7

#### **SOLUTION**

Use ROM to realize the implementation of the integer function

4.

7.7.7.35

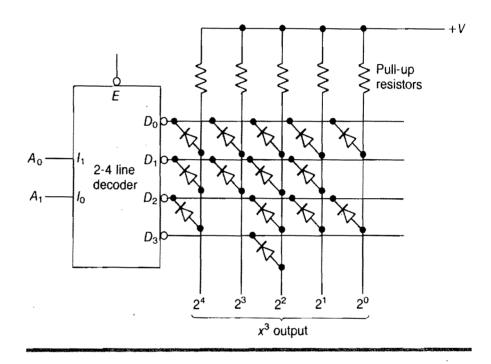

$$f(x) = x^3 \qquad \text{for } 0 \le x \le 3$$

The function truth table is obtained as shown in Figure 4.23. A 2-4 line decoder would be sufficient to decode the numbers 0, 1, 2, and 3, and it is apparent that a maximum of five output lines are needed to represent the cube of the largest number. The two select lines,  $A_0$  and  $A_1$ , can be used to select any one of these four outputs.

#### **FIGURE 4.23**

| х | f(x) | f(x) in Binary |

|---|------|----------------|

| 0 | 0    | 00000          |

| 1 | 1    | 00001          |

| 2 | 8    | 01000          |

| 3 | 27   | 11011          |

The resultant diode matrix implementation of  $x^3$  ROM, therefore, is obtained as shown in Figure 4.24.

#### FIGURE 4.24

#### EXAMPLE 4.8

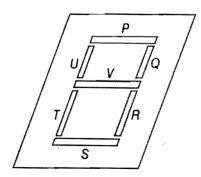

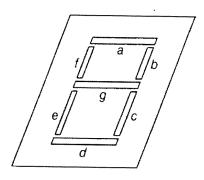

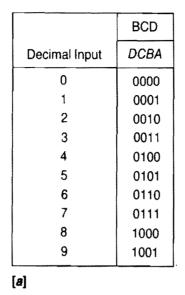

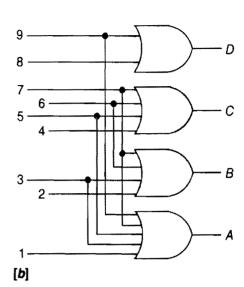

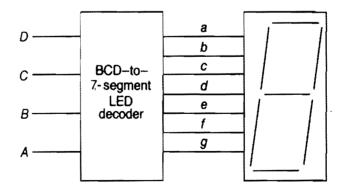

# Using a minimal ROM implementation, design a seven-segment-to-BCD code converter. The seven-segment display device consists of seven LEDs, as shown in Figure 4.25, arranged in such a way that they could be used for displaying data.

#### **SOLUTION**

#### **FIGURE 4.25**

The seven-segment-to-BCD truth table is obtained as shown in Figure 4.26. The input entries are selected in such a way that the output would be displayed only if the corresponding LED segments are lighted. For example, when all of the seven segments are turned on, the display will be an 8.

**FIGURE 4.26**

|   | Inputs |   |     |   |   |   |   | Out | outs |   |

|---|--------|---|-----|---|---|---|---|-----|------|---|

| P | Q      | R | s   | Τ | U | V | D | С   | В    | Α |

| 1 | 1      | 1 | 1   | 1 | 1 | 0 | 0 | 0   | 0    | 0 |

| 0 | 1      | 1 | 0 - | 0 | 0 | 0 | 0 | 0   | 0    | 1 |

| 1 | 1      | 0 | 1   | 1 | 0 | 1 | 0 | 0   | 1    | 0 |

| 1 | 1      | 1 | 1   | 0 | 0 | 1 | 0 | 0   | 1    | 1 |

| 0 | 1      | 1 | 0   | 0 | 1 | 1 | 0 | 1   | 0    | 0 |

| 1 | 0      | 1 | 1   | 0 | 1 | 1 | 0 | 1   | 0    | 1 |

| 0 | 0      | 1 | 1   | 1 | 1 | 1 | 0 | 1   | 1    | 0 |

| 1 | 1      | 1 | 0   | 0 | 0 | 0 | 0 | 1   | 1    | 1 |

| 1 | 1      | 1 | 1   | 1 | 1 | 1 | 1 | 0   | 0    | 0 |

| 1 | 1      | 1 | 0   | 0 | 1 | 1 | 1 | 0   | 0    | 1 |

#### FIGURE 4.27

| Р | Q | R | S | T | Z | Υ | Χ |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | Ō |

Note, however, that there could be up to two choices for displaying a 1: either U and T or Q and R.

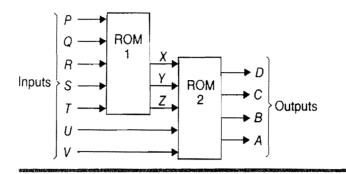

A direct implementation of this table requires a  $2^7 \times 4 = 512$ -bit ROM. Note that the partitioned table (with inputs P, Q, R, S, and T), as shown in Figure 4.27, would require only seven of the possible  $2^5 = 32$  combinations. This situation suggests that a reasonable improvement is possible if the designer is willing to cascade at least two smaller ROMs. One of these ROMs should have at the least three outputs—Z, Y, and X—since  $2^3 > 7$ . The output of the first ROM—Z, Y, and X—can be fed along with the other two inputs—U and V—into the second ROM. However, care must be taken in organizing the second ROM so that its output becomes equivalent to that of Figure 4.26. Accordingly, the compressed truth table of Figure 4.28 is obtained such that it incorporates the same logic as that of Figure 4.26. The seven inputs have now been replaced by only five inputs, where the first three are functions of P, Q, R, S, and T and the other two are U and V themselves.

Outputs Z, Y, and X are realizable using a 96-bit (3  $\times$  2<sup>5</sup>) ROM. A second ROM can be used where Z, Y, X, U, and V are the inputs. The second ROM size is 4  $\times$  2<sup>5</sup> = 128 bits. Therefore, the total ROM size requirement is reduced to only 96 + 128 = 224 bits. This solution reduces

FIGURE 4.28

| Z | Y | Х | U | V | D | С | В  | Α |

|---|---|---|---|---|---|---|----|---|

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0  | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0  | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1  | 0 |

| 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1  | 1 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | Ó. | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0  | 1 |

| 1 | 0 | i | 1 | 1 | 0 | 1 | 1  | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1  | 1 |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0  | 0 |

| 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0  | 1 |

the ROM size to about half of the original. The ROM implementation of the circuit, therefore, is given by the multi-level circuit of Figure 4.29.

#### **FIGURE 4.29**

Although the diode matrix serves to demonstrate the ROM concept, ROMs are presently manufactured using bipolar and MOS transistors, as shown in Figure 4.30. The presence of a connection from a row line to either a transistor base or a MOSFET gate represents a logic 0, and the absence of such a connection represents a logic 1. For economical reasons MOS ROM is preferred to bipolar ROM for large numbers of bits. Access time for bipolar ROM, however, is much less than that of MOS ROM.

FIGURE 4.30 [a] Bipolar  $m \times n$  ROM and [b] MOS  $m \times n$  ROM.

## 4.7 Function Implementation Using PLAs and PALs

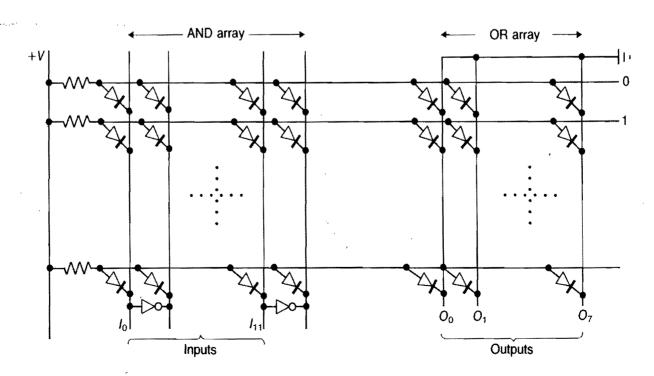

Examples 4.7 and 4.8 illustrated how a ROM may be used to implement SOP logic expressions. There is another aspect of the ROM that deserves attention, however. A ROM consists of a level of AND gates, which constitute the decoder part, followed by a second level of OR gates (made up of diodes or transistors), which constitute the encoder section. A ROM may be thought of as a programmable array of logic gates. With this array of AND and OR gates, every combination of minterms of the input variables (addresses) can be formed. This flexibility is costly in that, when implementing complex functions, not all minterms are necessary to realize a given expression. For example, a ROM that processes 12 variables requires a total of 4K byte (eight bits are called a byte) memory. For example, such an arrangement is needed for the Hollerith code conversion circuit that has up to 12 input variables, but has only 96 eight-bit output combinations of these variables. This situation implies that 4000 out of 4096 bytes will remain unused. Such waste can be eliminated by the use of a programmable logic array (PLA).

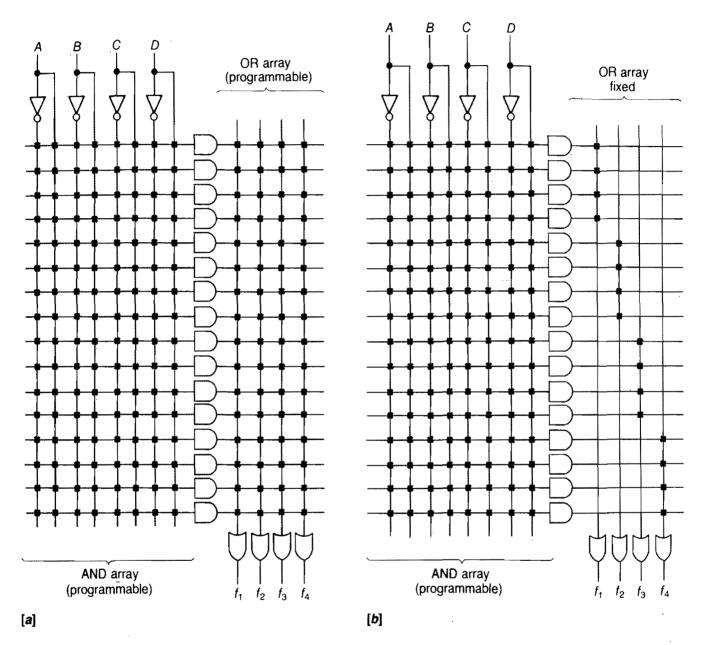

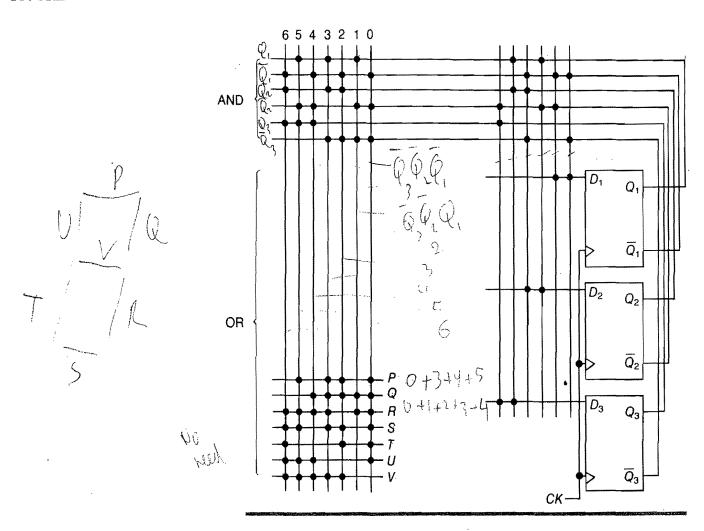

A PLA consists of an array of AND-OR logic along with *inverters* that may be programmed to realize the desired output. In essence a PLA may be regarded as being made up of two separate ROMs: an AND ROM and an OR ROM. A typical PLA configuration is shown in Figure 4.31 in a 12 × 32 × 8 format. The circuit consists

FIGURE 4.31  $12 \times 32 \times 8$  PLA Using Diodes.

of an initial AND array, which can implement any one or more of the 32 product terms of up to 12 variables. The inclusion of an inverter with each input variable allows any minterm to be formed.

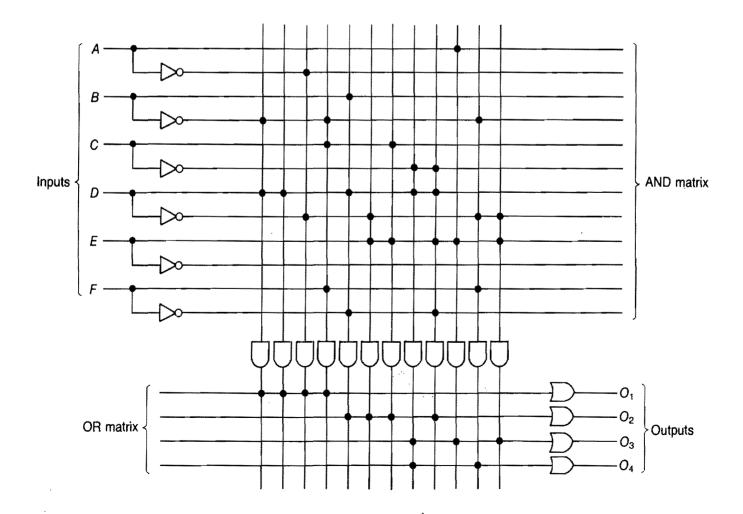

A PLA may be used as a Boolean function generator in much the same way as a ROM. As a simple example, Figure 4.32 shows a small PLA layout with six inputs, twelve product terms, and four outputs. The dots in the matrix of the top section can be thought of as AND inputs and those on the bottom part can be interpreted as OR inputs to generate the outputs. The output functions are easily determined as follows:

$$\begin{aligned} O_1 &= \overline{B}D + D + \overline{A}\overline{D} + \overline{B}CF = \overline{A} + D + \overline{B}CF \\ O_2 &= BD\overline{F} + \overline{D}E + CE + \overline{C}DE\overline{F} \\ O_3 &= \overline{C}D + AE + \overline{D}E \\ O_4 &= \overline{C}D + \overline{B}\overline{D}F \end{aligned}$$

FIGURE 4.32 PLA Implementation.

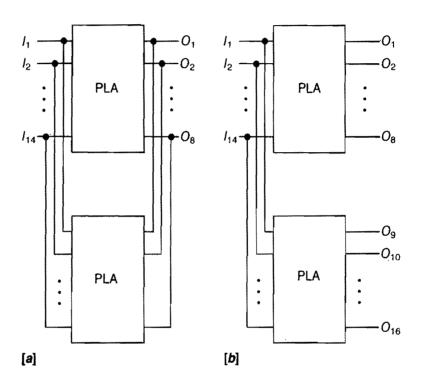

Larger numbers of product terms and/or outputs may be obtained when more than one PLA is cascaded. Some of these expansion schemes are shown in Figure 4.33. The product terms essentially are increased by tying the outputs in parallel. This configuration resembles the wiring of open-collector outputs. Correspondingly, an increase in the word size could be accomplished by unhooking the outputs.

FIGURE 4.33 PLA Expansion Scheme: [a] Product Term Expansion and [b] Output Expansion.

The designer must use care in choosing the minterms to be formed in the AND section of the PLA. In order to use PLAs optimally, it is necessary to have as many output functions as possible that have common minterms. It is not necessary for each function to be minimized; the goal is to minimize the total number of minterms required to implement the set of functions.

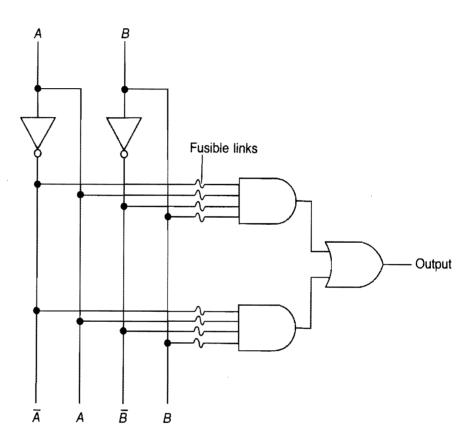

It would be appropriate now to discuss an additional programmable device known as programmable array logic (PAL). It also allows the systems engineer to design his or her "own chip" by fusible links to configure AND and OR gates to perform the desired logic functions. The PAL is basically a programmable AND array driving a fixed OR array. In comparison, both of the arrays of PLA are programmable, while the programmable version of ROM, known commonly as PROM (to be discussed in detail in Chapter 12), has a fixed AND matrix and programmable OR array.

In the PAL circuit, as shown in Figure 4.34, an AND array allows the designer to specify the product terms required and connect them to perform the required SOP logic functions. The PALs are available in a number of different part types, however, that vary the OR gate format. Specifying the OR gate connection, therefore, becomes a task of device selection rather than of programming.

FIGURE 4.34 Logic Diagram of a Simple PAL.

Consequently, PALs totally eliminate the need for a second matrix without any significant loss of flexibility.

In general PALs offer cost-effective capabilities for improving the effectiveness of existing logic designs by expediting and simplifying prototypes and board layouts. Figures 4.35[a-b] respectively show the PLA and PAL configurations of a four-input-four-output AND-OR circuit. The PLA provides the most flexibility for implementing logic functions since the designer is equipped with complete control over all inputs and outputs. However, this flexibility makes PLAs expensive and somewhat formidable to comprehend. In comparison, the PAL combines much of the flexibility of the PLA with the low cost and easy programmability of the PROM.

FIGURE 4.35 A Four-Input, Four-Output AND-OR Circuit Using [a] PLA and [b] PAL.

<sup>\*</sup> indicates a fusible link. Links are removed where no connection is desired.

### 4.8 Bridging Technique

The bridging technique is not so much a self-contained design algorithm as it is a way to bend the characteristics of a Boolean function that cannot be reduced further. If after using K-maps or the Q-M technique, the function is still large and unwieldy due to the minterms being logically separated, the function might be *bridged* by using known functions that exhibit similar patterns of logically sep-

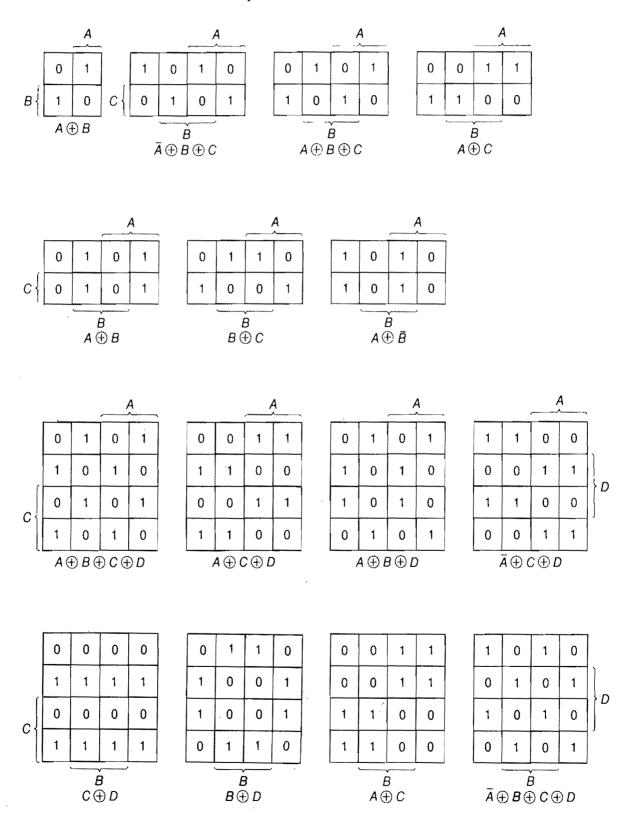

arated minterms. The X-OR function frequently is used in the bridging process.

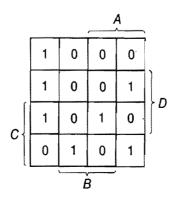

Consider the K-maps of several X-OR functions, shown in Figure 4.36. It is obvious that such K-maps are not reducible without the X-OR function. A close examination of these maps reveals that there are equal numbers of 1s and 0s on each half. In addition, the

FIGURE 4.36 Examples of Several X-OR Functions.

complement of the X-OR function may be obtained either by complementing the whole function or by complementing odd numbers of variables. An X-OR function can be changed to another equivalent X-OR function as long as either (a) an even number of variables have been complemented, or (b) the entire function and an odd number of variables have been complemented. For example,

$$A \oplus B \oplus C \oplus D = \overline{A} \oplus \overline{B} \oplus \overline{C} \oplus \overline{D} = A \oplus \overline{B} \oplus \overline{C} \oplus D$$

$$= A \oplus \overline{B} \oplus C \oplus \overline{D} = \overline{A \oplus \overline{B} \oplus C \oplus D}$$

The X-OR functions are often very useful in implementing functions that have logically isolated minterms.

As long as the function to be implemented bears the characteristic of an X-OR function, it can be realized using one or more X-OR gates. However, the problem becomes more difficult when the K-map closely resembles that of an X-OR function but is not one. The bridging technique then is used to connect the desired function and a closely resembling X-OR function. The technique consists of the following steps:

- 1. Match the function K-map, F, as closely as possible to a known X-OR K-map, f.

- 2. Realize the function F using bridging such that  $F = f \cdot X + Y$ , where X and Y are two separate functions of the same input variables. X and Y are determined by closely comparing K-maps of F and f.

Example 4.9 illustrates the idea behind the bridging scheme.

#### EXAMPLE 4.9

#### **SOLUTION**

Using X-OR and other assorted gates, implement the function

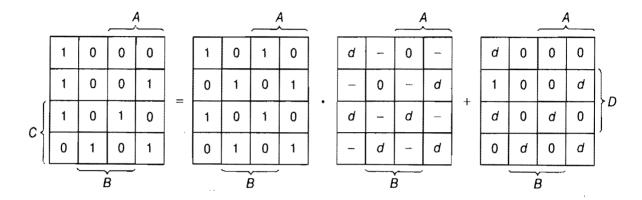

$$F(A,B,C,D) = \sum m(0,1,3,6,9,10,15)$$

The function K-map is obtained as shown in Figure 4.37. By comparing the K-map of Figure 4.37 with those of Figure 4.36, it would become obvious that the closest match occurs with  $f = \overline{A} \oplus B \oplus C \oplus D$ . However,

#### **FIGURE 4.37**

they are not exactly alike. They differ at three minterm locations: 1, 5, and 12. The two functions may be bridged, therefore, as shown in Figure 4.38. The bridging between the two functions F and f required that certain constraints, as listed in Figure 4.39, be met in determining X and Y functions. These constraints follow directly from the equation  $F = f \cdot X + Y$ .

#### FIGURE 4.38

FIGURE 4.39

| F | f | Х | Υ |

|---|---|---|---|

| 0 | 0 |   | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | - | 1 |

| 1 | 1 | ď | đ |

The d's in the table of Figure 4.39 indicate that either X or Y or both must equal 1. In other words, X and Y cannot simultaneously be 0 when F = f = 1. This use of d, however, permits many choices for the selection of X and Y. It can be seen that if all d's in X are set equal to 0, then F = Y, which is contrary to what is expected in bridging. When F = Y no bridging is needed. On the other hand, if all d's in X are set equal to 1, then

$$Y = \overline{A}\overline{B}\overline{C}D$$

$$X = \overline{B} + C$$

Therefore,

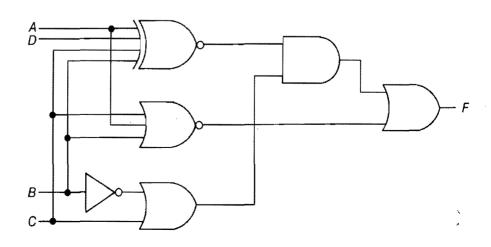

$$F = (\overline{A} \oplus B \oplus C \oplus D) \cdot (\overline{B} + C) + \overline{A}\overline{B}\overline{C}$$

The resultant circuit is obtained as shown in Figure 4.40. This bridged circuit is certainly better than the circuit that could be obtained by using only

FIGURE 4.40

a K-map. If a designer was limited to using only a K-map, the function would have reduced instead to

$$F(A,B,C,D) = \overline{A}\overline{B}\overline{C} + \overline{A}\overline{B}D + \overline{B}\overline{C}D + ABCD + \overline{A}BC\overline{D} + A\overline{B}C\overline{D}$$

The bridge scheme is very general and it does not have to involve only X-OR functions. This technique can be used for generating a complex function when a like function of the same variables already exists (see Problem 16).

#### 4.9 Summary

#### **Problems**

In this chapter various practical techniques were introduced for realizing combinational circuits. In particular, circuits using only NAND gates, only NOR gates, only MUXs, only ROMs, only PLAs, and only PALs were discussed. In addition, the bridging technique was introduced to handle functions that are otherwise not reducible.

- 1. Obtain the circuit for the following functions using only NAND gates:

- a.  $f(A,B,C,D) = \sum m(1,4,10,11,13,15)$

- b.  $f(A,B,C,D) = \sum m(1,3,4,9,10,13)$

- c.  $f(A,B,C,D) = \sum m(1,8-10,15)$

- d.  $f(A,B,C,D,E) = \sum m(1,3-7,11,14-17,22,24-27,30)$

- e.  $f(A,B,C,D,E) = \sum m(1,8-10,13-17,21,25-27,30,31)$

- 2. Obtain NOR circuits for the functions of Problem 1.

- 3. a. Use a single level of 1-of-8 MUXs and a few assorted gates (if needed) to obtain a combinational circuit for each of the functions of Problem 1.

- b. For each of your solutions, complement one variable and rearrange the inputs so that the function is still correct.

- 4. Using 1-of-4 MUXs, obtain a two-level MUX circuit for each of the functions of Problem 1.

- 5. Obtain the circuit for the function  $f(X,Y,Z,U,V) = \sum m(0,1,6,7,9,12,13,15,18,20,22,24-26,28)$  using two levels of 1-of-4 MUXs and a few assorted gates.

- 6. Use bridging to implement the following functions using X-OR gates:

- a.  $f(A,B,C,D) = \sum m(1,2,5,7,8,10,13,14)$

- b.  $f(A,B,C,D) = \sum m(2,3,6,7,9,11,12,13)$

- c.  $f(W,X,Y,Z) = \sum m(0,2,3,6-8,10,13)$

- d.  $f(W,X,Y,Z) = \Sigma m(0,6,9,10,15)$

- 7. Implement the functions of Problem 6 using ROMs.

- 8. Implement the functions of Problem 6 using PLAs.

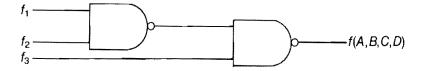

9. Given the function  $f(A,B,C,D) = \sum m(0,4,9,10,11,12)$  and  $f_1 = B \oplus D$ , determine  $f_2$  and  $f_3$  for the circuit of Figure 4.P1.

#### FIGURE 4.P1

- 10. Use a ROM to design a binary-to-Gray code converter.

- 11. Draw the logic diagram of an  $8 \times 2$  ROM that produces the full adder function as described in Chapter 1 (Table 1.4).

- 12. Use a ROM to achieve four-bit by four-bit binary multiplication.

- 13. Design a four-input network that squares each of the binary inputs using (a) a ROM, (b) a PLA, and (c) a PAL. Assume that both input and output are unsigned.

- 14. Design a five-input logic network that finds the 2's complement of a positive number using (a) a ROM, (b) a PLA, and (c) a PAL.

- 15. Design a network that accepts trigonometric angles in degrees (between 0° and 10° in steps of 1°) and gives out the corresponding tangent value correct up to five significant places. Use (a) a ROM and (b) a PLA.

- 16. Consider the truth table for the full adder of Table 1.4. Bridge the carry-out function with  $A_i \oplus B_i$ , where  $A_i$  and  $B_i$  are the augend and addend, respectively.

#### Suggested Readings

- Bartee, T. C. "Computer design of multiple output logical networks." *IRE Trans. Elect. Comp.*, vol. EC-10 (1961): 21.

- Cerny, E., and Marin, M. A. "A computer algorithm for the synthesis of memoryless logic circuits." *IEEE Trans. Comp.* vol. C-23 (1974): 455.

- Cerny, E., and Marin, M. A. "An approach to unified methodology of combinational switching circuits," *IEEE Trans. Comp.* vol. C-26 (1977): 745.

- Culliney, J. N.; Young, M. H.; Nakagawa, T.; and Muroga, S. "Results of the synthesis of optimal networks of AND and OR gates for four-variable switching functions." *IEEE Trans. Comp.* vol. C-27 (1979): 76.

- Curtis, H. A. "Short-cut method of deriving nearly optimal arrays of NAND trees." *IEEE Trans. Comp.* vol. C-28 (1979): 521.

- Davio, M. "Read-only memory implementation of discrete functions." *IEEE Trans. Comp.* vol. C-29 (1980): 931.

- Dietmeyer, D. L., and Su, Y. H. "Logic design automation of fan-in limited NAND networks." *IEEE Trans. Comp.* vol. C-18 (1969): 11.

- Ektare, A. B., and Mital, D. P. "Multiplexer logic circuit design using cubical complexes." *Elect. Lett.* vol. 16 (1980): 495.

- Ektare, A. B., and Mital, D. P., "Probabilistic approach to multiplexer logic circuit design," *Elect. Lett.* vol. 16 (1980): 686.

- Ellis, D. T. "A synthesis of combinational logic with NAND or NOR elements." *IEEE Trans. Elect. Comp.* vol. EC-14 (1965): 701.

- Fleisher, H., and Maissel, L. "An introduction to array logic." IBM J. Res. & Dev. vol. 19 (1975): 98.

- Jones, J. W. "Array logic macros." *IBM J. Res. & Dev.* vol. 19 (1975): 120. Jullien, G. A. "Residue number scaling and other operations using ROM arrays." *IEEE Trans. Comp.* vol. C-27 (1978): 325.

- Kambayashi, Y. "Logic design of programmable logic arrays." *IEEE Trans. Comp.* vol. C-28 (1979): 609.

- Lai, H. C., and Muroga, S. "Minimum parallel binary adders with NOR(NAND) gates." *IEEE Trans. Comp.* vol. C-28 (1979): 648.

- Li, H. F. "Variable selection in logic synthesis using multiplexers." *Int. J. Electron.* vol. 49 (1980): 185.

- Liu, T. K.; Hohulin, K. R.; Shiau, L. E.; and Muroga, S. "Optimal one-bit full adders with different types of gates." *IEEE Trans. Comp.* vol. C-23 (1974): 63.

- Logue, J. C.; Brickman, N. F.; Howley, F.; Jones, J. W.; and Wu, W. W. "Hardware implementation of a small system in programmable logic arrays." *IBM J. RES. & Dev.* vol. 19 (1975): 110

- Lotfi, Z. M., and Tosser, A. J. "Systematic search for minimum synthesis of logical functions with multiplexers." *Int. J. Electron.* vol. 47 (1980): 569.

- Nagle, H. T., Jr.; Carroll, B. D.; and Irwin, J. D. An Introduction to Computer Logic. Englewood Cliffs, N.J.: Prentice-Hall, 1975.

- Nakamura, K. "Synthesis of gate-minimum multi-output two-level negative gate networks." *IEEE Trans. Comp.* vol. C-28 (1979): 768.

- Papachristou, C. A. "An algorithm for optimal NAND cascade logic synthesis." *IEEE Trans. Comp.* vol. C-27 (1978): 1099.

- Peatman, J. B. Digital Hardware Design. New York: McGraw-Hill, 1980.

- Preparta, F. P. "On the design of universal Boolean functions." *IEEE Trans. Comp.* vol. C-20 (1971): 418.

- Sasao, T. "Input variable assignment and output phase optimization of PLA's." *IEEE Trans. Comp.* vol. C-33 (1984): 879.

- Sasao, T. "An algorithm to derive the complement of a binary function with multiple-valued inputs." *IEEE Trans. Comp.* vol. C-34 (1985): 131.

- Shannon, C. E. "A symbolic analysis of relay and switching circuits." Trans. AIEE. vol. 57 (1938): 713.

- Weinberger, A. "Device sharing in array logic." *IBM Tech. Disc. Bull.* vol. 19 (1976): 1357.

- Weinberger, A. "High-speed programmable logic array adders." *IBM J. Res. & Dev.* vol. 23 (1979): 163.

- Whitehead, D. G. "Algorithm for logic circuit synthesis by using multiplexers." *Elect. Lett.* vol. 13 (1977): 355.

- Wood, R. "A high density programmable logic array chip." *IEEE Trans. Comp.* vol. C-28 (1979): 602.

# Design of Combinational Circuits

CHAPTER FIVE

#### 5.1 Introduction

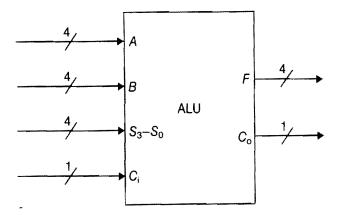

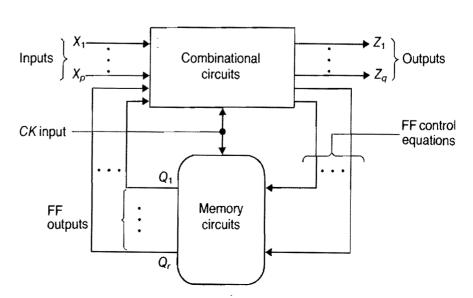

A combinational logic circuit, as shown by the block diagram of Figure 5.1, is defined as a combination of logic devices whose output is a function of the present values of the input variables and independent of the past values. After propagation time through the circuit, input variable changes cause output changes that are dependent only on the present input values.

FIGURE 5.1 Block Diagram of a Combinational Network.

In Chapters 1, 2, and 4 we introduced the necessary tools to design combinational logic circuits. The design algorithm leading to the realization of a complex combinational circuit consists of the following essential steps:

- 1. The complex logic problem is intuitively analyzed and decomposed into a set of smaller but nontrivial functional units.

- 2. The number and characteristics of both input and output variables for each of the functional units are identified.

- 3. A truth table for each of the functional units is determined.

- 4. The output functions for each of the functional units are simplified using one of the minimization schemes covered in previous chapters.

- 5. The circuits corresponding to each of the functional units are assembled and tested individually and then connected to form the desired complex function.

In practice, the designer would have to consider various practical limitations such as the number of logic gates, interconnections, gate inputs, fan-out, and the length of propagation delay. In the not too distant past the only option available to the designer was to assemble the entire logic circuit with a sack full of SSI chips. However, at this time we have better alternatives because many more complex logic circuits are available in IC form. The only limitation to the use of either the MSI or the LSI is that we may not be able to locate a device that exactly meets our requirements. In that event the designer must modify the standard device by externally combining it with other SSI or MSI chips.

In this chapter applications of these combinational logic design tools will be considered. The design and application of MSI devices, including adders, subtracters, decoders, encoders, and error-control logic, is presented. These devices play an important part in the development of more advanced digital systems. The application of the MSI devices considered is not governed by a set of design procedures as well defined as those procedures for individual logic gates. Experience and intuition (horse sense) become important. There is no substitute for understanding exactly what the MSI devices can do. After studying this chapter, you should be able to:

- O Break a complex design into manageable subunits;

- O Design individual subunits and be able to cascade them together;

- O Understand the working principles and design process of various combinational binary adders and/or subtracters;

- O Understand the working principles and design process of various code converters;

- O Understand the working principles and design of BCD arithmetic circuits;

- Understand the working principles and design of various decoders and encoders;

- O Understand the working principles and design of various error-correcting circuits.

### 5.2 Binary Adders

Most arithmetic operations are reducible to simple addition or subtraction processes that can be performed repetitively for more complex operations such as multiplication and division. If the addition circuit has no carry-in, the addition of the least significant bits involves only two operands, the addend and augend. The addition of the remaining bits, however, requires the carry-in from the addition of the previous column.

A multi-bit adder can be realized in various ways, each having different speed and cost characteristics. A two-level network would obviously prove to be the fastest. However, this network would require a large number of gates and gate inputs. It would be necessary to have  $2^{2n}$  NAND gates of 2n + 1 inputs and one NAND gate of  $2^{2n}$  inputs to add two *n*-bit numbers. This number of gates and inputs is quite significant for even small values of n. The alternative to this expensive design is quite straightforward. It follows directly from our observation of the algorithm of an *n*-bit add operation. Irrespective of the number of bits, the process of adding augend and addend is identical at each of the columns except at the least significant position. The design of a parallel *n*-bit addition circuit, therefore, is accomplished by designing a total of n single-bit addition circuits. In order to allow n single-bit adders to be connected together to form an *n*-bit adder, the single-bit adder stages need to be full adders (adders with three inputs). The least significant carry-in is tied to a 0, and each of the remaining carry-in inputs is tied to the carry-out of the previous single-bit addition.

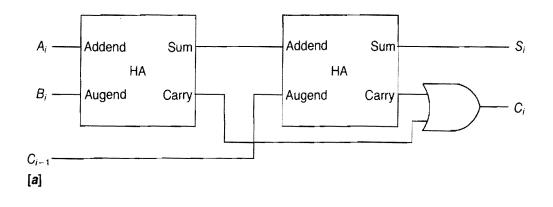

As an introduction to adder design, we shall first consider a half adder (adder with only two inputs, addend and augend). The resultant circuit will have application in the design of a full adder. In fact, an n-bit adder circuit using n-1 full adders and one half adder also can be designed.

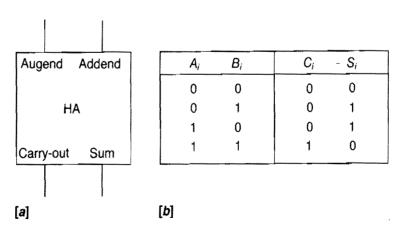

#### 5.2.1 Half Adder (HA)

The half adder (HA) unit is a simple multiple-output combinational circuit used for adding two bits without a carry-in. The truth table for the two inputs,  $A_i$  and  $B_i$ , and the output sum,  $S_i$ , and carry-out,  $C_i$ , are shown in Figure 5.2.

FIGURE 5.2 Half Adder: [a] Block Diagram and [b] Truth Table.

Using a Karnaugh map, the equations for the sum,  $S_i$ , and carry,  $C_i$ , are as follows:

$$S_i = A_i \overline{B}_i + \overline{A}_i B_i = A_i \oplus B_i$$

[5.1]

$$C_i = A_i B_i ag{5.2}$$

There are several ways to implement these functions. Figure 5.3

FIGURE 5.3 HA Circuit: [a] Using AND and X-OR Gates, [b] Using NOR Gates, [c] Using NAND Gates, and [d] Using MUXs.

illustrates four ways to implement the HA functions. Circuits using [a] an AND and an X-OR gate, [b] NOR gates, [c] NAND gates, and [d] multiplexers are shown.

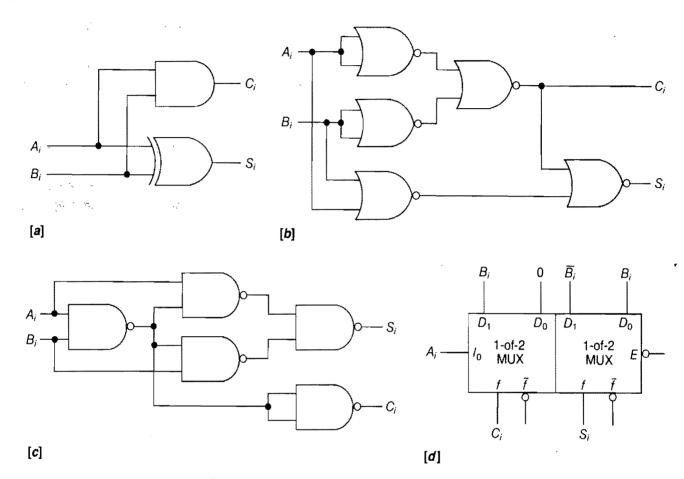

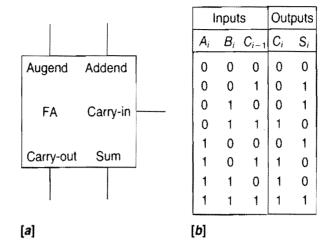

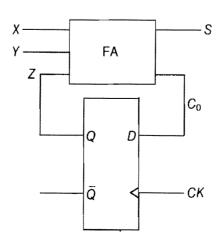

#### 5.2.2 Full Adder (FA)

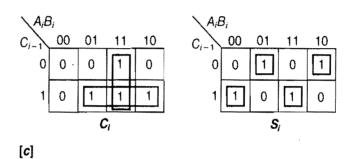

A full adder (FA) is a three-input, two-output logic circuit that adds two binary digits,  $A_i$  and  $B_i$ , and a carry-in from the i-1 bit position,  $C_{i-1}$ . The block diagram and the corresponding truth table are shown in Figures 5.4[a-b]. The K-maps for the sum bit,  $S_i$ , and the carry-out,  $C_i$ , are constructed from the truth table and shown in Figure 5.4[a]. The equations for the sum and carry-out can then be obtained from the K-maps as follows:

$$S_{i}(A_{i},B_{i},C_{i-1}) = \overline{A}_{i}\overline{B}_{i}C_{i-1} + \overline{A}_{i}B_{i}\overline{C}_{i-1} + A_{i}\overline{B}_{i}\overline{C}_{i-1} + A_{i}B_{i}C_{i-1}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1} + \overline{A}_{i} + \overline{B}_{i}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{B}_{i} + \overline{C}_{i-1} + \overline{A}_{i} + B_{i} + \overline{C}_{i-1}}$$

$$= \overline{A_{i} + \overline{A}_{i} +$$

and

$$C_{i}(A_{i},B_{i},C_{i-1}) = A_{i}B_{i} + A_{i}C_{i-1} + B_{i}C_{i-1}$$

$$= \overline{A_{i} + B_{i} + \overline{A_{i} + C_{i-1}} + \overline{B_{i} + C_{i-1}}}$$

[5.5]

FIGURE 5.4 Full Adder: [a] Block Diagram, [b] Truth Table, and [c] K-Maps for the Carry-Out and the Sum.

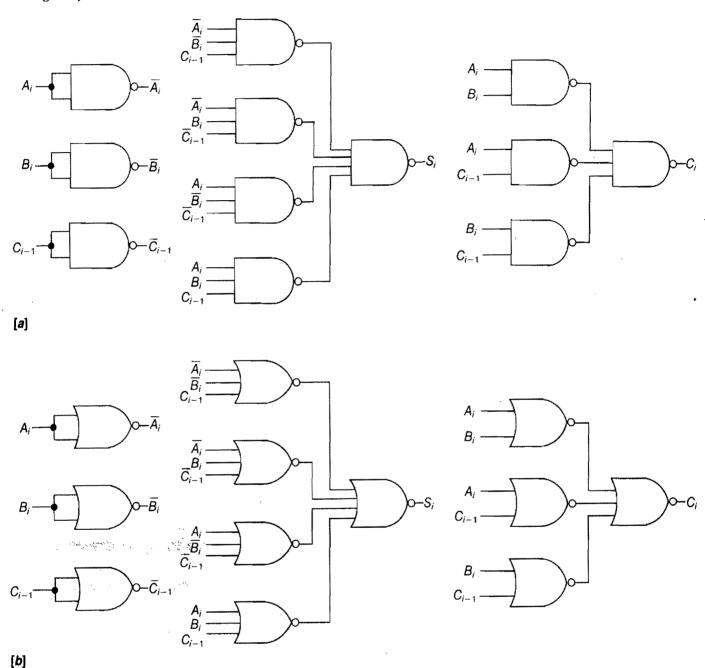

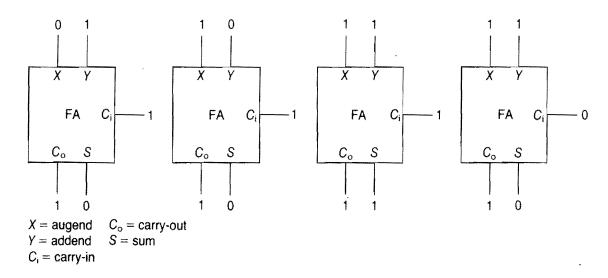

There are several ways to implement the FA equations. The direct implementation of Equations [5.3] and [5.5] leads to FA circuits using only NAND gates. If Equations [5.4] and [5.6] are used, the equivalent NOR circuits may be obtained. Figures 5.5[a-b] respectively show the typical FA circuits using only NAND and only NOR gates. Each of these circuits requires a total of 12 gates and 31 gate inputs. However, by making use of the bridging technique, the number of gates can be reduced.

Note that the K-map for the sum output is irreducible, producing a cumbersome circuit. Note also that the K-map for  $S_i$  is that of a three-input X-OR function. A review of Figure 4.36 indicates that the sum equation may be reduced to

$$S_i = A_i \oplus B_i \oplus C_{i-1} \tag{5.7}$$

Examining the carry-out K-map reveals that it could be bridged with an X-OR function as follows (see Chapter 4, Problem 16):

$$C_i = (A_i \oplus B_i)C_{i-1} + A_iB_i$$

[5.8]

Now recall that  $A_i \oplus B_i$  is the sum output and  $A_iB_i$  is the carry-

## FIGURE 5.5 FA Circuit: [a] Using Only NAND Gates and [b] Using Only NOR Gates.

out for an HA. Thus the HAs designed in the last section may be used for realizing an FA. Expressing the FA equations in terms of the HA equations, Equations [5.1] and [5.2], gives

$$S_i = S_{i(HA)} \oplus C_{i-1}$$

[5.9]

$$C_i = S_{i(HA)} \cdot C_{i-1} + C_{i(HA)}$$

[5.10]

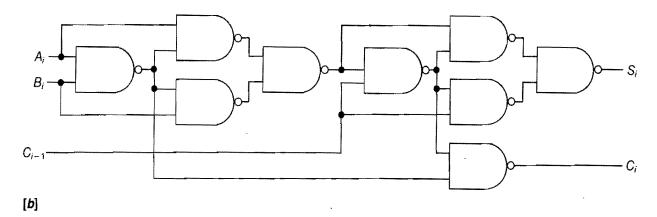

where  $S_{i(HA)}$  and  $C_{i(HA)}$  are the sum and carry-out of the HA. Note also that Equation [5.9] involves an X-OR operation between the carry-in and the HA sum. If the sum output of the HA and the carry-in are fed into a second HA, the final sum output will be the

FA sum,  $S_i$ . In addition, if the carry-outs from both of the HAs are ORed together, the FA carry-out,  $C_i$ , is obtained. Figure 5.6[a] shows the FA circuit using two HAs and an OR gate. The circuit corresponding to Equations [5.7] and [5.8] also may be implemented using only NAND gates or only NOR gates. The resultant NAND equivalent circuit is shown in Figure 5.6[b]. This NAND circuit requires only nine NAND gates and a total of 18 gate inputs. We have designed an FA circuit using three fewer gates and 13 fewer gate inputs than would be necessary had we not made use of the X-OR K-map structure and bridging.

FIGURE 5.6 FA Circuits: [a] Using HAs and [b] Using Only NAND Gates.

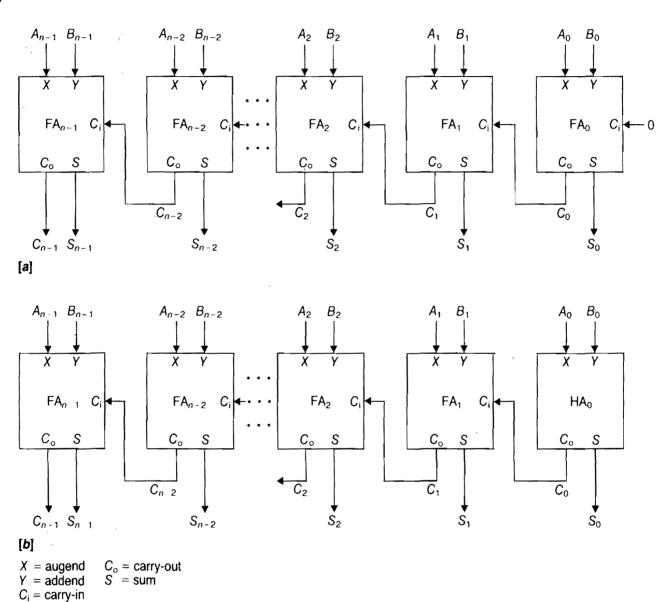

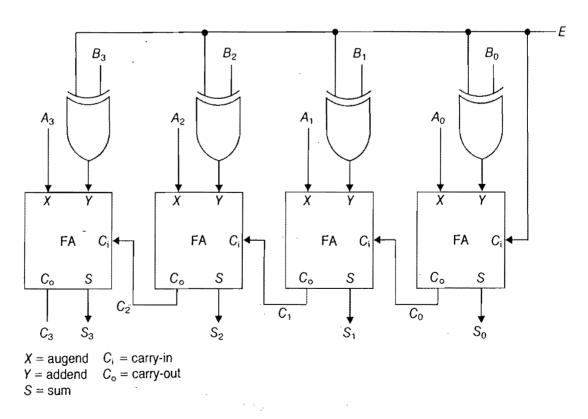

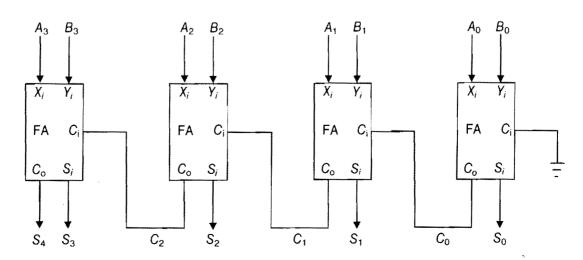

We have completed the design of half and full adders. These devices are also commercially available in the form of MSI devices. Four FAs usually are connected and are commercially available in an MSI four-bit adder IC. Using a commercially available four-bit adder, two quantities,  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$ , can be added. The resultant sum is  $S_3S_2S_1S_0$ , and the carry-out is from the  $A_3$ ,  $B_3$ , and  $C_2$  addition. Figure 5.7 demonstrates the connection of n FAs to

FIGURE 5.7 n-Bit Parallel Adder Circuit: [a] Using n FAs and [b] Using n-1 FAs and One HA.

## FIGURE 5.8 Multiplication of Two Three-Bit Numbers.

make an *n*-bit adder. The delay of this *n*-bit ripple adder is  $n\Delta$  where  $\Delta$  is the propagation delay of the carry-out of a single FA. This delay is accumulated when the carry into the multi-bit adder has to propagate through all of the FAs to get to the final carry-out. Consequently, this delay becomes more and more significant as *n* becomes larger.

Multiplication of binary numbers makes use of addition just as multiplication of decimal numbers does. The multiplication of two three-bit numbers,  $A = A_2A_1A_0$  and  $B = B_2B_1B_0$ , is symbolically obtained as shown in Figure 5.8, where  $P_5P_4P_3P_2P_1P_0$  forms the prod-

uct. Note that for the multiplication of two n-bit numbers, the product has the possibility of 2n bits.

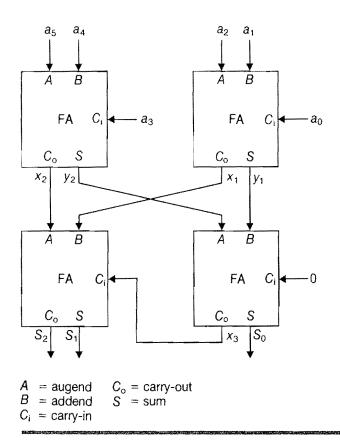

Later in the text sequential design techniques will be presented that will allow designing a multiplier that uses a repetitive algorithm for multiplication. It is possible, however, to design a combinational circuit using FAs that will perform the multiplication of two binary numbers by performing the sum of the three partial products of two numbers. This combinational circuit must be able to add columns of bits. Example 5.1 will demonstrate how FAs can be used to do similar functions.

#### EXAMPLE 5.1

#### Design a circuit using FAs that may be used for adding a column of six single-bit numbers.

#### **SOLUTION**

Let the column of numbers be  $a_0$ ,  $a_1$ ,  $a_2$ ,  $a_3$ ,  $a_4$ , and  $a_5$ . The sum if all were 1 would add up to 110, so there will be three outputs:  $S_2$ ,  $S_1$ , and  $S_0$ . However, an FA may add up to only three single bits. Two FAs may be used to obtain two partial sums of the six bits as follows:

where  $x_1$  and  $x_2$  are the carry-outs and  $y_1$  and  $y_2$  are the respective sums. As a next step the least significant bits,  $y_1$  and  $y_2$ , may be added as follows:

$$\begin{array}{ccc}

y_1 \\

y_2 \\

0 \\

\hline

x_3 & S_0

\end{array}$$

where  $x_3$  and  $S_0$  are the carry-out and the sum, respectively. Finally,  $x_1$ ,  $x_2$ , and  $x_3$  could be fed into a fourth FA to yield the carry-out,  $S_2$ , and the sum,  $S_1$ , as follows:

$$\begin{array}{c}

x_1 \\

x_2 \\

x_3 \\

\hline

S_2 \quad S_1

\end{array}$$

The complete circuit, therefore, would require four FAs. The resulting circuit is obtained as shown in Figure 5.9.

#### FIGURE 5.9

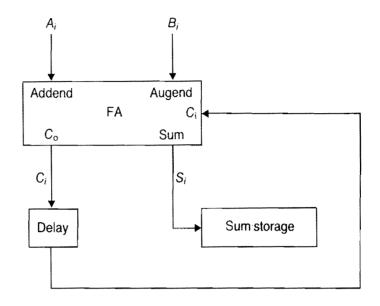

Another example of the application of adders in digital systems is given in Example 5.2. This example also demonstrates how a computer that is designed to handle binary quantities of n bits can perform operations on 2n-bit quantities. In programming, such an operation is commonly called a multiple-precision operation.

#### EXAMPLE 5.2

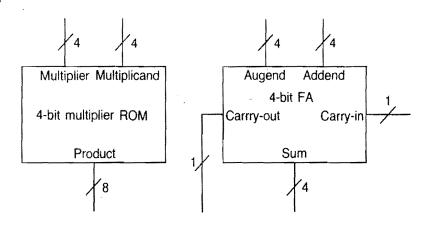

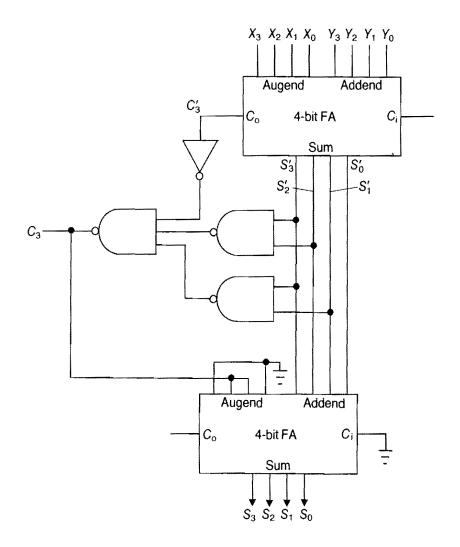

Use four-bit multipliers and four-bit FIGURE 5.10 binary adders to design a circuit for multiplying two eight-bit numbers. The block diagrams of the multiplier and adder units are provided in Figure 5.10. The fourbit multipliers are assumed to be ROMs. The two four-bit quantities to be multiplied make up an eightbit address. Each ROM storage location is the eight-bit product of the two four-bit quantities that make up its address.

#### **SOLUTION**

#### FIGURE 5.11

X = multiplier

V = addend

Y = multiplicandZ = product

W = sum

U = augend

= carry-in  $C_o = carry-out$

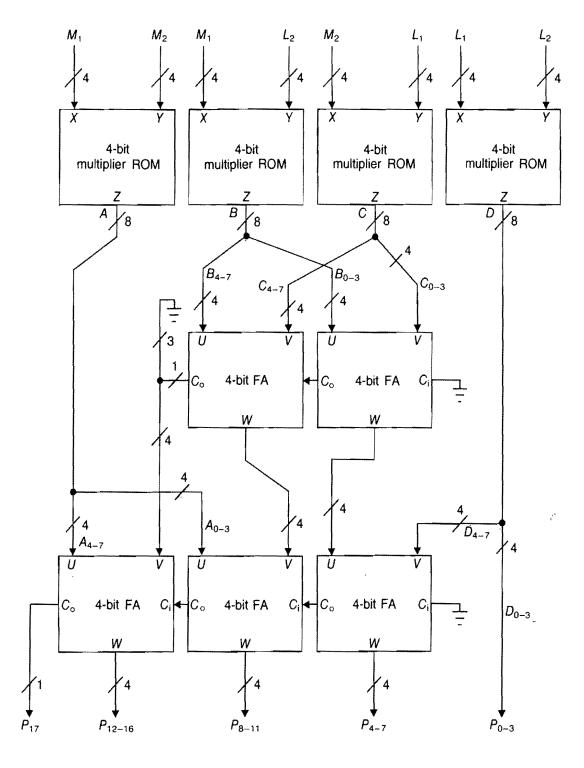

> A good approach to any design problem is to break the given problem into several simpler problems. This procedure is necessary in this example in order to make the problem fit the devices that are provided. Consider the multiplication of two eight-bit numbers,  $X_1$  and  $X_2$ , each consisting of a

least significant four bits,  $L_i$ , and a most significant four bits,  $M_i$ . The eight-bit number can then be expressed as the sum of the two four-bit parts:

$$X_i = 2^4(M_i) + L_i$$

where  $M_i$  is shifted to the left four places (multiplied by  $2^4$ ) before being added to  $L_i$ . The product, P, may now be expressed as

$$P = [2^{4}(M_{1}) + L_{1}][2^{4}(M_{2}) + L_{2}]$$

=  $2^{8}(M_{1}M_{2}) + 2^{4}(M_{1}L_{2} + M_{2}L_{1}) + (L_{1}L_{2})$

Each of these four partial products may be obtained using four four-bit multiplier units. The four multiplier units would respectively have (a)  $M_1$  and  $M_2$ , (b)  $M_1$  and  $L_2$ , (c)  $M_2$  and  $L_1$ , and (d)  $L_1$  and  $L_2$  as inputs. This configuration would result in a total of four eight-bit outputs: A, B, C, and D, respectively. Since two eight-bit quantities are being multiplied, a 16-bit product is expected. Note also that D should be added to the sum of B and C that have been shifted to the left four places, and this in turn should be added to A that have been shifted to the left eight places. A network of six four-bit FAs may be employed, as shown in Figure 5.11, to obtain the 16-bit sum of the shifted partial products. The final product is obtained by adding the partial products. Care must be taken to connect the partial products at the correct bit positions relative to their power of 2. The shifting is implicit in the interconnection pattern of the adder modules.

Note that a single ROM for multiplying two eight-bit numbers would require a total of 1,048,576 bits, that is, 16 bits of address and 16 bits in each location, to store the 16-bit product, or  $2^{16} \times 16$  bits. Each ROM that we used in this example had a size of only 2048 bits, giving a total of 8192 bits. This design would probably be less expensive but would be slower due to the time required to perform the additions. Such time and money trade-offs will be a typical design decision that must be made by every engineer.

#### 5.3 Binary Subtracters

Many arithmetic circuits also require a unit for subtraction. A subtracter circuit could be designed from scratch. However, recall from Chapter 1 that subtraction also is possible by adding the complement of the subtrahend to the minuend. Consequently, rather than designing a straightforward subtracter, a multi-bit subtracter can be made using complement arithmetic. This design would involve the use of a multi-bit parallel adder circuit that is fed with the complemented subtrahend and the minuend.

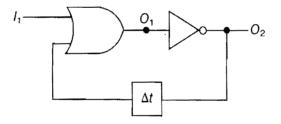

In order to accommodate the multi-bit parallel adder to the requirement of our present design, certain modification is necessary for complementing the subtrahend. If each bit of the subtrahend is individually complemented, the corresponding 1's complement will be obtained. A 2's complement could be formed by adding a one to the LSB of the corresponding 1's complement, that is, by making the carry-in to the LSB position of the adder a 1. To perform the

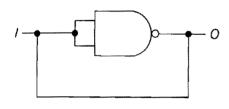

complementing of each bit, we can use an X-OR gate. An X-OR has a useful characteristic that makes it perform as a programmable inverter. Consider a two-input X-OR gate for which one input is a bit of the subtrahend and the other input is tied to a select line, E. When E=1, the output will be the complement of the subtrahend bit. When E=0, the output will be the uncomplemented bit, since from the X-OR truth table,

$$1 \oplus Y = \overline{Y}$$

$$0 \oplus Y = Y$$

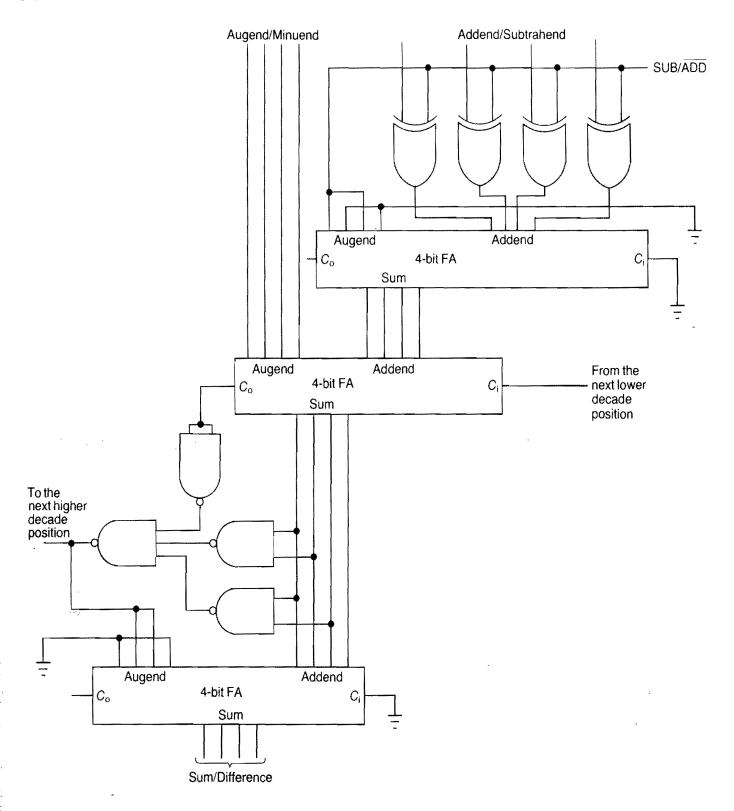

The property of an X-OR function provides the possibility of having both an adder and a subtracter out of the same circuit. Such a circuit is shown in Figure 5.12 where the enable, E, allows the circuit to add or to subtract by taking the 1's complement and adding a one to the LSB. When E=0, the circuit adds with a carry-in of 0, and when E=1, the circuit complements B and adds that to A with a carry-in of 1.

FIGURE 5.12 Four-Bit Adder/ Subtracter Unit.

#### EXAMPLE 5.3

#### **SOLUTION**

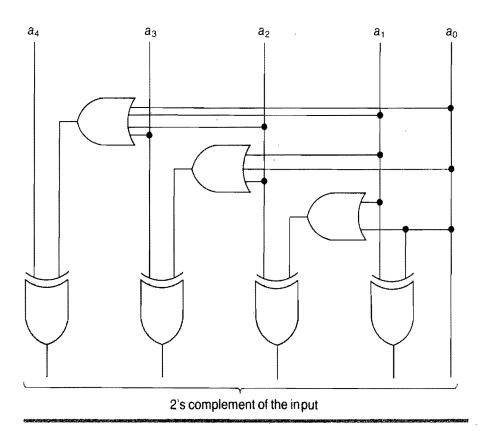

Obtain a combinational circuit for realizing the 2's complement of a five-bit binary number.

From Section 1.4 we know that the LSB of a number always remains unchanged when obtaining the 2's complement. If the LSB,  $a_0$ , is 1, then the next higher bit,  $a_1$ , is inverted. An X-OR gate in the form of  $a_0 \oplus a_1$

may be used to accomplish this. The next higher bit,  $a_2$ , is complemented if either  $a_1$  or  $a_0$  is 1. This line of argument could be carried out for all of the remaining bits. Such logical tests can be implemented by performing  $a_0 + a_1 + \cdots + a_{m-1}$ , which would indicate whether or not a 1 is present in the least significant m bits.

It is apparent, therefore, that X-OR and OR gates can be used to realize the necessary circuit for performing 2's complement of a number. The OR gates would perform tests and the X-OR gates would complement bits if necessary. The resulting circuit for a five-bit number  $a_4a_3a_2a_1a_0$  is obtained as shown in Figure 5.13.

FIGURE 5.13

いいとう でんしいとういうかんとうことを変してはなるのではなるのでは、

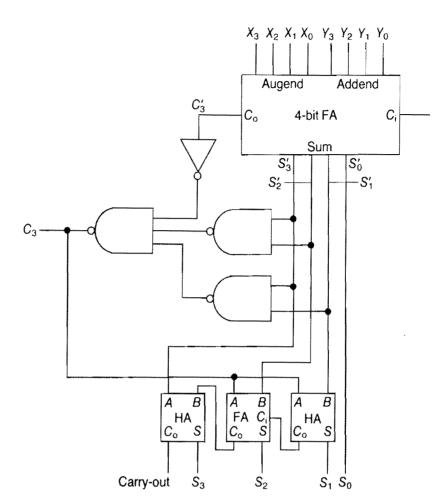

# 5.4 Carry Look-Ahead (CLA) Adders

The particular multi-bit parallel adder circuit developed in the previous section is sometimes referred to as a *ripple adder* because a carry from one unit of the adder may have to ripple through several units before the sum is obtained. Such ripple adders have also been used to form either 2's complement, or 1's complement sign-and-magnitude binary adder/subtracters. The performance of a ripple adder/subtracter, however, is limited by the time required for the carries to ripple through all of the stages of the circuit. For such devices the maximum delay is directly proportional to the number of FA units.

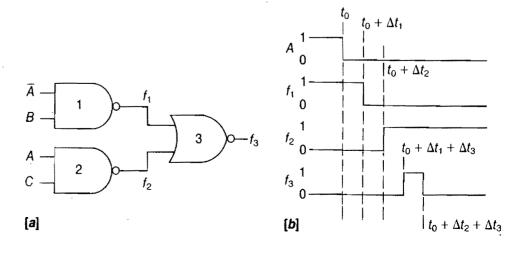

One particular method of speeding up the combinational addition process is known as *carry look-ahead (CLA)*. In Figure 5.14 it may be seen that the carry-out is the same as the carry-in as long as one

## FIGURE 5.14 FA Configurations Resulting in a Carry-Out.

of the other two inputs is a 1. Also, the carry-out is always a 1 independent of the carry-in when both of the other inputs are 1s, and 0 if both are 0. Consequently, two useful functions can be defined: the carry-propagate,  $P_i$ , and the carry-generate,  $G_i$

$$P_i = A_i \oplus B_i \tag{5.11}$$

$$G_i = A_i \cdot B_i \tag{5.12}$$

where  $A_i$  and  $B_i$  are the addend and augend, respectively, of the *i*th full adder.

The FA equations, Equations [5.7] and [5.8], can then be rewritten as

$$S_i = P_i \oplus C_{i-1} \tag{5.13}$$

$$C_i = G_i + P_i C_{i-1} ag{5.14}$$

For a four-bit adder the carries for the various stages are as follows:

$$C_0 = G_0 + P_0 C_{-1} ag{5.15}$$

$$C_1 = G_1 + P_1 C_0$$

$$= G_1 + P_1 G_0 + P_1 P_0 C_{-1}$$

[5.16]

$$C_2 = G_2 + P_2 C_1$$

$$= G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_{-1}$$

[5.17]

and

$$C_3 = G_3 + P_3C_2$$

=  $G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0 + P_3P_2P_1P_0C_{-1}$  [5.18]

while the sum bits are

$$S_0 = P_0 \oplus C_{-1} \tag{5.19}$$

$$S_1 = P_1 \oplus C_0 \tag{5.20}$$

$$S_2 = P_2 \oplus C_1 \tag{5.21}$$

and

$$S_3 = P_3 \oplus C_2 \tag{5.22}$$

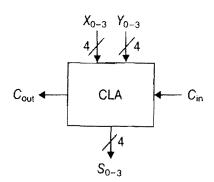

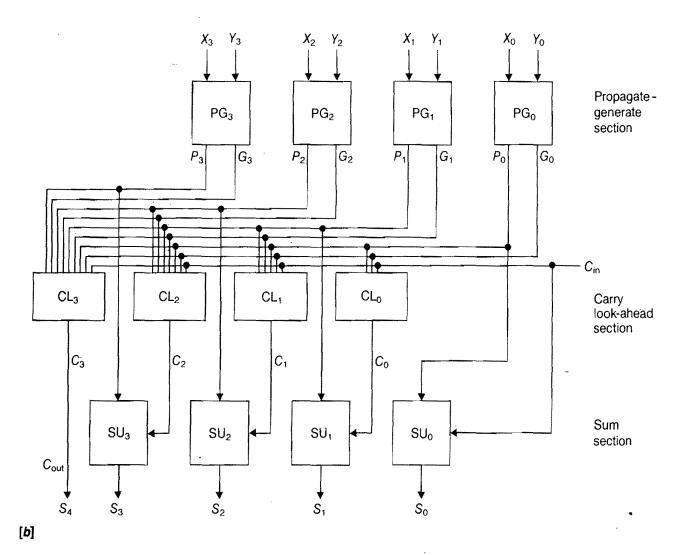

In Equations [5.15–18] the carry-out for each of the stages is dependent only on the initial carry,  $C_{-1}$ , and the corresponding propagate and generate functions. The equation for  $C_3$  can be implemented with a two-gate level circuit. Since each of the generate and propagate functions can be expressed in terms of the two data bits,  $C_3$  is available after two gate delays, resulting in a fast addition process. The block diagram of a four-bit CLA adder is shown in Figure 5.15. It consists of three sections, each having four subunits. The  $PG_i$  section generates the carry-propagate and carry-generate functions. The  $CL_i$  section intakes the outputs of the previous section and generates the carries. Finally, the  $SU_i$  section generates the sum bits. However, the carry units are different for every bit, and their complexity increases as they move further away from the LSB.

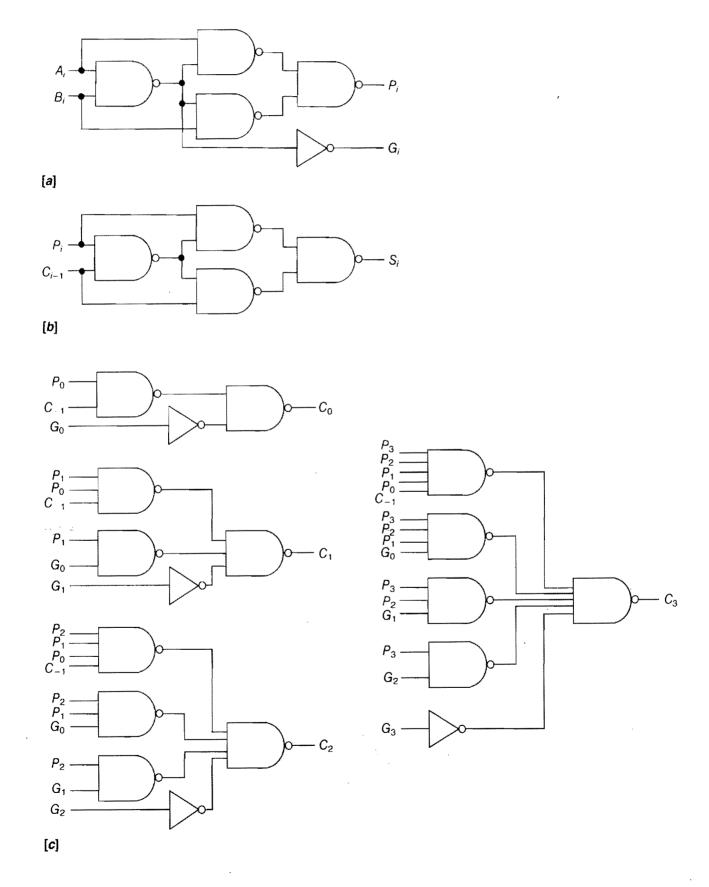

The internal hardware for the four-bit CLA adder is shown in Figure 5.16. Each propagation-generation unit requires five NAND gates, each sum unit requires four NAND gates, and the n-bit carry section requires a total of  $(n^2 + 5n)/2$  NAND gates. A four-bit CLA adder, therefore, requires a total of 54 NAND gates and involves a total of eight units of gate delay. In comparison, addition in a four-bit ripple adder requires 12 units of gate delay. The four-bit CLA, therefore, cuts down the time factor by about one-third. Similarly, a 64-bit CLA adder requires almost five times as many NAND gates as a 64-bit ripple adder, but reduces the propagation delay by a factor of 17. It follows, therefore, that the CLA adder will provide a faster addition time, especially when the number of bits is higher.

An inventory of the *n*-bit CLA adder reveals that the sum and the carry subunits require a total of 9n two-input NAND gates. The carry section, however, requires (2n + 1) two-input NAND gates and (n + 3 - m) *m*-input NAND gates for  $3 \le m \le n + 1$ . Therefore, from a practical standpoint CLA for too large n turns out to be quite problematic. It was seen in Chapter 3 that NAND gates with too many inputs are hard to come by. This limitation is compounded by the fact that the carry-in,  $C_{-1}$ , must drive a total of n + 1 gates. In addition, the propagate functions will be subjected to a fan-out requirement on the order of  $(n + 1)^2/4$ . All of these together result in a serious fan-in problem for n too large.

FIGURE 5.15 Four-Bit CLA Adder: [a] Block Diagram and [b] Internal Circuitry.

[a]

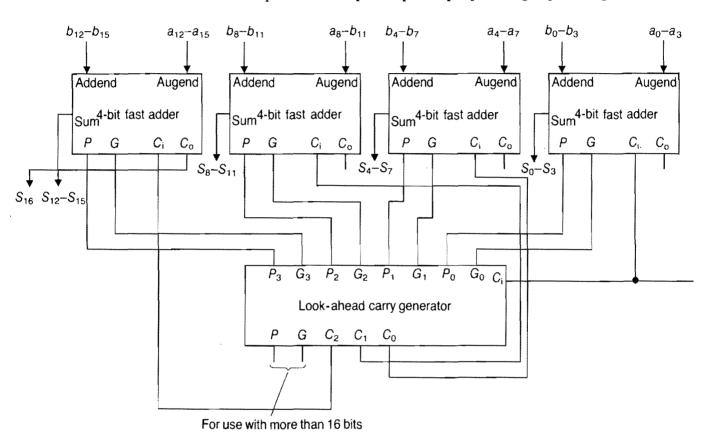

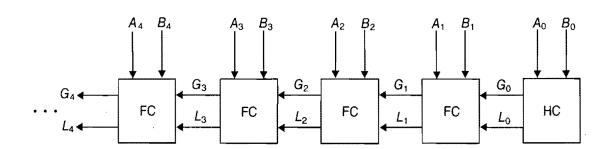

Commercially available four-bit adders perform an internal CLA for a four-bit add. These outputs are available and labeled as P for propagate and G for generate. These outputs when used with another MSI device called a *look-ahead carry generator* provide significant acceleration in the add operation, particularly for large num-

FIGURE 5.16 [a] Single Propagation-Generation Unit, [b] Single Sum Unit, and [c] Carry Units of a Four-Bit CLA Adder.

bers of bits. Figure 5.17 shows the connections for performing the addition of two 16-bit numbers with CLA.

Carry-propagate and carry-generate functions for more than four bits can be derived continuing the same process used for deriving  $C_3$  and  $S_3$ . Circuit complexity makes such implementation impractical except for special-purpose, high-speed requirements.

FIGURE 5.17 16-Bit Addition with CLA Modules.

#### EXAMPLE 5.4

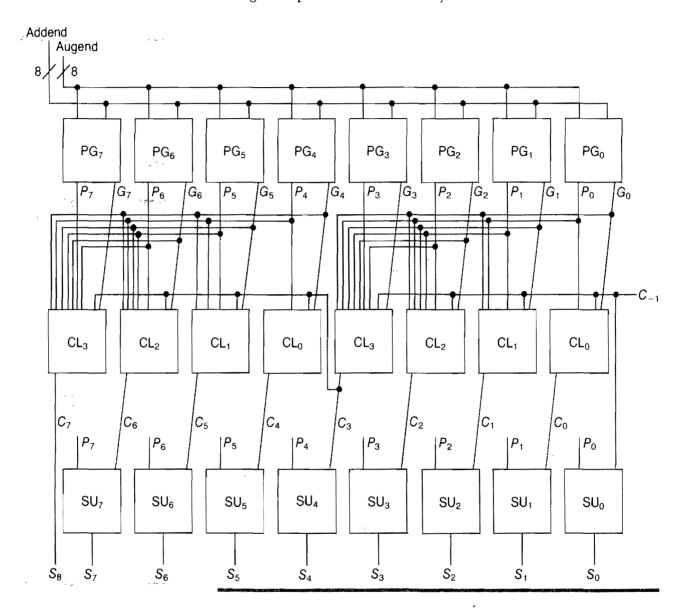

Design an eight-bit fast adder where the fan-in and fan-out problems are avoided by allowing the carries to ripple through after the addition of every four bits.

#### **SOLUTION**

The modified carry equations for an eight-bit fast adder are derived as follows:

$$C_0 = G_0 + C_{-1}P_0$$

$$C_1 = G_1 + G_0P_1 + C_{-1}P_0P_1$$

$$C_2 = G_2 + G_1P_2 + G_0P_1P_2 + C_{-1}P_0P_1P_2$$

$$C_3 = G_3 + G_2P_3 + G_1P_2P_3 + G_0P_1P_2P_3 + C_{-1}P_0P_1P_2P_3$$

$$C_4 = G_4 + G_3P_4$$

$$C_5 = G_5 + G_4P_5 + C_3P_4P_5$$

$$C_6 = G_6 + G_5P_6 + G_4P_5P_6 + C_3P_4P_5P_6$$

$$C_7 = G_7 + G_6P_7 + G_5P_6P_7 + G_4P_5P_6P_7 + C_3P_4P_5P_6P_7$$

The first four equations are similar to Equations [5.15–18]. The last four equations have a similar form, but  $C_3$  is treated as the carry-in to the fifth bit. The resultant circuit may now be obtained, as shown in Figure 5.18, by having two separate units for the carry section.

**FIGURE 5.18**

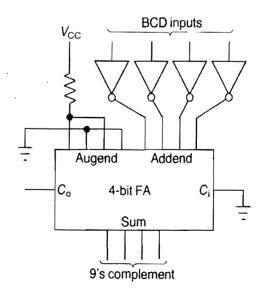

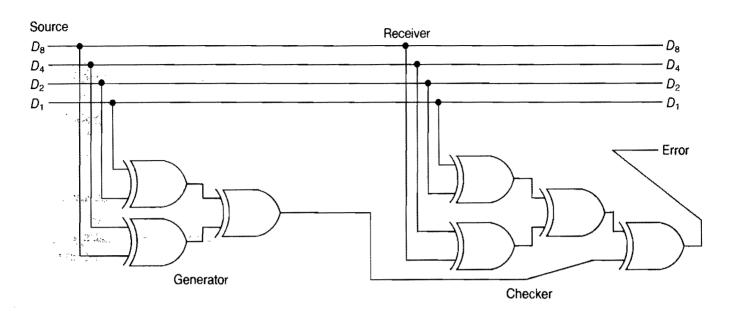

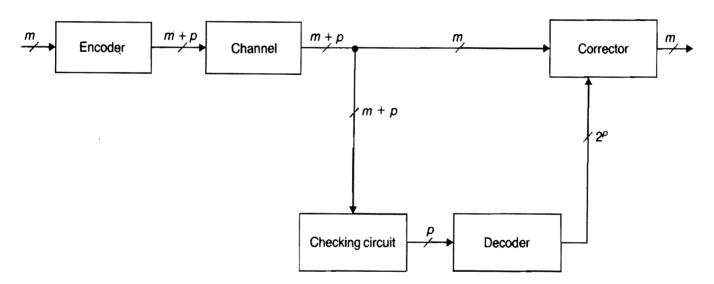

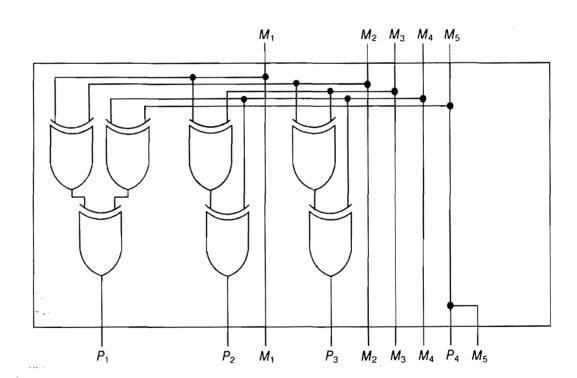

#### 5.5 Code Converters

It was pointed out in Chapter 1 that many different binary codes exist that are used in various digital subsystems. Sometimes it is necessary to transfer data from one subsystem to another. *Code converter circuits* are required to convert one form of binary code to another. Many of these converters use combinational logic, and there are many that use sequential logic as well.

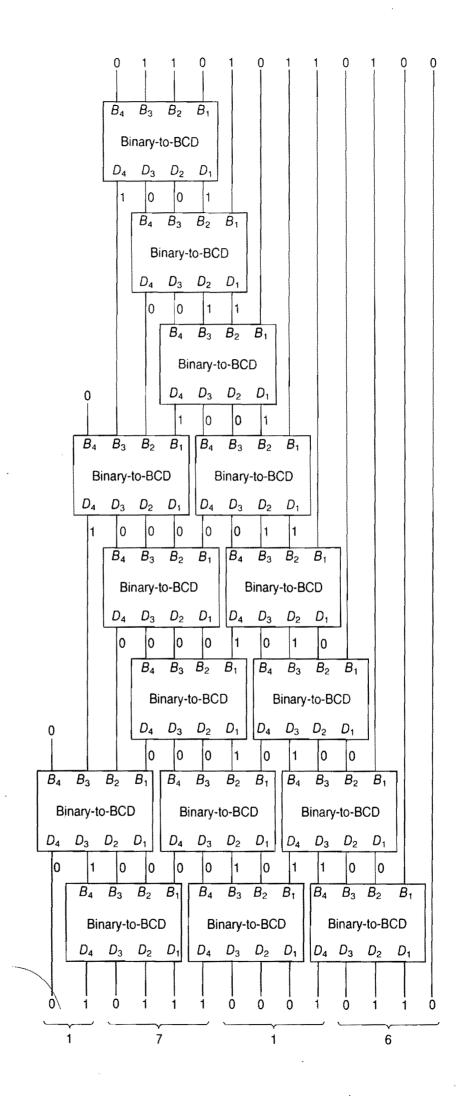

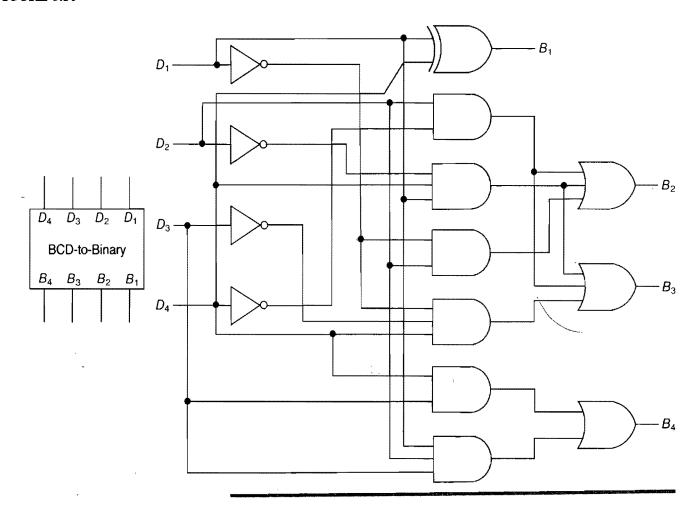

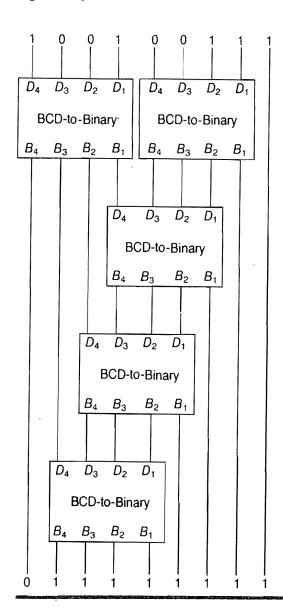

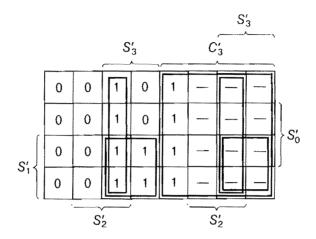

The following examples will illustrate the combinational techniques in the design of various code converters. We shall consider several conversion schemes: Gray-to-binary, binary-to-Gray, binary-to-BCD, and BCD-to-binary.

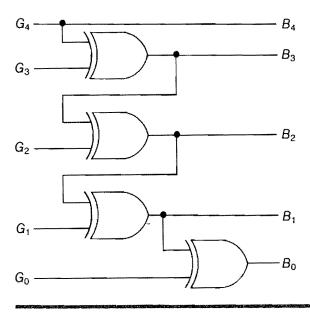

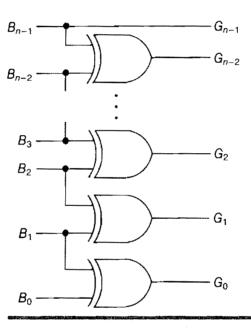

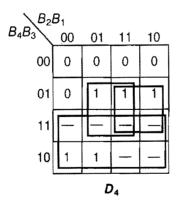

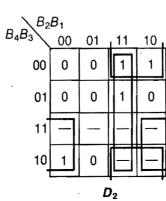

#### EXAMPLE 5.5

#### **SOLUTION**

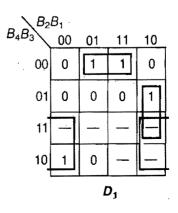

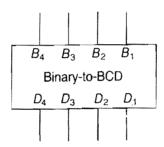

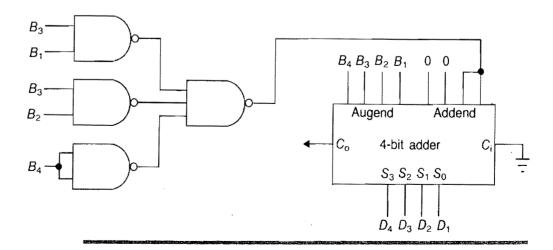

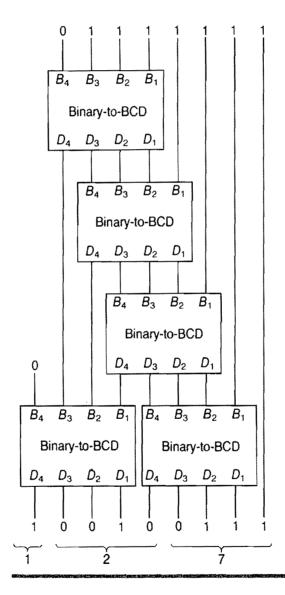

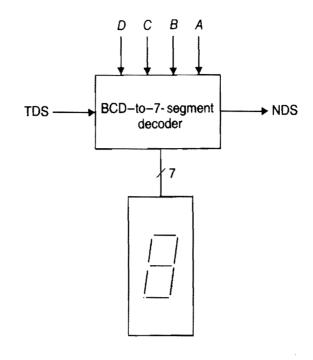

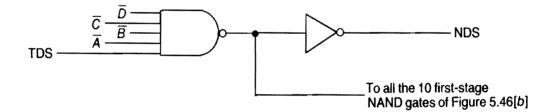

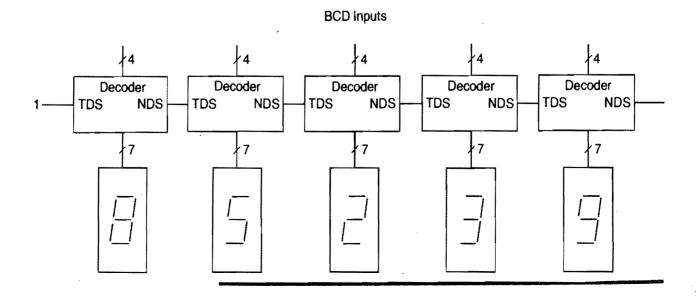

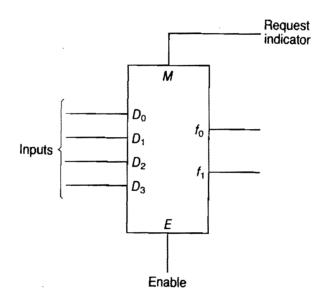

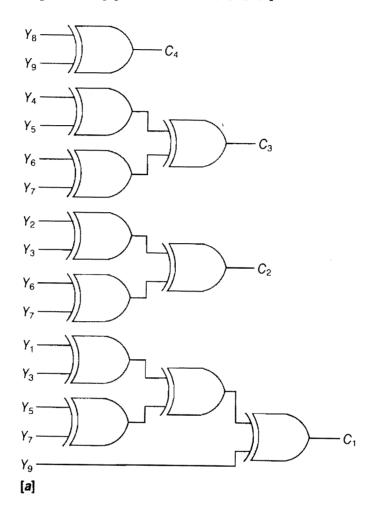

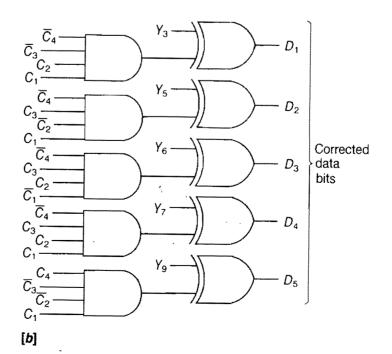

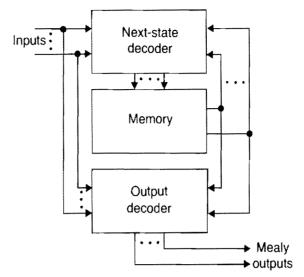

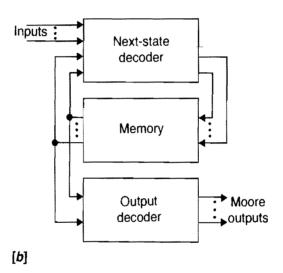

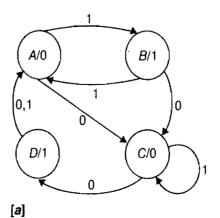

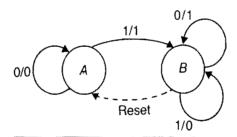

Design a circuit for converting a five-bit Gray code into its binary equivalent.